Abstract

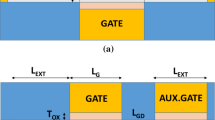

For the first time in this study a junctionless field effect diode (JL-FED) is proposed and investigated using 2D simulations. In this structure, the advantages of junctionless field effect transistor (JL-FET) and FED are combined together. Unlike a FED, a JL-FED device can be turned on without applied biases to the control gates. JL-FED device with channel lengths less than 15 nm could not be turned off due to the short channel effects (SCEs). We have proposed a new structure, namely modified JL-FED (MJ-FED), to reduce the issues of SCEs. All structural parameters of MJL-FED device are quite the same as the JL-FED device, except its control gates work function. Our simulation results demonstrate that OFF-state current of MJL-FED with 10 nm channel length is approximately six orders of magnitude lower than that of JL-FED. Moreover, simulation results obtained here show that the MJL-FED with 22 nm channel length exhibit ION/IOFF ratio of ~ 3 × 1014 and a subthreshold swing (SS) of ~ 78 mV/decade, which are considerably improved as compared to those of reported so far in the literature. As a result, MJL-FED is a promising candidate for a switching performance.

Similar content being viewed by others

References

F. Raissii, A brief analysis of the field effect diode and breakdown transistor. IEEE Trans. Electron. Devices 43(2), 362–365 (1996)

N. Manavizadeh, F. Raissi, E.A. Soleimani, M. Pourfath, S. Selberherr, Performance assessment of nanoscale field-effect diodes. IEEE Trans. Electron. Devices 58(8), 2378–2384 (2011)

M. Vadizadeh, M. Fathipour, G.H. Darvish, Silicon on raised insulator field effect diode (SORI-FED) for alleviating scaling problem in fed. Int. J. Mod. Phys. B 28(5), 1450038 (2014)

M. Vadizadeh, Improving gate delay and I ON/IOFF in nanoscale heterostructure field effect diode (H-FED) by using heavy doped layers in the channel. Appl. Phys. A 122(4), 469 (2016)

M. Vadizadeh, Dual material gate nanowire field effect diode (DMG-NWFED): operating principle and properties. Microelectron. J. 71, 1–7 (2018)

A. Sotoudeh, M. Amirmazlaghani, Graphene-based field effect diode. Superlat Microstruct 120, 828–836 (2018)

B.J. Touchaei, M. Negin, Impact of scaling voltage and size on the performance of side-contacted field effect diode. Superlatt Microstruct 117, 406–412 (2018)

A.Z. Badwan, Z. Chbili, Y. Yang, A.A. Salman, Q. Li, D.E. Ioannou, SOI field-effect diode DRAM cell: design and operation. IEEE Electron. Device Lett. 34(8), 1002–1004 (2013)

A.Z. Badwan, Z. Chbili, Q. Li, D.E. Ioannou, SOI FED-SRAM cell: structure and operation. IEEE Trans. Electron. Devices 62(9), 2865–2870 (2015)

I. Sheikhian, F. Raissi, High-speed digital family using field effect diode. Electron. Lett. 39(4), 345–347 (2003)

J.P. Colinge, C.W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O’neill, A. Blake, M. White, A.M. Kelleher, Nanowire transistors without junctions. Nat. Nanotechnol. 5(3), 225 (2010)

T. Rudenko, A. Nazarov, R. Yu, S. Barraud, K. Cherkaoui, P. Razavi, G. Fagas, Electron mobility in heavily doped junctionless nanowire SOI MOSFETs. Microelectron. Eng. 109, 326–329 (2013)

N. Dehdashti Akhavan, I. Ferain, P. Razavi, R. Yu, J.P. Colinge, Improvement of carrier ballisticity in junctionless nanowire transistors. Appl. Phys. Lett. 98(10), 103510 (2011)

M. Vadizadeh, Designing a hetrostructure junctionless-field effect transistor (HJL-FET) for high-speed applications. J. Korean Phys. Soc. 71(5), 275–282 (2017)

M. Vadizadeh, Characteristics of GaAs/GaSb tunnel field-effect transistors without doping junctions: numerical studies. J. Comput. Electron. 17(2), 745–755 (2018)

P.K. Asthana, B. Ghosh, Y. Goswami, B.M. Tripathi, High-speed and low-power ultradeep-submicrometer III–V heterojunctionless tunnel field-effect transistor. IEEE Trans. Electron. Devices 61, 479–486 (2014)

S. Ramaswamy, Mamidala JK (2014) Junctionless impact ionization MOS: proposal and investigation. IEEE Trans. Electron. Devices. 61(12), 4295–4298 (2014)

P. Ranade, H. Takeuchi, T.J. King, C. Hu, Work function engineering of molybdenum gate electrodes by nitrogen implantation. Electrochem. Solid State Lett. 4(11), G85–G87 (2001)

J.M. Sallese, F. Jazaeri, L. Barbut, N. Chevillon, C. Lallement, A common core model for junctionless nanowires and symmetric double-gate FETs. IEEE Trans. Electron. Devices 60(12), 4277–4280 (2013)

H. Tsuchiya, A. Svizhenko, M.P. Anantram, M. Ogawa, T. Miyoshi, Comparison of non-equilibrium Green’s function and quantum-corrected Monte Carlo approaches in nano MOS simulation. J. Comput. Electron. 4(1–2), 35–38 (2005)

M. Luisier, A. Schenk, W. Fichtner, Quantum transport in two-and three-dimensional nanoscale transistors: coupled mode effects in the nonequilibrium Green’s function formalism. J. Appl. Phys. 100(4), 043713 (2006)

O. Kurniawan, P. Bai, E. Li, Ballistic calculation of nonequilibrium Green’s function in nanoscale devices using finite element method. J. Phys. D Appl. Phys. 42(10), 105109 (2009)

ATLAS User’s Manual, Device simulation software (Silvaco International, Santa Clara, 2014)

M. Gupta, Ballistic MOSFETs, the ultra-scaled transistors. IEEE Potent. 21(5), 13–16 (2002)

H-E, Jung, S. Mincheol, Surface-roughness-limited mean free path in Si nanowire FETs. arXiv:1304.5597 (2013)

S. Datta, Quantum transport: atom to transistor (Cambridge University Press, Cambridge, 2005)

B.G. Streetman, S.K. Banerjee, Solid state electronic devices, global edn. (Pearson Education, London, 2016)

H. Kawaura, T. Sakamoto, T. Baba, Observation of source-to-drain direct tunneling current in 8 nm gate electrically variable shallow junction metal–oxide–semiconductor field-effect transistors. Appl. Phys. Lett. 76(25), 3810–3812 (2000)

M.P.V. Kumar, C.Y. Hu, K.H. Kao, Y.J. Lee, T.S. Chao, Impacts of the shell doping profile on the electrical characteristics of junctionless FETs. IEEE Trans. Electron. Devices 62(11), 3541–3546 (2015)

V.P.-H. Hu, C.-T. Wang, Optimization of III–V heterojunction tunnel FET with non-uniform channel thickness for performance enhancement and ambipolar leakage suppression. Jpn. J. Appl. Phys. 57(4S), 04FD18 (2018)

A.K. Bansal, M. Kumar, C. Gupta, T.B. Hook, A. Dixit, Series resistance reduction with linearity assessment for vertically stacked junctionless accumulation mode nanowire FET. IEEE Trans. Electron. Devices 65(8), 3548–3554 (2018)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Vadizadeh, M. Performance estimation of junctionless field effect diode. Appl. Phys. A 125, 495 (2019). https://doi.org/10.1007/s00339-019-2788-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-019-2788-1