Abstract

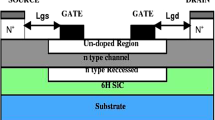

We have analyzed the operating mechanism of the novel deep submicrometer SOI drive-in gate controlled hybrid transistor (DGCHT), which can effectively alleviate the contradiction between speed enhancement and power reduction in conventional MOS devices and can improve the output resistance. On the basis of this, the subthreshold current model of DGCHTs is proposed. The model takes into account the impact of lateral non-uniform doping profile on body effect, short-channel effect and carrier mobility. Considering the mobile charge, two-dimensional Poisson equation is solved with quasi-two-dimensional analysis and parabolic approximation of surface potential. With the surface potential obtained, the subthreshold current is figured out, including both the diffusion and drift component. The calculated results are in good agreement with the MEDICI numerical simulation results, indicating the correct description of the current characteristics of SOI DGCHT by the presented model. The model can also be considered as an important reference to the current simulation of deep submicrometer MOSFET with pocket implantation.

Similar content being viewed by others

References

Colinge, J. P., A SOI voltage-controlled bipolar-MOS device, IEEE Trans. Electron Devices, 1987, 34: 845.

Parke, S. A., Hu, C., Ko, P. K., Bipolar-FET hybrid-mode operation of quarter-micrometer SOI MOSFET’s, IEEE Electron Device Lett., 1993, EDL14: 234.

Assaderaghi, F., Sinitsky, D., Parke, S. A. et al., Dynamic threshold-voltage MOSFET(DTMOS) for ultra-low voltage VLSI, IEEE Trans. Electron Devices, 1997, 4D41: 414.

Huang, R., Wang, Y. Y., Comprehensive analysis of the short channel effect in SOI gate controlled hybrid transistor, International Journal of Electronics, 1999, 86: 685.

Hirota, T., Ueda, K., 0.5V 320MHz multiplexer/demultiplexer chips based on a gate array with regular-structured DTMOS/SOI, International Solid-State Circuits Conference, U.S.A., 1998.

Yan, Z., Deen, M. J., Malhi, D. S., Gate-controlled lateral PNP BJT: characteristics, modeling and circuit applications, IEEE Trans. Electron Devices, 1997, 44: 118.

Huang, R., Zhang, X., Wang, Y. Y., A high-performance SOI drive-in gate controlled hybrid transistor with annealing (DGCHT), IEEE Trans. Electron Devices, 1998, 45: 2079.

Shahidi, G. G., CMOS scaling in the 0.1-µ, 1.x-volt regime for high performance applications, IBM J. RES. Develop, 1995, 39(1/2): 229.

Hong, M. Y., Simulation and fabrication of submicron channel length DMOS transistors for analog applications, IEEE Trans. Electron Devices, 1993, 40(12): 2222.

Liu, C. M., Lou, K. H., Kuo, J. B., 77K versus 300K operation: the quasi-saturation behavior of a DMOS device and its fully analytical model, IEEE Trans. Electron Devices, 1993, 40(9): 1636.

Lin, H. C., Jones, W. N., Computer analysis of the double-diffused MOS transistor for integrated circuits, IEEE Trans. Electron Devices, 1973, 20(3): 275.

Rodgers, T. J., Asai, S., Pocha, M. D. et al., An experimental and theoretical analysis of double-diffused MOS transistors, IEEE Journal of Solid-State Circuits, 1975, SC-10(5): 322.

Lin, P. S., Wu, C. Y., A new simplified two-dimensional model for the threshold voltage of MOSFET’s with nonuniformly doped substrate, IEEE Trans. Electron Devices, 1991, 38(6): 1376.

Maa, J. J., Wu, C. Y., A new simplified threshold-voltage model for n-MOSFET’s with nonuniformly doped substrate and its application to MOSFET’s miniaturization, IEEE Trans. Electron Devices, 1995, 42(8): 1487.

Lopez-Villanueva, J. A., Gamiz, F., Roldan, J. B. et al., Study of the effects of a stepped doping profile in short-channel MOSFET’s, IEEE Trans. Electron Devices, 1997, 44(9): 1425.

Huang, T. H., Chen, M. J., Empirical modeling for gate-controlled collector current of lateral bipolar transistor in an n-MOSFET structure, Solid State Electronics, 1995, 38: 115.

Joardar, K., An improved analytical model for collector currents in lateral bipolar transistors, IEEE Trans. Electron Devices, 1994, 41: 372.

Huang, R., Wang, Y. Y., Han, R. Q., Analytical model for collector current in SOI gate controlled hybrid transistor, Solid State Electronics, 1996, 39: 1816.

McKinnon, W. R., Ferguson, R., McAlister, S. P., A model for gated-lateral BJT’s based on standard MOSFET models, 1999, IEEE Trans. Electron Devices, 1999, 46(2): 427.

Huang, R., Han, R. H., Wang, Y. Y., Modeling for the subthreshold current in SOI short channel gate controlled hybrid transistor, in Proceedings 1998 IEEE Hong Kong Electron Devices Meeting, Hong Kong, Aug. 30, 1998, 118–121.

Hsiao, T. C., Subthreshold characteristics of fully depleted submicron SOI MOSFETs, IEEE Trans. Electron Devices, 1995, 42: 1120.

Poole, D. R., Kwong, D. L., Analytical modeling of the subthreshold current in short channel MOSFET’s, IEEE Electron Devices Let., 1986, EDL7: 340.

Liu, Z. H., Hu, C., Huang, J. H. et al., Threshold voltage model for deep-submicrometer MOSFET’s, IEEE Trans. Electron Devices, 1993, 40(1): 86.

Banna, S. R., Threshold voltage model for deep-submicron fully depleted SOI MOSFET’s, IEEE Trans. Electron Devices, 1995, 42: 1949.

Terrill, K. W., Hu, C., Ko, P. K., An analytical model for the channel electric field in MOSFET’s with graded drain structures, IEEE Electron Device Letters, Nov. 1984, LEDL5(11): 440.

Arora, N. D., MOSFET Models for VLSI Circuit Simulation—Theory and Practice, New York-Vienna: Springer-Verlag, 1993.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Huang, R., Bu, W., Zhang, X. et al. Quasi-two-dimensional subthreshold current model of deep submicrometer SOI drive-in gate controlled hybrid transistors with lateral non-uniform doping profile. Sci China Ser F 44, 60–67 (2001). https://doi.org/10.1007/BF02713940

Received:

Issue Date:

DOI: https://doi.org/10.1007/BF02713940