applied, the induced torque causes the pieces to rotate out of the plane on tiny hinges and lock into place.

Chang Liu, a professor of electrical and computer engineering and director of the Micro Actuators, Sensors, and Systems Laboratory at UIUC, said, "By varying the amount of magnetic material attached to the flaps, we can control the speed at which the parts fold into position. This creates a sequential assembly process that can significantly improve the speed and efficiency of fabricating large arrays of 3D structures."

Magnetic actuation could be used to create arrays of neural probes, micro-optical devices, or miniature testing devices for integrated circuits, Liu said. The fabrication process also makes possible the development of a modular building block for the construction of a new class of integrated microsensors.

Liu has recently teamed up with UIUC entomologist and neurobiologist Fred Delcomyn to develop a microintegrated sensor that mimics the action of a hair cell. "The hair cell is a very fundamental structure consisting of a long cilia attached to a neuron," Liu said. "Nature uses this basic building block in a variety of ways to accomplish such sensing tasks as hearing, balance, and touch."

The use of microelectromechanical fabrication techniques offers opportunities for creating artificial hair cells with a size scale and frequency response comparable to their biological counterparts, Liu said. The resulting sensors could be used in many applications, including autonomous robots that more fully perceive and respond to their environment.

Liu presented this work at the NASA Nanospace 2000 meeting in January, and will present related work at the World Congress on Medical Physics and Biomedical Engineering, July 23–28 in Chicago, and at an IEEE meeting in October in Arizona.

## Reliable 1.6-nm Gate Oxides Produced

Silicon chips may reach their performance limits several years later than previous predictions, according to researchers at Lucent Technologies/Bell Labs. A limiting factor in producing increasingly smaller and faster silicon-based transistors is the transistor's insulating layer. Made of silicon dioxide, the insulating layer on chips currently averages 12 atomic layers thick. While various research groups have said that 9–10 atoms would be the thinnest insulating layer for reliable, practical silicon chips, Ashraful Alam of Lucent Technologies/Bell Labs and his colleagues have shown that the intrinsic reliability

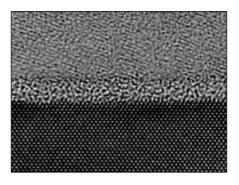

High-resolution transmission electron microscopy image showing a 1.6-nm gate oxide. (Credit: Frieder Baumann, Lucent Technologies/Bell Labs.)

limit is fewer than six atoms, or 1.5 nm. As a result, the researchers concluded that the "doomsday" scenario for the conventional silicon chip might be delayed until after 2005, instead of the next couple of years, as had been predicted.

The insulating layer, also known as the gate oxide, is the device's smallest feature. It lies between the transistor's gate electrode, which turns current flow on and off, and the channel through which this current flows. The gate oxide acts as an insulator by protecting the channel from the gate electrode, thus preventing a short circuit.

To obtain their reliability results, the researchers first studied how thicker gateoxide layers withstand high voltages over many days and developed computer models to simulate those results. They then used the same physics-based models to show that a transistor with a 1.5-nm gate oxide operating at 3 V for several hours would be comparable to a similar transistor operating at 1 V for 10 years.

As reported in April at the International Reliability Physics Symposium in San Jose, this theoretical work was confirmed by experimental work on ultrathin gate oxides. Using conventional manufacturing techniques, the research team made the ultrathin gate oxides by growing atomic layers that were exceptionally uniform and smooth (see figure). The team then tested the reliability of the transistors, verifying their theory.

## Zr-Rich Pyrochlore Stabilizes Radiation Resistance

In a collaborative effort of the University of Michigan (UM), the Pacific Northwest National Laboratory (PNNL), the Australian Nuclear Science and Technology Organisation, and the Indira Gandhi Centre for Atomic Research in India, a team of researchers has found that gadolinium zirconate (Gd<sub>2</sub>Zr<sub>2</sub>O<sub>7</sub>) resists radiation, serving as a basis for developing a very durable storage material for the safe disposal of plutonium. Lead author and UM postdoctoral fellow Shixin Wang and the research team published their results in the December 1999 issue of the *Journal of Materials Research*, and are scheduled to present their work at the Plutonium Futures 2000 Conference on July 10 in Santa Fe.

The researchers prepared pyrochlore samples from gadolinium titanate to gadolinium zirconate, varying the amounts of titanate to zirconate. When they analyzed the temperature-dependence of amorphization dose of 1 MeV Kr<sup>+</sup> irradiation on the Gd<sub>2</sub>( $Zr_xTi_{1-x}$ )<sub>2</sub>O<sub>7</sub> composition, they found an increasing resistance to radiation in response to an increase in Zr content and a decrease in temperature for amorphization. The researchers reported that for Zr-rich systems (x = 0.5), amorphization did not occur above 380 K.

High-resolution electron microscopy (HREM) observation revealed that Gd<sub>2</sub>Zr<sub>2</sub>O<sub>7</sub> transformed from a pyrochlore to a fluorite structure in response to 1 MeV Kr<sup>+</sup> irradiation, identical to stabilized cubic zirconia, thus stabilizing the composition's resistance to radiation. Previous studies attributed the stability of zirconate in part to the Zr-O bond. The transformation of Gd<sub>2</sub>Ti<sub>2</sub>O<sub>7</sub> from a crystalline structure to the fluorite structure, however, was found to be unstable relative to the amorphous state. The researchers said that regulatory requirements developed for titanate-based ceramics can be applied to the zirconatebased ceramics.

## Oxide Thin Films Fabricated with Metal Alkoxides as Oxygen Sources

By using two metal compounds in which at least one is an alkoxide, scientists in the Department of Chemistry at the University of Helsinki have discovered a way of depositing metal oxide of variable thicknesses onto silicon wafers without the formation of a SiO<sub>2</sub> interfacial layer. In metal-oxide-semiconductor field-effect transistor (MOSFET) technology, SiO<sub>2</sub> is typically a part of the gate-oxide material. In the interest of reducing device size, SiO<sub>2</sub> presents a problem because further reduction of SiO<sub>2</sub> gate-layer thickness may lead to tunneling current. Gate-oxide material with higher permittivity is desired, preferably eliminating the SiO<sub>2</sub> interlayer at the same time.

The atomic-layer deposition (ALD) method is conventionally applied to deposit a metal-oxide layer. The scientists said that a deposition cycle consists of "exposure to a metal precursor, a purge