# **Contact materials for nanoelectronics**

H.N. Alshareef, M.A. Quevedo-Lopez, and P. Majhi, **Guest Editors**

In this article, we review current research activities in contact material development for electronic and nanoelectronic devices. A fundamental issue in contact materials research is to understand and control interfacial reactions and phenomena that modify the expected device performance. These reactions have become more challenging and more difficult to control as new materials have been introduced and as device sizes have entered the deep nanoscale. To provide an overview of this field of inquiry, this issue of MRS Bulletin includes articles on gate and contact materials for Si-based devices, junction contact materials for Si-based devices, and contact materials for alternate channel substrates (Ge and III-V), nanodevices.

#### Introduction

It is well established that contact materials have a significant impact on the operation of electronic devices. In most cases, an ohmic contact, allowing unhindered current flow in and out of the device, is desired. Yet, in other cases, the contact is expected to perform a function beyond just passing current. Examples include transistor gate contacts, which determine transistor threshold voltage, and Schottky contacts, which act as rectifiers by blocking current flow in one direction. For a materials scientist, one of the key considerations in choosing contact materials is the stability of the interface between the contact material and the semiconducting film or substrate. This is because uncontrolled chemical reactions at the interface can modify the expected device performance. To realize good ohmic contacts, it is necessary to minimize the contact resistance  $(R_{co})$ between the contact and the semiconductor materials. This has become especially important as contact areas have entered the deep nanoscale ( $R_{co} = \rho_c / A_{cont}$ ), where  $A_{cont}$  is the contact area. The specific contact resistivity ( $\rho_c$ ) depends on two key parameters at the disposal of a materials scientist—doping density (N) in the semiconductor and the barrier height  $(\phi_R)$ :1

$$\rho_{\rm c} \propto \exp\left(\frac{4\pi\sqrt{\varepsilon_{\rm s}m^*}}{h}\frac{\phi_{\rm B}}{\sqrt{N}}\right),$$

(1)

where  $m^*$  is the carrier effective mass, h is Plank's constant, and  $\varepsilon_s$  is the semiconductor permittivity. The barrier height is ideally determined by the work functions of the contact/semiconductor pair. The Schottky-Mott theory provides that the barrier height,  $\phi_{\rm B}$ , is determined by the difference in the metal work function,  $\phi_{\rm m}$ , and the electron affinity of the semiconductor,  $\chi_{\rm s}$  (where  $\phi_B = \phi_m - \chi_s$ ). However, it has been observed experimentally that the barrier height is a rather weak function of  $\phi_m$ , and interfacial effects are the dominant factors that determine the value of  $\phi_B$ . Such effects have been attributed to the phenomena of Fermilevel pinning or metal-induced gap states (MIGS) theory.<sup>2,3</sup> The engineering of these interrelated parameters  $(R_{co}, N, and$  $\phi_{\rm B}$ ) is the key to getting the desired device performance and is the central theme that cuts across the different types of devices being discussed in this issue.

### **Contact materials in Si-based devices**

As Si devices have been scaled down in size, so has the contact area, resulting in increasing contact resistance. In fact, the overall contribution of contact resistance to the series resistance of metal oxide semiconductor field-effect transistors (MOSFETs) is expected to reach above 60% for the 32 nm node.<sup>4,5</sup> There are two ways to reduce the contact resistance at the silicide-Si junctions (current values are in the upper  $10^{-8} \Omega$  cm<sup>2</sup>). The first way, traditionally used, is a higher

H.N. Alshareef, King Abdullah University of Science and Technology; Husam.alshareef@kaust.edu.sa M.A. Quevedo-Lopez, University of Texas at Dallas; mquevedo@utdallas.edu P. Majhi, SEMATECH, prashant.majhi@sematech.org

DOI: 10 1557/mrs 2011 9

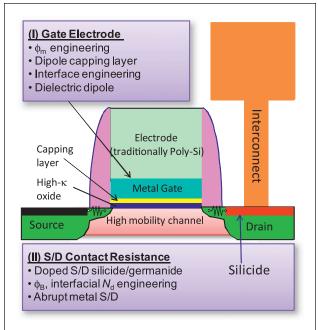

active doping concentration (N) in the junction. However, this approach is limited by the solid solubility of the dopant in Si and has basically reached the limit of its benefit. An additional method to reduce  $\rho_c$  is to lower the barrier height at the silicide-Si junction (a barrier height < 0.3 eV is needed to get  $\rho_c$  below  $1 \times 10^{-8} \Omega$  cm<sup>2</sup>). The current preferred silicide (NiSi) forms relatively large barrier heights to  $n^+$  and  $p^+$  Si of 0.67 and 0.43 eV, respectively.6 Figure 1 summarizes the multiple approaches that can be leveraged to lower junction barrier heights to reduce  $\rho_c$ . One approach is to use a smaller bandgap material such as SiGe. In fact, SiGe junctions for p-channel devices have now been in production and provide a small reduction in the barrier height to Si (in addition to strain-enhanced mobility). Another approach is to use dualsilicide junctions, shown as the black and red regions above the source and drain, respectively, in Figure 1. One silicide is optimized for  $n^+$ -Si and the other for  $p^+$ -Si. This approach has been reported using PtSi for a p-type metal oxide semiconductor (PMOS) and ErSi<sub>1.7</sub> for an *n*-type metal oxide semiconductor (NMOS) ( $\phi_n$ ,  $\phi_n = 0.22$  eV, 0.3 eV, respectively).8 Yet another method takes advantage of Fermi-level pinning using surface passivation to set the effective barrier height.9 More details on this topic are found in the article by Loh and Coss in this issue.

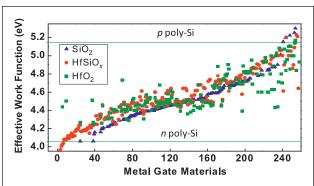

Increasingly, the introduction of new materials is driving improvements in Si transistor performance. One high profile example involving contacts is high-κ/metal gate materials.<sup>10–17</sup> Because of its lower carrier concentration compared to metals, polycrystalline silicon (poly-Si) has always exhibited a carrier depletion effect, but its impact on transistor performance became significant only as the SiO<sub>2</sub> gate dielectric thickness dropped below 2.0 nm. To eliminate the poly-Si depletion effect, metal gate materials with work functions comparable to heavily doped *n*-type silicon (4.05 eV) and *p*-type silicon (5.15 eV) were needed. The realization of these work functions using metal gates deposited directly on Hf-based dielectrics was not trivial even as hundreds of contact materials and compositions were evaluated<sup>18-21</sup> (see Figure 2). The vast majority showed some level of Fermi-level pinning, making it difficult to get the appropriate threshold voltage, especially with gate oxides approaching 1 nm equivalent oxide thickness.<sup>22-24</sup> Ultimately, two solutions emerged to overcome this issue. One was interface engineering using angstrom-level dipole interfacial layers to shift the effective work function to the desired values (4.0 and 5.0 eV for the *n*- and *p*-type silicon layers, respectively). A particularly effective oxide for NMOS was  $La_2O_3$ ,  $^{25-27}$ and for PMOS, Al<sub>2</sub>O<sub>3</sub> was effective.<sup>28</sup> The second approach was to use a lower thermal budget flow to exert better control on the interface chemistry, particularly oxygen.<sup>29,30</sup> Please see the article by Wen and Chambers in this issue for more details.

# **Electrical contacts to nanoscale devices**

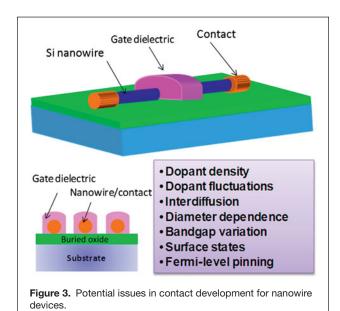

Si nanowires and carbon nanotubes (CNTs) have attracted significant attention for nanoelectronic device applications (see Figure 3).31-33 While CNTs offer exceptional mobilities, Si

Figure 1. Research directions in nanoscale complementary metal oxide semiconductor devices. These directions include junction silicide engineering, gate stack engineering, and incorporation of alternate channel materials. S/D is source/ drain,  $\phi_B$  is the barrier height,  $\phi_m$  is the metal work function, and  $N_{\rm d}$  is the doping density.

Figure 2. Effective work function of transistor gate contacts. The *x*-axis shows a large number of materials and compositions that have been tested as transistor metal gates. They include metals, conductive nitrides, silicides, oxides, and a combination of such materials.18,19

nanowires stand to benefit from the vast existing Si industry experience. The realization of Si nanowire devices, such as planar devices, will require low resistance contacts, controlled Fermi-level pinning, controlled doping levels and profiles, and appropriate barrier heights to be achieved. Two things make Si nanowire devices different from their planar counterparts: their large surface area-to-volume ratio and their exceedingly small size. Since contact resistance increases with the inverse of contact area, contact resistance can be large for nanowire devices. Further, obtaining ohmic contacts by relying on heavy doping of Si or Ge nanowires may not be a viable approach

because variation in dopant concentration of only a few atoms would significantly alter the contact resistance.<sup>34</sup> Additionally, the realization of appropriate barrier heights may be equally challenging. This is because variation in Si nanowire size may lead to fluctuation in the bandgap<sup>35-37</sup> and because interfacial phenomena such as Fermi level,  $E_{\rm F}$ , pinning and interface trap density can show dramatic differences from planar devices.<sup>38–41</sup> In fact, it has been reported that highly localized interfacial dipoles can form which, together with pinning of  $E_{\rm F}$ , can result in nanoscale Schottky barriers 40% to 90% larger than the barrier at the corresponding bulk interface.<sup>42</sup> CNTs mostly form Schottky barrier heights, and surface treatments may be needed to reduce these barriers, while Si nanowires have been demonstrated with ohmic contacts.

Another type of nanoscale device being addressed here is the nanoelectromechanical switching device. Along with the common issues of contact resistance and barrier height, these devices will present a different set of challenges. These challenges include the requirement of low stress contacts and mechanical integrity of the contact interface with the active materials, particularly for the moving parts. Please refer to the article by Hussain and Song in this issue for more details.

# Contact materials to Ge and III-V compounds

It is becoming clear that scaling of CMOS can only be realized by the continuous introduction of new materials (high-κ/metal gates, 43 SiGe-SiC, 44 Ge45/III-V channels46) and/or architectures (such as FinFET<sup>47</sup> [fin-shaped field-effect transistor] and triplegated transistors, 48 and nanowires 49). High mobility materials are strong contenders to replace Si in future generation lowpower devices. These materials provide an intrinsic mobility enhancement in excess of five times over Si and hence pose a much more stringent requirement on contact resistance (to keep the external resistance,  $R_{\text{ext}}$ , a small fraction of the total resistance). To realize the true potential of devices with Ge and/or

III–V channels, it is estimated that the contact resistivities for these systems should be below  $10^{-8}~\Omega~\text{cm}^2$ . One needs to comprehend the nanostructure of the metal-semiconductor contact and correlate this to the electrical properties of the contact. Interestingly, it has been demonstrated that most metals in contact with p-Ge have their work function pinned to the valence band of Ge, making it easier to form ohmic contacts to Ge for pFETs. However, for nFETs this Fermi-level pinning toward the valence band edge  $E_{v}$  results in a very high interfacial resistance. Some research groups have demonstrated promise in tuning this resistance by inserting a thin layer that modulates the pinning while being transparent and allowing high tunneling currents. Nevertheless, there is limited experimentally demonstrated low  $R_{co}$  for metal-Ge (n-type) contacts. For the III-V systems, there has been significant research on making low resistance contacts to an In-Ga-As semiconductor. The various approaches include the modulation of the interface to tune the Schottky barrier height and increasing the semiconductor dopant densities to 10<sup>20</sup>/cm<sup>3</sup> levels by in situ doped junctions. It has also been surmised that the higher dopant densities create an interfacial dipole that further reduces the effective Schottky barrier height of the metal/III-V contacts. Additionally, modulation of the contact resistivity using a metal-insulator-semiconductor structure is being researched with limited, but promising, results. The article by Hu et al. in this issue summarizes the current understanding of contacts to Ge and III–V semiconductors and ongoing research directions.

#### **Contact materials to thin-film transistors**

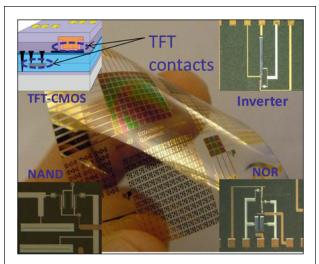

Thin-film transistors (TFTs) have become a key technology for the electronic flat panel industry in the past 15 years, just as silicon chips have been a key technology for the electronics revolution. Multiple factories today produce millions of displays per year, with each display incorporating several million TFTs. The concept of the TFT and its potential utility significantly pre-dated the device that gave rise to the term transistor. 50 However, for many years, it was overshadowed by the astounding developments associated with the original bipolar transistor and the MOSFET. In more than six decades, thin-film transistors have undergone extensive evolution, development, and optimization. During this period of time, their intended uses went from switching systems to low-cost computer logic to flat panel displays, and new materials, structures, and fabrication techniques were introduced. TFT-based CMOS devices have also been demonstrated (Figure 4).<sup>51,52</sup>

For conventional semiconductors, including single crystal and amorphous silicon, ohmic contacts are most often formed using heavily doped semiconductor regions at metalsemiconductor interfaces. However, most oxide and organic TFT devices do not use doping to help form ohmic contacts. Instead, electrodes directly contact semiconductor regions with negligible or low doping. As a result, many oxide and organic TFTs have non-ohmic contacts. In fact, many oxide and organic semiconductor TFTs operate with Schottky source contacts, where gate field-induced charge is used to provide carriers not

Figure 4. Complementary metal oxide semiconductor (CMOS) fabricated in thin-film transistor (TFT) technologies. Top left: Cross-section of the CMOS structure comprising both organic and inorganic thin-film transistors. Top right and bottom left and right: test structures.51,52

present from doping to allow tunneling between the source electrode and the TFT channel. 53 Despite the considerable progress made in recent years to improve the performance of organic and oxide TFTs, many issues are still poorly understood and poorly controlled. With decreasing device dimensions, the contact resistance as a part of the total device resistance will dominate compared with channel resistance, and therefore will play an important part in TFT operation, as well. This can be alleviated either by performing surface preparation to reduce the metal semiconductor barrier height or by increasing the effective carrier concentration of the surface, perhaps taking advantage of interface engineering.

# **Summary**

The effect of contact resistance on the performance of devices is becoming more pronounced as devices are scaled to the nanoscale. This reality will require increased ingenuity on the part of materials scientists to control interfacial reactions and to engineer the interface. Judging from the rate at which new materials and processes have entered the microelectronic and nanoelectronic industries, the prognosis for finding solutions to mitigate these issues is quite good.

### References

- 1. E.H. Rhoderick, R.H. Williams, Metal Semiconductor Contacts (Oxford University Press, Cary, NC, 1988).

- 2. R.E. Allen, Phys. Rev. B 25, 1423 (1982).

- 3. J. Tersoff, Phys. Rev. Lett. 52, 465 (1984).

- 4. S.-D. Kim, C.-M. Park, J.C.S. Woo, IEEE Trans. Electron Devices 49 (3), 467(2002).

- 5. S.D. Kim, S. Narasimha, K. Rim, IEEE IEDM Tech. Digest 149 (2005).

- 6. J.A. Kittl, K. Opsomer, C. Torregiani, C. Demeurisse, S. Mertens, D.P. Brunco, M.J.H. Van Dal, A. Lauwers, Mater. Sci. Eng. B 154 (2008).

- 7. T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, M. Bohr, IEEE IEDM Tech. Digest 978 (2003).

- 8. J. Kedzierski, P. Xuan, E.H. Andew, J. Bokor, T.-J. King, C. Hu, IEEE IEDM Tech. Digest 57 (2000).

- 9. K. Ikeda, Y. Yamashita, N. Sugiyama, N. Taoka, S. Takagi, Appl. Phys. Lett. 88 (15), 152115 (2006).

- 10. S. Ito, H. Namba, K. Yamaguchi, T. Hirata, K. Ando, S. Koyama, S. Kuroki, N. Ikezawa, T. Suzuki, T. Saitoh, T. Horiuchi, IEEE IEDM Tech. Digest 247 (2000). 11. A. Shimizu, K. Hachimin, N. Ohki, H. Ohta, M. Koguchi, Y. Nonaka, H. Sato, F. Ootsuka, IEEE IEDM Tech. Digest 433 (2001)

- 12. R. Chau, S. Datta, M. Doczy, B. Doyle, J. Kavalieros, M. Metz, IEEE Electron Device Lett. 25 (6), 408 (2004).

- 13. G. Wilk, R.M. Wallace, J.M. Anthony, J. Appl. Phys. 87, 484 (2000).

- 14. K.J. Hubbard, D.G. Schlom, J. Mater. Res. 11, 2757 (1996).

- 15. M. Houssa, Ed., High-k Dielectrics (IOP Publishing, London, 2004).

- 16. H.R. Huff, D.C. Gilmer, Eds., High-k Dielectric Constant Materials (Springer-Verlag, New York, 2005).

- 17. E.P. Gusev, D.A. Buchanan, E. Cartier, A. Kumar, D. DiMaria, S. Guha, A. Calegari, S. Zafar, P.C. Jamison, D.A. Nuemayer, M. Copel, M.A. Okorn-Schmidt, H.C. D'Emic, P. Kozlowski, K. Chan, N. Bojarczuk, L.-A. Ragnarsson, P. Ronsheim, K. Rim, R.J. Fleming, A. Mocuta, A. Ajmera, IEDM Tech. Digest 451 (2001).

- 18. H.N. Alshareef, Z. Zhang, P. Majhi, G. Brown, P. Zeitzof, H. Huff, B.H. Lee, Future Fab Int. 19, 91 (2005).

- 19. P. Majhi, H.C. Wen, H.N. Alshareef, H.R. Harris, H. Luan, K. Choi, C.S. Park, S.C. Song, B.H. Lee, R. Jammy, MICRO Mag. (May 2006).

- 20. J.A. Kittl, A. Veloso, A. Lauwers, K.G. Anil, C. Demeurisse, S. Kubicek, M. Niwa, M.J.H. van Dal, O. Richard, M.A. Pawlak, M. Jurczak, C. Vrancken, T. Chiarella, S. Brus, K. Maex, S. Biesemans, 2005 VLSI Technology Symposium (2005), p. 72. 21. J.K. Schaeffer, S.B. Samavedam, D.C. Gilmer, V. Dhandapani, P.J. Tobin, J. Mogab, B.-Y. Nguyen, B.E. White Jr., S. Dakshina-Murthy, R.S. Rai, J. Vac. Sci. Technol., B 21 (1), 11 (2003).

- 22. C. Hobbs, L. Fonseca, A. Knizhnik, V. Dhandapani, S. Samavedam, W. Taylor, J. Grant, L. Dip, D. Triyoso, R. Hegde, D. Gilmer, R. Garcia, D. Roan, L. Lovejoy, R. Rai, E. Hebert, H. Tseng, S. Anderson, B. White, P. Tobin, IEEE Trans. Electron Devices 51, 971(2004).

- 23. S.B. Samavedam, L.B. La, P.J. Tobin, B. White, C. Hobbs, L.R.C. Fonseca, A.A. Demkov, J. Schaeffer, E. Luckowski, A. Martinez, M. Raymond, W. Triyoso, D. Roan, V. Dhandapani, R. Garcia, S.G.H. Anderson, K. Moore, H.H. Tseng, C. Capasso, O. Adetutu, D.C. Gilmer, W.J. Taylor, R. Hegde, J. Grant, IEDM Tech. Digest (2003).

- 24. Y.C. Yeo, T.J. King, C. Hu, J. Appl. Phys. 92, 7266 (2002).

- 25. H.N. Alshareef, M. Quevedo-Lopez, H.C. Wen, R. Harris, P. Kirsch, P. Majhi, B.H. Lee, R. Jammy, Appl. Phys. Lett. 89, 232103 (2006).

- 26. H.N. Alshareef, H.R. Harris, H.C. Wen, C.S. Park, C. Huffman, K. Choi, H.F. Luan, P. Majhi, B.H. Lee, R. Jammy, D.J. Lichtenwalner, J.S. Jur, A.I. Kingon, VLSI Technology Symposium 10 (2006).

- 27. M. Copel, S. Guha, N. Bojarczuk, E. Cartier, V. Narayanan, V. Paruchuri, Appl. Phys. Lett. 95 (21), 212903 (2009).

- 28. H.N. Alshareef, H.F. Luan, K. Choi, H.R. Harris, H.C. Wen, M.A. Quevedo-Lopez, P. Majhi, B.H. Lee, Appl. Phys. Lett. 88, 112114 (2006).

- 29. S. Guha, V. Narayanan, Phys. Rev. Lett. 98, 196101 (2007).

- 30. K. Shiraishi, K. Yamada, K. Torii, Y. Akasaka, K. Nakajima, M. Konno, T. Chikyo, H. Kitajima, T. Arikado, Symposium on VLSI Technology (Honolulu, HI, 2004), p. 108.

- 31. W. Lu, C.M. Lieber, J. Phys. D: Appl. Phys. 39, R387 (2006)

- 32. V. Schmidt, J.V. Wittemann, S. Senz, U. Gosele, Adv. Mater. 21, 2681 (2009).

- 33. M.P. Anantram, F. Léonard, Rep. Prog. Phys. 69, 507 (2006).

- 34. T. Hanrath, B.A. Korgel, Proc. Inst. Mech. Eng. N, J. Nanoeng. Nanosystems

- 35. J. Piscator, O. Engström, Physica, Physica E 40 (7), 2508 (2008).

- 36. Mi. Nolan, S. O'Callaghan, G. Fagas, J.C. Greer, Nano Lett. 7 (1), 34 (2007).

- 37. D. Yao, G. Zhang, B. Li, Nano Lett. 8 (12), 4557 (2008).

- 38. H. Hasegawa, T. Sato, S. Kasai, Appl. Surf. Sci. 166, 96 (2000). 39. F. Leonard, A.A. Talin, *Phys. Rev. Lett.* **97** (2), 026804 (2006)

- 40. S.M. Woodruff, N.S. Dellas, B.Z. Liu, S.M. Eichfeld, T.S. Mayer, J.M. Redwing, S.E. Mohney, J. Vac. Sci. Technol., B 26, 1592 (2008)

- 41.J. Svensson, A.A. Sourab, Y. Tarakanov, D. Su. Lee, S.J. Park, S.J. Baek, Y.W. Park, E.B. Campbell, Nanotechnology. 20, 175204 (2009).

- 42. U. Landman, R.N. Barnett, A.G. Scherbakov, P. Avouris, Phys. Rev. Lett. 85, (9), 1958 (2000).

- 43. R. Chau, J. Brask, S. Datta, G. Dewey, M. Doczy, B. Doyle, J. Kavalieros, B. Jin, M. Metz, A. Majumdar, M. Radosavljevic, Microelectron. Eng. 80, 1 (2005). 44. T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, M. Bohr., IEDM Tech. Digest (2001).

- 45. H.Y. Yu, M. Ishibashi, J.-H. Park, M. Kobayashi, K.C. Saraswat, IEEE Electron Dev Lett. 30(6), 675 (2009).

- 46. J. Hu, K.C. Saraswat, H.-S. Philip Wong, J. Appl. Phys. 107, 063712 (2010).

47. J. Kedzierski, D. Fried, E.J. Nowak, T. Kanarsky, J.H. Rankin, H. Hanafi, W. Natzle, D. Boyd, IEDM Tech. Digest 437 (2001).

48. J. Kavalieros, B.S. Doyle, S. Datta, G. Dewey, R. Chau, Symposium on VLSI Technology (Honolulu, HI, 2006).

49. M. Li, K.H. Yeo, S.D. Suk, Y.Y. Yeoh, D.W. Kim, T.Y. Chung, K.S. Oh, W.S. Lee, Symposium on VLSI Technology (Honolulu, HI, 2009), p. 94.

50. J.E. Lilienfeld, U.S. Patent 1,900,018 (1933).

51. M.A. Quevedo-Lopez, S. Gowrisanker, H.N. Alshareef, B. Gnade, S. Venugopal, R. Krishna, K. Kaftanoglu, D.M. Allee, ECS Trans. 25 (7), 503 (2009). 52. S. Gowrisanker, Y. Ai, H. Jia, M.A. Quevedo-Lopez, H.N. Alshareef, B.E. Gnade, Org. Electron. 10, 1217 (2009).

53. Y. Sun, J.A. Rogers, Adv. Mater. 19, 1897 (2007).