# **NANO EXPRESS**

# **Open Access**

# Embedded Micro-detectors for EUV Exposure Control in FinFET CMOS Technology

Chien-Ping Wang<sup>1</sup>, Burn Jeng Lin<sup>2</sup>, Pin-Jiun Wu<sup>3</sup>, Jiaw-Ren Shih<sup>1</sup>, Yue-Der Chih<sup>4</sup>, Jonathan Chang<sup>4</sup>, Chrong Jung Lin<sup>1</sup> and Ya-Chin King<sup>1\*</sup>

# Abstract

An on-wafer micro-detector for in situ EUV (wavelength of 13.5 nm) detection featuring FinFET CMOS compatibility, 1 T pixel and battery-less sensing is demonstrated. Moreover, the detection results can be written in the in-pixel storage node for days, enabling off-line and non-destructive reading. The high spatial resolution micro-detectors can be used to extract the actual parameters of the incident EUV on wafers, including light intensity, exposure time and energy, key to optimization of lithographic processes in 5 nm FinFET technology and beyond.

Keywords: Extreme ultraviolet (EUV), Detectors, FinFET CMOS technologies

### Introduction

Extreme ultraviolet (EUV) is high-energy electromagnetic radiation with wavelengths from 100 to 10 nm [1], which has become a key energy source for many applications. For instance, in the field of solar science, EUV and soft X-Ray (SXR) are used in the solar physics missions at National Aeronautics and Space Administration (NASA) to observe the Sun [2]. On the other hand, EUV microscope captured images of spatial resolution in nanometer scale within a few seconds have been reported [3, 4]. Not to mention in the semiconductor industry, EUV source enables the minimization of the critical dimension (CD) and pushes forward the performance of microchips aggressively. EUV radiation with wavelength of 13.5 nm has become the standard light source in the advanced lithographic systems for integrated circuit (IC) technology nodes beyond 5 nm [5, 6].

To ensure and stabilize the control of CD, the uniformity and consistency of EUV radiation must be kept, which relies on the detecting system for in situ and in-tool EUV monitoring. Conventional silicon-based detecting

\*Correspondence: ycking@ee.nthu.edu.tw

<sup>1</sup> Institute of Electronics Engineering, National Tsing Hua University, Hsinchu, Taiwan

Full list of author information is available at the end of the article

solutions for EUV radiation use photodiodes [1], which sense EUV light directly by measuring the corresponding photocurrent. As EUV radiation is mostly absorbed within the surface layer of less than 600 nm in most materials [7, 8], extra effort must be taken to ensure good sensitivities. Hence, photodiodes with ultra-shallow junction and defect-free doping are required [1, 9], which in turn increases the complexity in manufacturing and raises barriers for integrating with other devices and circuits.

On the other hand, CMOS Image Sensor (CIS)-based methods employing Active Pixel Sensor (APS) through Backside Illuminated (BSI) technology [10, 11] are also a possible solution to obtain good Quantum Efficiency (QE) and low noise for EUV sensing. Besides CIS-based detectors, Charge-Coupled Device (CCD) is another option for obtaining high resolution and image quality [12]. Yet, all the above technologies require external power supply or batteries installed during sensing, which complicate the in situ sensing design and make them difficult to use in certain environments, for instance, high-vacuum processing chamber and submerging in liquid in emerging lithographic systems.

To meet the recent surge of interest in monitoring in situ EUV intensity distributions without external power supply, an on-wafer EUV micro-detector featuring FinFET CMOS compatibility, compact 1 T pixel structure

© The Author(s) 2022. **Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

and in-tool detection is proposed and demonstrated in this work. With this compact 1 T pixel, high spatial resolution array with pixel pitch <7  $\mu$ m can be achieved. The proposed embedded micro-detectors can not only provide high spatial resolution; the detected image can be directly written to an in-pixel storage node during exposure without power supply. The stored image can be offline non-destructive read out, providing timely feedback of on-wafer EUV radiation parameters.

#### **Methods and Operation Principle**

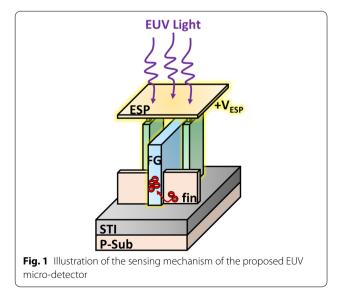

The sensing mechanism and pixel structure of the proposed micro-detector are outlined in Fig. 1. The incident EUV light with wavelength of 13.5 nm is projected on the sensing plane consisting of metal Energy Sensing Pads (ESP). Electrons on these metal ESP get excited and escape from the electrode because of the photoelectric effect, creating positive charged ESP potential  $(+V_{ESP})$ . This potential will be coupled to the in-pixel storage node, floating gate (FG) through a laterally capacitively coupling structure. When the floating gate potential  $(V_{\rm FG})$  is high enough, electron's injection occurs from finshape substrate through the thin gate-dielectric layer into FG by the Fowler–Nordheim (FN) tunneling. This then allows the EUV light intensities of each individual pixel to be written onto its corresponding FGs. The amount of FG charge  $(Q_{FG})$  depends on both the EUV intensity as well as the exposure time, while its level can be read out by off-line wafer level tests. Therefore, the on-wafer micro-detector is proposed to detect and reflect the in situ EUV signal in the advanced lithographic chamber without external power.

The detector's fabrication process is the same as a standard FinFET CMOS logic process. A brief description is a FinFET process [13–17]. First, the active region is defined by mask and forms a fin-shape substrate. Second, Sallow Trench Isolation (STI) is used to isolate the devices. Then, oxidation will be performed to form thin dielectric. Next, polysilicon is deposited and defined as gate region. And the Lightly Doped Drain (LDD) will be implanted to reduce hot carrier injection and other nonideal effects. After LDD, Spacer and Source (SL)/Drain (BL) region is formed. Then, gate material is replaced with metal (FG) for better reliability. Finally, back-end-of-line (BEOL) process is used to interconnect and construct the coupling structure of the detector (RS&ESP).

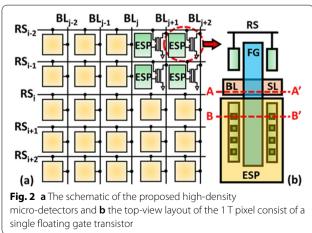

The schematic and pixel layout of micro-detectors are shown in Fig. 2a, b, respectively. A pixel is composed of one n-channel FG transistor with two coupling gates. One of the coupling gates is connected to Row-Select (RS) line, which is responsible for signal control during readout; the other coupling gate is connected to ESP, consisting of Cu-based metal for EUV sensing. The filled factor of the proposed pixel determined by the ratio of ESP area against the overall pixel area is around 30%.

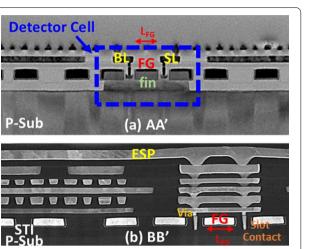

The cross section view of the pixel is shown in the Transmission Electron Microscope (TEM) image along AA' line in Fig. 3a. On the other hand, the coupling structure of RS and ESP realized by closely placed slot contacts next to FG can be further observed in the TEM image along BB' line in Fig. 3b; hence,  $V_{\text{FG}}$  is determined by the potential of RS ( $V_{\text{RS}}$ ) and  $V_{\text{ESP}}$  through these laterally coupling structure.

## **Experimental Results and Discussion** Optical Simulation and Detectors Modeling

It is known that EUV light can be absorbed by a thin layer of most materials [7, 8], which makes the EUV detector

Fig. 3 TEM image of the cross section of **a** the n-channel FG FinFET transistor and **b** the ESP with a slot-contact coupling structure, where the FG length,  $L_{FG}$  = 0.14 µm

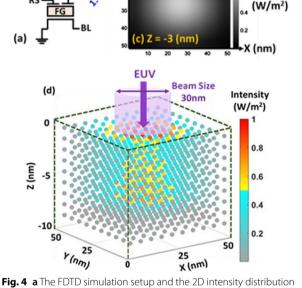

design much more challenging. Here, optical simulation by Finite-Difference Time-Domain (FDTD) is firstly used to estimate the EUV intensity profile on ESP to facilitate the pixel design. By using this simulation tool, nanoscale optical device can be precisely modeled by resolving the Maxwell's equations on a mesh in the time domain [18]. The incident EUV light intensity is set to be Gaussian distribution with standard deviation of 30 nm in space, projecting on the Copper ESP covered by native Copper oxide (CuO) of 3 nm [19], as illustrated in Fig. 4a. The FDTD optical simulation parameters of each dielectric films with film thickness < 10 nm at wavelength of 13.5 nm are summarized in Table 1. From the simulation results in Fig. 4b, c, the 2D distribution at the interface of Vacuum/CuO (Z=0 nm) and CuO/Cu (Z=-3 nm) indicates that a significant amount of incident EUV is absorbed by native CuO. Furthermore, little spread is found in the dielectric film, indicating the direct absorption of EUV light dominates, while scattering effect is limited in these oxide layer covered on ESP structures. Data show that native CuO will cause ~ 19% loss in signal, as shown in the 3D distribution in Fig. 4d.

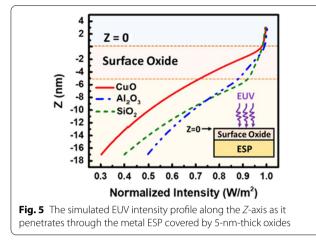

The intensity profile of depth (along the *Z*-axis) in different surface oxide and Cu-based ESP reveals that surface oxide layer can critically affect the EUV signal reaching ESP, as shown in Fig. 5. It is found that CuO can significantly block EUV light with even a thickness less than 5 nm.

Here, the impact of native aluminum oxide  $(Al_2O_3)$  with thickness of 5 nm [23] on AlCu-based (Aluminum Copper alloy) ESP is also considered. The penetration ratio and absorption depth of the three types of ESP/ oxide stacks compared in Fig. 6 suggest that replacing

Y (nm)

b) Z = 0 (nm

0

σ = 30nm

Cu-Based ESP 0.36µm

EUV

(13.5nm)

3nm

at  $\mathbf{b} Z = 0$  nm and  $\mathbf{c} Z = -3$  nm.  $\mathbf{d}$  The 3D intensity distribution, indicating the energy profile of the injected EUV light

CuO by  $SiO_2$  can enhance EUV penetration by 10%, while the thickness of AlCu-based ESP needs to be above 150 nm to ensure EUV absorption. The further performance comparison based on measurement data between Cu-based ESP and AlCu-based ESP detectors will be addressed in our future work.

Next, the photo-response of the Cu-based ESP is measured and quantified through specially designed tests. The photography of the experimental setup uses synchrotron radiation of 13.5 nm, including the proposed micro-detectors, as well as a real-time EUV photocurrent

Table 1 FDTD parameters at wavelength of 13.5 nm

| Dielectric                          | Refractive index | Extinction coefficient | REF  |

|-------------------------------------|------------------|------------------------|------|

| Copper oxide (CuO)                  | 0.948            | 0.072                  | [20] |

| Silicon dioxide (SiO <sub>2</sub> ) | 0.97352          | 0.01608                | [21] |

| Aluminum oxide $(Al_2O_3)$          | 0.9714           | 0.035                  | [22] |

<sup>16</sup> Intensity

(W/m<sup>2</sup>)

0.6 Intensity

$(I_{\rm ph})$  measurement by a wireless module. During this experiment, the exposure time is controlled by an electrical shutter with switching time in millisecond level, while the light intensity is monitored simultaneously by a power meter. The measured photo-response current in real-time waveform can be used to check for alignment of the light beam.

Al<sub>2</sub>O<sub>3</sub>

AlCu

Fig. 6 EUV penetrated percentage through oxide and ESP

absorption depth of different oxide/metal compositions

CuO 3nm

Cu

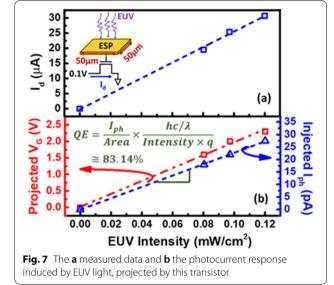

To estimate the Quantum Efficiency (QE) of ESP, the real-time EUV  $I_{\rm ph}$  is firstly measured by the channel current of a n-channel MOSFET with an AlCu-based ESP connected to its gate. Its ESP is charged under EUV exposure, turning on the transistor and raising its channel current ( $I_{\rm d}$ ), as demonstrated in Fig. 7a.

In this study, QE is essentially defined as followed:

$$QE = \frac{I_{\rm ph}}{\text{Sensing Area}} \times \frac{\text{Photon Energy}}{\text{EUV Intensity} \times q},$$

(1)

where q is the elementary electric charge.

Therefore, QE of the surface ESP is estimated to be 83.14% by injecting a gate current which fits the

channel current under a certain light intensity, as shown in Fig. 7b. In other words, 83.14% of incident photons will be converted to electrons on ESP due to the photoelectric effect, leading to positively charged ESP. The measured QE can be affected significantly by multiple non-ideal effects, for instance, absorption of native oxide, surface traps and so forth [24–26]. On the other hand, QE of conventional silicon-based EUV sensors is estimated as the amount of generated photoelectron divided by the incident photons, which is generally determined by its photoconductivity gain, biasing conditions and surface/ interface quality, etc. [27–29].

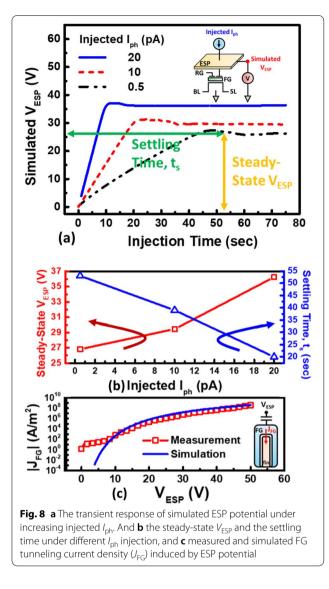

Furthermore, the simulated transient response of  $V_{\rm ESP}$  with the corresponding injected  $I_{\rm ph}$  is compared in Fig. 8a, both the settling time ( $t_{\rm s}$ ) and the steady-state  $V_{\rm ESP}$  can be obtained in Fig. 8b. As the data indicated, the settling time of ESP is about 50 s; hence, the minimum exposure time is set to be 500 s in this study to ensure the stability of EUV light. In an actual EUV scanner at the level of a few W/cm<sup>2</sup>, the settling time is expected to be less than 1 µs, while the exposure time of our on-wafer detector is expected to be higher than 20 µs. The injection current density into FG ( $I_{\rm FG}$ ) induced by  $V_{\rm ESP}$  is further shown in Fig. 8c, indicating higher  $V_{\rm ESP}$  results in higher  $J_{\rm FG}$  within a period of exposure time. These enable the model between the stored  $Q_{\rm FG}$  and EUV intensity to be established.

## **EUV Detection Results**

As discussed in Sect. 2, random charge may be stored in FG during the plasma process of manufacturing; therefore, initial calibration procedure is needed before EUV exposure. The threshold voltage ( $V_{th}$ ) distribution

Penetration Absorption Depth, dz 200

175

150

125

100

SiO<sub>2</sub> 5nm

2

3

100

Penetration (%

converged to its neutral state ( $V_{\rm th}$  at 4 V). It is done by biasing RS or substrate to high voltage so that channel hot carrier injection or FN tunneling may occur to clear out the initial  $Q_{\rm FG}$ .

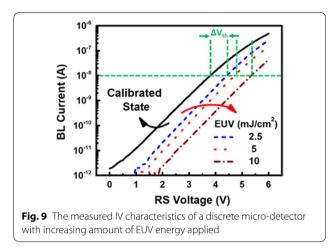

The electrical characteristics of the proposed microdetector before and after EUV exposure are compared in Fig. 9. Under the fixed intensity of 5  $\mu$ W/cm<sup>2</sup>, as the exposure time as well as the exposed EUV energy increases, tunneling current over a longer period of time is expected to occur between FG and substrate, leading to more FG charge. Hence, the IV curve shifts further to the right with increasing amount of FG charge, as reflected by the shift in  $V_{\text{th}}$ , as indicated in this plot. For monitoring EUV level during wafer-level test,  $V_{\text{th}}$  extraction can be done externally through automatic testing programs, measuring BL current under  $V_{\text{RS}}$  sweeps. To increase readout speed, readout circuits such as a  $V_{\text{th}}$  extractor

circuit [30] can be also incorporated through FinFET platform.

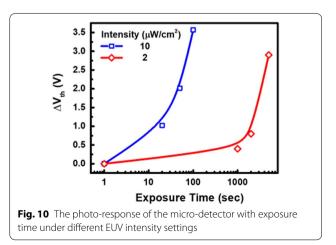

The measured  $V_{\rm th}$  shift ( $\Delta V_{\rm th}$ ) can reflect the projected EUV intensity and exposure time, as indicated in Fig. 10. As the EUV intensity increases, the photocurrent level on ESP is expected to raise, resulting in higher ESP potential. Consequently, more charge will be recorded in the in-pixel storage node (FG). Therefore, the combination of EUV light intensity and exposure time will determine the final  $Q_{\rm FG}$ , which in turn reflects on the readout  $\Delta V_{\rm th}$ . On the other hand, if the light intensity is too low, the detector will not be able to register the response as FG charge when tunneling effect is minimal even with long exposure time. In contrast, under high enough light intensity, the amount of FG charge is expected to be proportional to exposure time.

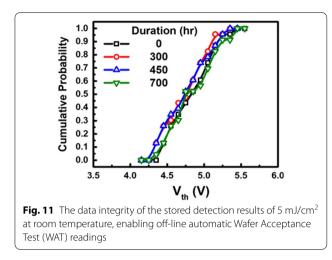

One of the unique features of the proposed microdetectors is its capability to store and record the detected image without external power supply, as demonstrated in Fig. 11. The detected EUV image can be recorded in the

in-pixel FG for months in room temperature after exposure, enabling follow-up off-line and non-destructive electrical reading.

## Conclusions

In this work, a novel embedded micro-detector for in situ and in-tool EUV imaging featuring FinFET CMOS compatibility, compact pixel structure and high spatial resolution is demonstrated. The promising EUV microdetectors can provide robust detection, precise monitoring for battery-less detection in EUV chambers.

#### Abbreviations

AlCu: Aluminum Copper Alloy; Al<sub>2</sub>O<sub>3</sub>: Aluminum oxide; APS: Active Pixel Sensor; BEOL: Back-end-of-line; BL: Bit line; BSI: Backside illuminated; CCD: Charge-coupled device; CD: Critical dimension; CIS: CMOS Image Sensor; CMOS: Complementary Metal Oxide Semiconductor; Cu: Copper; CuO: Copper oxide; ESP: Energy Sensing Pad; EUV: Extreme ultraviolet; FDTD: Finite-Difference Time-Domain; FG: Floating gate; FinFET: Fin Field-Effect Transistor; FN: Fowler-Nordheim tunneling effect; IC: Integrated circuit; I<sub>ph</sub>: Photocurrent; J<sub>FG</sub>: FG current density; LDD: Lightly Doped Drain; NASA: National Aeronaucts and Space Administration; QE: Quantum Efficiency; Q<sub>FG</sub>: FG charge; RS: Row select; SiO<sub>2</sub>: Silicon dioxide; SL: Source line; STI: Sallow Trench Isolation; SXR: Soft X-ray; TEM: Transmission Electron Microscope; t<sub>s</sub>: Settling time; V<sub>ESP</sub>: Energy Sensing Pad Potential; V<sub>FG</sub>: Floating gate potential; V<sub>RS</sub>: Row-select potential; V<sub>tt</sub>: Threshold voltage; WAT: Wafer Acceptance Test.

#### Acknowledgements

The authors would like to thank the support from Taiwan Semiconductor Manufacturing Company (TSMC) and the Ministry of Science and Technology (MOST), Taiwan (Project Number: MOST 110-2622-8-007-018).

#### Authors' contributions

Equal contributions for all authors and discussed the results. All authors read and approved the final manuscript.

#### Funding

This study is supported by Taiwan Semiconductor Manufacturing Company (TSMC) and the Ministry of Science and Technology (MOST), Taiwan (Project Number: MOST 110-2622-8-007-018).

#### Availability of data and materials

Not applicable.

#### Declarations

#### **Competing interests**

The authors declare that they have no competing interests.

#### Author details

<sup>1</sup> Institute of Electronics Engineering, National Tsing Hua University, Hsinchu, Taiwan. <sup>2</sup>Institute of Photonics Technologies, National Tsing Hua University, Hsinchu, Taiwan. <sup>3</sup>National Synchrotron Radiation Research Center, Hsinchu, Taiwan. <sup>4</sup>Design Technology Division, Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan.

#### Received: 13 October 2021 Accepted: 22 December 2021 Published online: 05 January 2022

#### References

- Shi L, Nihtianov S (2012) Comparative study of silicon-based ultraviolet photodetectors. IEEE Sens J 12(7):2453–2459

- Young PR (2021) Future prospects for solar EUV and soft X-ray spectroscopy missions. Front Astron Space Sci 8:50

- Wachulak PW, Torrisi A, Bartnik A et al (2017) A desktop extreme ultraviolet microscope based on a compact laser-plasma light source. Appl Phys B 123:25

- Gunjala G, Wojdyla A, Sherwin S et al (2020) Extreme ultraviolet microscope characterization using photomask surface roughness. Sci Rep 10:11673

- Turkot B, Carson S, Lio A (2017) Continuing Moore's law with EUV lithography. In: 2017 IEEE international electron devices meeting (IEDM), 2017, pp 14.4.1–14.4.3

- Xie R et al. (2016) A 7 nm FinFET technology featuring EUV patterning and dual strained high mobility channels. In: 2016 IEEE international electron devices meeting (IEDM), pp 2.7.1–2.7.4

- Luong V, Philipsen V, Hendrickx E, Opsomer K, Detavernier C, Laubis C, Scholze F, Heyns M (2018) Ni-Al alloys as alternative EUV mask absorber. Appl Sci 8(4):521

- Kang HY, Hwangbo CK (2009) Absorber stack with transparent conductive oxide layer for extreme ultraviolet lithography. J Vac Sci Technol B Microelectron Nanometer Struct Process Meas Phenom 27:58–60

- Shi L, Nanver LK, Nihtianov SN (2011) Stability characterization of highsensitivity silicon-based EUV photodiodes in a detrimental industrial environment. In: IECON 2011—37th annual conference of the IEEE industrial electronics society, 2011, pp 2651–2656

- Rao PR, Laubis C, Nihtianov S (2014) Backside illuminated CMOS image sensors for extreme ultraviolet applications. In: Sensors, 2014 IEEE, pp 1660–1663

- Stern RA, Shing L, Waltham N, Mapson-Menard H, Harris A, Pool P (2011) EUV and soft X-ray quantum efficiency measurements of a thinned back-illuminated CMOS active pixel sensor. IEEE Electron Device Lett 32(3):354–356

- 12. Shang Y, Guan Y, Liu Y, Zhao X (2008) The design of EUV CCD camera. In: Proc. SPIE 7021, high energy, optical, and infrared detectors for astronomy III, p 702110

- Okano K et al. (2005) Process integration technology and device characteristics of CMOS FinFET on bulk silicon substrate with sub-10 nm fin width and 20 nm gate length. In: 2005 IEEE international electron devices meeting (IEDM), pp 721–724

- Veloso A, Lee JW, Simoen E, Ragnarsson L-Å, Arimura H, Cho MJ, Boccardi G, Thean A, Horiguchi N (2014) Replacement metal gate/high-k last technology for aggressively scaled planar and FinFET-based devices. ECS Trans 61(2):225–235

- Standaert T et al. (2016) BEOL process integration for the 7 nm technology node. In: 2016 IEEE international interconnect technology conference/advanced metallization conference (IITC/AMC), pp 2–4

- Han X, Yang C, Li D, Zhang S (2008) A simple nano-scale patterning technology for FinFET fabrication. In: 2008 9th international conference on solid-state and integrated-circuit technology, pp 1340–1342

- Tanwar K, Canaperi D, Lofaro M, Tseng W-T, Patlolla R, Penny C, Waskiewicz C (2013) BEOL Cu CMP process evaluation for advanced technology nodes. J Electrochem Soc 160(12):3247–3254

- Ishak AM, Ishak MT, Jusoh MT, Syed Dardin SF, Judd MD (2017) Design and optimization of UHF partial discharge sensors using FDTD modeling. IEEE Sens J 17(1):127–133

- 19. Kim SJ, Kim S, Lee J et al (2021) Color of copper/copper oxide. Adv Mater 33(15):2007345

- Brimhall N, Herrick N, Allred DD, Turley RS, Ware M, Peatross J (2009) Measured optical constants of copper from 10 nm to 35 nm. Opt Express 17(26):23873–23879

- Bodermann B, Wurm M, Diener A, Scholze F, Groß H (2009) EUV and DUV scatterometry for CD and edge profile metrology on EUV masks. In: Proc. SPIE, vol 7470, p 74700F

- Rebellato J, Meltchakov E, Soufli R, Rossi SD, Zhang X, Auchère F, Delmotte F (2018) Analyses of tabulated optical constants for thin films in the EUV range and application to solar physics multilayer coatings. In: Proc. SPIE, vol 10691, p 106911U

- 23. Saif MTA, Zhang S, Haque A, Hsi KJ (2002) Effect of native  $Al_2O_3$  on the elastic response of nanoscale Al films. Acta Mater 50(11):2779–2786

- Schuster J, Bellotti E (2014) Evaluation of quantum efficiency, crosstalk, and surface recombination in HgCdTe photon-trapping structures. J Electron Mater 43:2808–2817

- Booker RL, Geist JC (1982) Photodiode quantum efficiency enhancement at 365 nm: optical and electrical. Appl Opt 21(22):3987–3989

- 26. Hamden ET, Jewell AD, Shapiro CA, Cheng SR, Goodsall TM, Hennessy J, Hoenk ME, Jones T, Gordon S, Ong HR, Schiminovich D, Martin DC, Nikzad S (2016) Charge-coupled devices detectors with high quantum efficiency at UV wavelengths. J Astron Telesc Instrum Syst 2(3):036003

- Mudgal S, Singh S, Komarala VK (2018) Interfacial spectral response under voltage and light bias to analyse low voltage in amorphous-crystalline silicon heterojunction solar cell with S-shape characteristics. In: 2018 IEEE 7th world conference on photovoltaic energy conversion (WCPEC) (a joint conference of 45th IEEE PVSC, 28th PVSEC & 34th EU PVSEC), pp 2158–2161

- Li X, Carey JE, Sickler JW, Pralle MU, Palsule C, Vineis CJ (2012) Silicon photodiodes with high photoconductive gain at room temperature. Opt Express 20(5):5518–5523

- Kuroda R, Kawada S, Nasuno S, Nakazawa T, Koda Y, Hanzawa K, Sugawa S (2014) A highly ultraviolet light sensitive and highly robust image sensor technology based on flattened Si surface. ITE Trans Media Technol Appl 2(2):123–130

- Johnson MG (1993) An input-free VT extractor circuit using a two-transistor differential amplifier. IEEE J Solid-State Circuits 28(6):704–705

#### **Publisher's Note**

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

# Submit your manuscript to a SpringerOpen<sup>®</sup> journal and benefit from:

- Convenient online submission

- ► Rigorous peer review

- Open access: articles freely available online

- High visibility within the field

- Retaining the copyright to your article

Submit your next manuscript at > springeropen.com