### NANO EXPRESS Open Access

# High-Performance a-InGaZnO Thin-Film Transistors with Extremely Low Thermal Budget by Using a Hydrogen-Rich Al<sub>2</sub>O<sub>3</sub> Dielectric

Yan Shao, Xiaohan Wu, Mei-Na Zhang, Wen-Jun Liu and Shi-Jin Ding to

#### **Abstract**

Electrical characteristics of amorphous In-Ga-Zn-O (a-IGZO) thin-film transistors (TFTs) are compared by using  $O_2$  plasma-enhanced atomic layer deposition  $Al_2O_3$  dielectrics at different temperatures. High-performance a-IGZO TFTs are demonstrated successfully with an  $Al_2O_3$  dielectric deposited at room temperature, which exhibit a high field-effect mobility of  $19.5~\rm cm^2~V^{-1}~s^{-1}$ , a small subthreshold swing of  $160~\rm mV/dec$ , a low threshold voltage of  $0.1~\rm V$ , a large on/off current ratio of  $4.5\times10^8$ , and superior negative and positive gate bias stabilities. This is attributed to the hydrogen-rich  $Al_2O_3$  dielectric deposited at room temperature in comparison with higher deposition temperatures, thus efficiently passivating the interfacial states of a-IGZO/ $Al_2O_3$  and the oxygen vacancies and improving conductivity of the a-IGZO channel by generating additional electrons because of enhanced hydrogen doping during sputtering of IGZO. Such an extremely low thermal budget for high-performance a-IGZO TFTs is very attractive for flexible electronic application.

**Keywords:** Amorphous In-Ga-Zn-O, Thin-film transistor, Room temperature, Atomic layer deposition, Hydrogen-rich Al<sub>2</sub>O<sub>3</sub>

#### **Background**

Amorphous In-Ga-Zn-O (a-IGZO)-based thin film transistors (TFTs) have attracted much attention in the past decade due to their high mobility, good uniformity, high visible light transparency, and low process temperature [1-3]. These merits make it a promising candidate for the application of next-generation electronics, such as transparent display, flexible devices, or wearable electronics. In particular, for the applications of flexible electronics, TFTs are generally fabricated on low thermally stable polymer substrates. Thus, it is necessary to reduce the thermal budget of a-IGZO TFT fabrication. For this purpose, many researchers have focus on a-IGZO TFTs with room temperature fabricated gate insulators, such as sputtering [4-6], solution process [7-9], e-beam evaporation [10], and anodization [11]. However, these dielectric films often suffer from high density of traps and strong dielectric/a-IGZO interfacial scattering, thus resulting in limited field-effect mobility, a large subthreshold swing, and a small on/off current ratio [4–11].

On the other hand, atomic layer deposition (ALD) is a promising technique, which can provide high-quality films, precise control of film thickness, good uniformity over a large area, and low process temperature [12–14]. Zheng et al. [15] reported that the a-IGZO TFT with ALD SiO<sub>2</sub> dielectric exhibited excellent electrical performance without the need of post-annealing. However, a high substrate temperature of 250 °C is required for the ALD of SiO<sub>2</sub> films [15], which is higher than glass transition temperatures of most flexible plastic substrates. Interestingly, it is reported that ALD of Al<sub>2</sub>O<sub>3</sub> films can be realized even at room temperature (RT) [16, 17]; meanwhile, the Al<sub>2</sub>O<sub>3</sub> film deposited at RT contains a large amount of hydrogen (H) impurities [17]. However, to the best of our knowledge, the abovementioned H-rich Al<sub>2</sub>O<sub>3</sub> film has never been utilized as a gate insulator in a-IGZO TFT. Therefore, it is desirable to explore the a-IGZO TFT with a RT ALD Al<sub>2</sub>O<sub>3</sub> gate insulator.

<sup>\*</sup> Correspondence: sjding@fudan.edu.cn School of Microelectronics, Fudan University, Shanghai 200433, People's Republic of China

Shao et al. Nanoscale Research Letters (2019) 14:122 Page 2 of 6

In this letter, high-performance a-IGZO TFT was successfully fabricated with a room temperature deposited  $Al_2O_3$  gate dielectric. By comparing the characteristics of the a-IGZO TFTs with various  $Al_2O_3$  gate insulators deposited at different temperatures, the underlying mechanism was addressed.

#### **Methods**

Highly doped p-type silicon wafers ( $< 0.0015 \Omega$  cm) were cleaned by standard RCA processes and served as gate electrodes. Forty-nanometer Al<sub>2</sub>O<sub>3</sub> films were deposited in a commercial ALD system (Picsun Ltd.) using trimethylaluminum (TMA) and O<sub>2</sub> plasma as a precursor and reactant, respectively. One growth cycle consisted of 0.1 s TMA pulse, 10 s N<sub>2</sub> purge, 8 s O<sub>2</sub> plasma pulse, and 10 s N2 purge. The TMA was maintained at 18 °C for a stable vapor pressure and dose, and the O<sub>2</sub> gas flow rate was fixed at 150 sccm with a plasma generator power of 2500 W. Subsequently, 40-nm a-IGZO films were deposited by RF sputtering using an IGZO ceramic target with an atomic ratio of In:Ga:Zn:O = 1:1:1:4. During sputtering, working pressure and Ar and O<sub>2</sub> gas flow rates were fixed at 0.88 Pa and 48 and 2 sccm, respectively. The active region was formed by photolithography and wet etching. After that, source/drain electrodes of 30-nm Ti/70-nm Au bilayers were prepared by electron beam evaporation and a lift-off method. No further annealing processes were applied on these devices.

The electrical properties of a-IGZO TFTs were characterized using a semiconductor device analyzer (Agilent Tech B1500A) in a dark box at room temperature. The device stabilities were measured under positive and negative gate bias stresses, respectively. The depth profiles of elements and chemical composition were measured by secondary ion mass spectrometry (SIMS) and X-ray photoelectron spectroscopy (XPS), respectively.

#### **Results and Discussion**

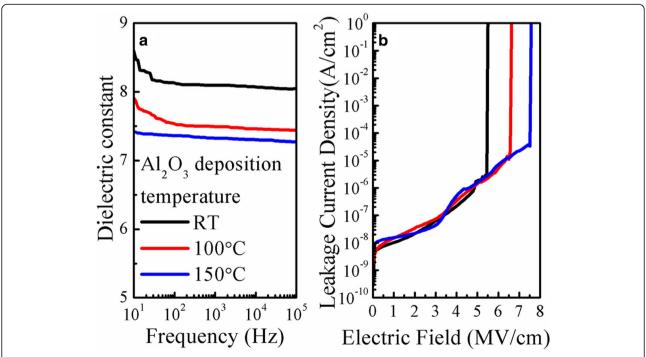

Figure 1a compares the dielectric constants of the Al<sub>2</sub>O<sub>3</sub> films deposited at different temperatures as a function of frequency (i.e., from 10 Hz to 10<sup>5</sup> Hz). As the deposition temperature increases from 100 to 150 °C, the film shows a gradual decrease in dielectric constant. A similar trend was also reported in previous literatures for the deposition temperature changing from RT to 150 °C [18, 19]. This is because the RT Al<sub>2</sub>O<sub>3</sub> film contains the highest concentration of hydrogen (H) in the form of OH groups. Thus, the corresponding dielectric constant is enhanced due to a rotation of more OH groups in an electric field [20]. In terms of the measurement frequency of 10 Hz, the extracted dielectric constants for the RT, 100 °C, and 150 °C Al<sub>2</sub>O<sub>3</sub> films are equal to 8.6, 7.9, and 7.4, respectively, which are used for the extraction of the field-effect mobility ( $\mu_{EE}$ ) and interfacial trap density ( $D_{it}$ ) of the

Fig. 1 Electrical properties of  $Al_2O_3$  films deposited at different temperatures. a Dielectric constant versus frequency. b Leakage current density versus electric field

Shao et al. Nanoscale Research Letters (2019) 14:122 Page 3 of 6

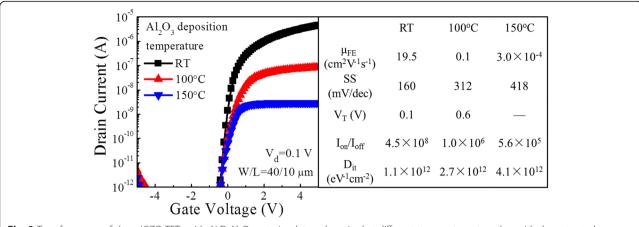

Fig. 2 Transfer curves of the a-IGZO TFTs with ALD  $Al_2O_3$  gate insulators deposited at different temperatures together with the extracted device parameters

fabricated TFT device. Figure 1b shows the leakage current characteristics of different  $\rm Al_2O_3$  films. It is found that the RT  $\rm Al_2O_3$  film exhibits a small leakage current density of  $2.38\times 10^{-8}~\rm A/cm^2$  at 2 MV/cm and a breakdown electric field of 5.3 MV/cm. In addition, the breakdown electric field increases gradually with increasing deposition temperature from 100 to 150 °C.

Figure 2 shows the typical transfer curves of the a-IGZO TFTs with different  ${\rm Al_2O_3}$  gate insulators. The RT  ${\rm Al_2O_3}$  TFT exhibits the best performance, such as high  $\mu_{\rm FE}$  of  $19.5~{\rm cm^2\,V^{-1}\,s^{-1}}$ , a small subthreshold swing (SS) of  $160~{\rm mV/dec}$ , a small threshold voltage ( $V_{\rm T}$ ) of  $0.1~{\rm V}$ , and a large on/off current ratio ( $I_{\rm on/off}$ ) of  $4.5\times10^8$ . However, the a-IGZO TFTs with  ${\rm Al_2O_3}$  gate insulators deposited at both  $100~{\rm and}~150~{\rm °C}$  show a much

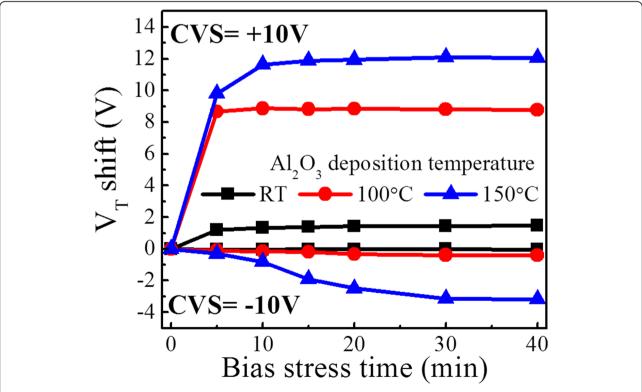

Fig. 3  $V_T$  shift as a function of bias stress time under NGBS = -10 V and PGBS = 10 V for the TFTs with Al<sub>2</sub>O<sub>3</sub> insulators deposited at different temperatures

Shao et al. Nanoscale Research Letters (2019) 14:122 Page 4 of 6

poorer performance, i.e., reduced on-currents ( $10^{-7}$  and  $3 \times 10^{-9}$  A) and degraded SS. The  $D_{\rm it}$  at the interface of Al<sub>2</sub>O<sub>3</sub>/a-IGZO can be calculated based on the following equation [21]:

$$D_{\rm it} = \left(\frac{\rm SS \times lge}{kT/q} - 1\right) \frac{C_{ox}}{q^2} \tag{1}$$

where e, k, T, and q represent the Euler's number, Boltzmann constant, absolute temperature, and unit electron charge, respectively.  $C_{\rm ox}$  is the gate dielectric capacitance per unit area. For the RT Al<sub>2</sub>O<sub>3</sub> TFT, the  $D_{\rm it}$  is equal to  $1.1\times10^{12}\,{\rm eV^{-1}\,cm^{-2}}$ , which is over one or two times lower than those for the TFTs with the Al<sub>2</sub>O<sub>3</sub> gate insulators deposited at 100 and 150 °C.

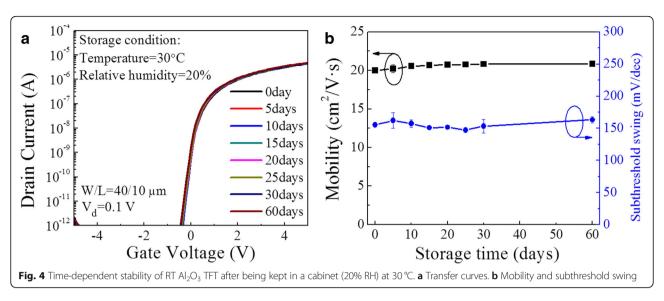

The gate bias stabilities of the devices were further measured by applying negative and positive voltages. Figure 3 shows the  $V_{\mathrm{T}}$  shift as a function of bias stress time for different TFTs. In terms of negative gate bias stress (NGBS), the RT Al<sub>2</sub>O<sub>3</sub> TFT exhibits a negligible  $V_{\rm T}$  shift of  $-0.04\,{\rm V}$ after being stressed at -10 V for 40 min. However, highertemperature  $Al_2O_3$  gate insulators generate larger  $V_T$  shifts especially for 150 °C. Such a high NGBS stability for RT Al<sub>2</sub>O<sub>3</sub> should be attributed to a low concentration of oxygen vacancies  $(V_{\rm O})$  in the a-IGZO channel [22]. With respect to positive gate bias stress (PGBS), the RT Al<sub>2</sub>O<sub>3</sub> TFT shows a  $V_{\rm T}$  shift of 1.47 V, which is much smaller than those (8.8 V and 12.1 V) for the 100 and 150 °C Al<sub>2</sub>O<sub>3</sub> TFTs. Moreover, the influence of storage time on the device performance was investigated, as shown in Fig. 4. Although no passivation layer is covered on the back channel, the device still maintains an excellent performance after being kept in a cabinet (20% RH) for 60 days at 30 °C; meanwhile, no significant variations in  $\mu_{\rm FE}$  and SS are observed. This indicates the RT Al<sub>2</sub>O<sub>3</sub> TFTs without any passivation layer have good storage-time-dependent stability in the current ambience.

Table 1 compares the performance of our RT  $Al_2O_3$  TFT with other reports. It is found that our device exhibits a zero-near  $V_T$ , smaller SS, and larger  $I_{on/off}$  in the case of comparable mobility [4, 23]. Although using a  $Ta_2O_5$  gate insulator can obtain higher mobility of  $61.5 \, \mathrm{cm}^2 \, \mathrm{V}^{-1} \, \mathrm{s}^{-1}$ , both SS and  $I_{on/off}$  deteriorate remarkably [10]. In a word, our RT  $Al_2O_3$  TFT possesses a superior comprehensive performance in comparison with the 100 and 150 °C  $Al_2O_3$  TFTs. Since all processing steps are identical except the deposition step of  $Al_2O_3$ , such significant differences in electrical performance should originate from the  $Al_2O_3$  gate insulators.

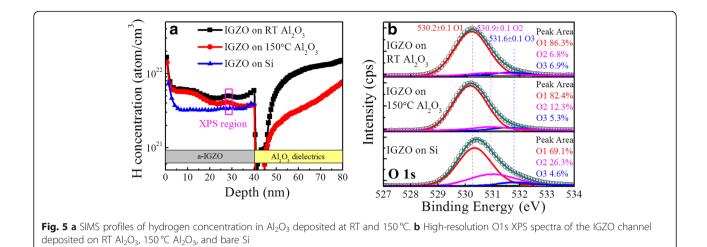

To understand the underlying mechanism, the depth profiles of the elements in the a-IGZO/Al<sub>2</sub>O<sub>3</sub> stacked films were analyzed by SMIS. Figure 5a shows the dependence of H concentration on depth in the stacks of IGZO/Al<sub>2</sub>O<sub>3</sub>, where the Al<sub>2</sub>O<sub>3</sub> films were deposited at RT and 150 °C, respectively. For comparison, an IGZO film deposited on a bare Si substrate was also analyzed. The IGZO film deposited on bare Si contains an H concentration of  $\sim 3 \times 10^{21} \, {\rm cm}^{-3}$ , which originates from the residual gas in sputtering system and absorbed H<sub>2</sub>/H<sub>2</sub>O

**Table 1** Comparison of the electrical parameters of our RT  $Al_2O_3$  a-IGZO TFT and other a-IGZO TFTs fabricated at low temperatures ( $T_{\rm max}$  denotes the maximum process temperature)

| Insulator                      | $T_{\max}$ (°C) | $\mu_{\rm EF} \over ({\rm cm}^2{\rm V}^{-1}{\rm s}^{-1})$ | SS<br>(V/dec) | V <sub>T</sub><br>(V) | l <sub>on</sub> / <sub>off</sub> | Ref.      |

|--------------------------------|-----------------|-----------------------------------------------------------|---------------|-----------------------|----------------------------------|-----------|

| Al <sub>2</sub> O <sub>3</sub> | RT              | 19.5                                                      | 0.16          | 0.1                   | $4.5 \times 10^{8}$              | This work |

| $Al_2O_3$                      | RT              | 7.5                                                       | 0.44          | -                     | $3.1 \times 10^{8}$              | [31]      |

| $Al_2O_3$                      | 60              | 5.9                                                       | 0.26          | 2.48                  | 10 <sup>8</sup>                  | [9]       |

| SiO <sub>2</sub>               | RT              | 18.5                                                      | 0.27          | 1.5                   | 10 <sup>7</sup>                  | [4]       |

| SiO <sub>2</sub>               | RT              | 15.8                                                      | 0.66          | -0.42                 | $4.4 \times 10^{5}$              | [23]      |

| SiO <sub>2</sub>               | 90              | 11                                                        | 0.4           | 0.44                  | 10 <sup>5</sup>                  | [32]      |

| Ta <sub>2</sub> O <sub>5</sub> | RT              | 61.5                                                      | 0.61          | 0.25                  | 10 <sup>5</sup>                  | [10]      |

Shao et al. Nanoscale Research Letters (2019) 14:122 Page 5 of 6

molecules on the Si surface. Both IGZO films deposited on the Al<sub>2</sub>O<sub>3</sub> films contain higher H concentrations than that on the bare Si substrate. This indicates that the increased H concentrations should come from the release of H impurities in the underlying Al<sub>2</sub>O<sub>3</sub> films during sputtering of IGZO. Moreover, it is observed that the H concentration in the IGZO film atop the RT Al<sub>2</sub>O<sub>3</sub> film is higher than that on the 150 °C one in the interface-near region, which can provide more efficient passivation of interfacial states. This thus improves the SS and PGBS stability of the RT Al<sub>2</sub>O<sub>3</sub> TFT by reducing interfacial carrier trapping. Additionally, the O 1s XPS spectra of the a-IGZO films near the interface of IGZO/Al<sub>2</sub>O<sub>3</sub> were analyzed, as shown in Fig. 5b. The fitted peaks are located at 530.2 ± 0.1 eV,  $530.9 \pm 0.1 \text{ eV}$ , and  $531.6 \pm 0.1 \text{ eV}$ , corresponding to  $O^{2-}$  ions bound with metal (O1),  $V_O$  (O2), and OH groups (O3), respectively [13, 24]. The percentage of O2 is 26.3% in the a-IGZO layer atop the bare Si; however, it decreases to 12.3% and 6.8% for the 150 °C and RT Al<sub>2</sub>O<sub>3</sub> underlying films, respectively. This indicates that more  $V_{\rm O}$  in the IGZO channel can be effectively passivated by additional H impurities originating from the underlying Al<sub>2</sub>O<sub>3</sub> films, especially for the RT Al<sub>2</sub>O<sub>3</sub> film with a higher H concentration. It is reported that when  $V_{\rm O}$  and H both are present in the a-IGZO film, they can combine to form a stable state in which H is trapped at  $V_{\rm O}$  ( $V_{\rm O}$ H), and the resulting  $V_{\rm O}H$  is a shallow-level donor [25–27]. Thus, enhanced H doping into the IGZO channel atop the RT Al<sub>2</sub>O<sub>3</sub> improves the channel conductivity by providing additional electrons. Furthermore, the small  $V_{\rm T}$  shift under the NGBS for the RT Al<sub>2</sub>O<sub>3</sub> TFT can also be attributed to the effective H passivation of  $V_{\rm O}$  [28]. As reported in literatures, the instability of TFT under NGBS originates from ionization of neutral  $V_{\rm O}$  ( $V_{\rm O} \rightarrow {V_{\rm O}}^{2+} + 2e^-$ ) [17, 29]. Moreover, the O3 percentage of the a-IGZO film on the RT  $Al_2O_3$  is 6.9%, which is higher than those on the 150 °C Al<sub>2</sub>O<sub>3</sub> (5.3%) and the bare Si (4.6%), respectively. The OH group could originate from the reaction  $O^{2-} + H \rightarrow OH^- + e^-$  during deposition of IGZO films [30]. Thus, the enhanced H doping into the IGZO channel atop the RT  $Al_2O_3$  film generates more OH groups and also contributes to improve the channel conductivity.

#### **Conclusions**

A high-performance a-IGZO TFT was fabricated successfully under the extremely low thermal budget of RT using an H-rich  ${\rm Al_2O_3}$  gate dielectric prepared by  ${\rm O_2}$  plasma-enhanced ALD. This is ascribed to the fact that the  ${\rm Al_2O_3}$  dielectric deposited at RT contains more hydrogen impurities than those deposited at higher temperatures. Thus, the released H impurities during sputtering of IGZO generated more electrons, and efficiently passivated the interfacial states of a-IGZO/Al<sub>2</sub>O<sub>3</sub> and the  $V_{\rm O}$  in the a-IGZO channel.

#### Abbreviations

a-IGZO: Amorphous In-Ga-Zn-O; ALD: Atomic layer deposition;  $D_{\rm it}$ : Interfacial trap density; H: Hydrogen;  $I_{\rm on/off}$ : On/off current ratio; NGBS: Negative gate bias stress; PGBS: Positive gate bias stress; RT: Room temperature; SIMS: Secondary ion mass spectrometry; SS: Subthreshold swing; TFT: Thinfilm transistor;  $V_{\rm O}$ : Oxygen vacancy;  $V_{\rm O}$ H: Hydrogen trapped at oxygen vacancy;  $V_{\rm T}$ : Threshold voltage; XPS: X-ray photoelectron spectroscopy;  $\mu_{\rm FE}$ : Field-effect mobility

#### Acknowledgements

There is no acknowledgement.

#### Funding

This work was supported by the National Natural Science Foundation of China (61874029, 61474027, 51603151), and the National Key Technologies R&D Program of China (2015ZX02102-003).

#### Availability of Data and Materials

All datasets are presented in the main paper and freely available to any scientist wishing to use them for non-commercial purposes, without breaching participant confidentiality.

Shao et al. Nanoscale Research Letters (2019) 14:122 Page 6 of 6

#### **Authors' Contributions**

YS and MNZ carried out the main part of the fabrication and analytical works. YS, XW, and SJD participated in the sequence alignment and drafted the manuscript. SJD and WJL conceived the study and participated in its design. All authors read and approved the final manuscript.

#### **Competing Interests**

The authors declare that they have no competing interests.

#### **Publisher's Note**

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

### Received: 28 December 2018 Accepted: 26 March 2019 Published online: 02 April 2019

#### References

- Nomura K, Ohta H, Takagi A et al (2004) Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432:488–492

- Park JS, Maeng WJ, Kim HS et al (2011) Review of recent developments in amorphous oxide semiconductor thin-film transistor devices. Thin Solid Films 520:1679–1692

- Zan HW, Yeh CC, Meng HF et al (2012) Achieving high field-effect mobility in amorphous indium- gallium-zinc oxide by capping a strong reduction layer. Adv Mater 24:3509–3514

- 4. Zheng Z, Zeng Y, Yao R et al (2017) All-sputtered, flexible, bottom-gate  $IGZO/Al_2O_3$  bi-layer thin film transistors on PEN fabricated by a fully room temperature process. J Mater Chem C 5:7043–7050

- Huang XD, Ma Y, Song JQ, Lai PT (2016) High-performance amorphous InGaZnO thin-film transistor with ZrLaO gate dielectric fabricated at room temperature. J Disp Technol 12:1522–1527

- Nag M, Bhoolokam A, Steudel S et al (2015) Impact of the low temperature gate dielectrics on device performance and bias-stress stabilities of a-IGZO thin-film transistors. ECS J Solid State SC 4:N99–N102

- Hsu CC, Chu MW, Sun JK, Chou HT (2016) Low temperature fabrication of an amorphous InGaZnO thin-film transistor with a sol-gel SiO<sub>2</sub> gate dielectric. J Disp Technol 12:1043–1050

- Seul HJ, Kim HG, Park MY, Jeong JK (2016) A solution-processed silicon oxide gate dielectric prepared at a low temperature via ultraviolet irradiation for metal oxide transistors. J Mater Chem C 4:10486–10493

- Jo JW, Kim YH, Park J et al (2017) Ultralow-temperature solution-processed aluminum oxide dielectrics via local structure control of nanoclusters. ACS Appl Mater Interfaces 9:35114–35124

- Chiu CJ, Chang SP, Chang SJ (2010) High-performance a-IGZO thin-film transistor using Ta<sub>2</sub>O<sub>5</sub> gate dielectric. IEEE Electron Device Lett 31:1245–1247

- 11. Shao Y, Xiao X, He X et al (2015) Low voltage a-InGaZnO thin-film transistors with anodized thin  $HfO_2$  gate dielectric. IEEE Electron Device Lett 36:573–575

- Ok KC, Park SHK, Hwang CS et al (2014) The effects of buffer layers on the performance and stability of flexible InGaZnO thin film transistors on polyimide substrates. Appl Phys Lett 104:063508

- Sheng J, Han J, Choi W, Park J, Park JS (2017) Performance and stability enhancement of in–Sn–Zn–O TFTs using SiO<sub>2</sub> gate dielectrics grown by low temperature atomic layer deposition. ACS Appl Inter Mater 49: 42928–42934

- Levy DH, Nelson SF (2011) Thin-film electronics by atomic layer deposition.

J Vac Sci Technol A 30:018501

- Zheng LL, Ma Q, Wang YH et al (2016) High-performance unannealed a-InGaZnO TFT with an atomic-layer-deposited SiO<sub>2</sub> insulator. IEEE Electron Device Lett 37:743–746

- Groner MD, Fabreguette FH, Elam JW, George SM (2003) Low-temperature Al<sub>2</sub>O<sub>3</sub> atomic layer deposition. Chem Mater 16:639–645

- Potts SE, Keuning W, Langereis E et al (2010) Low temperature plasmaenhanced atomic layer deposition of metal oxide thin films. J Electrochem Soc 157:P66–P74

- Kim SK, Lee SW, Hwang CS et al (2005) Low temperature (<100°C) deposition of aluminum oxide thin films by ALD with O<sub>3</sub> as oxidant. J Electrochem Soc 153:F69–F76

- Niskanen A, Arstila K, Ritala M, Leskela M (2005) Low-temperature deposition of aluminum oxide by radical enhanced atomic layer deposition. J Electrochem Soc 152:F90–F93

- Pethrick RA, Hayward D, Jeffry K, Affrossman S, Wilford P (1996)

Investigation of the hydration and dehydration of aluminium oxide-hydroxide using high frequency dielectric measurements between 300 kHz-3 GHz. J Mater Sci 31:2623–2629

- 21. Schroder DK (2005) Semiconductor material and device characterization, 3rd edn. Wiley, Hoboken

- Moon YK, Lee S, Kim DH et al (2009) Application of DC magnetron sputtering to deposition of InGaZnO films for thin film transistor devices. Jpn J Appl Phys 48:031301

- Ning H, Zeng Y, Kuang Y et al (2017) Room-temperature fabrication of highperformance amorphous In–Ga–Zn–O/Al<sub>2</sub>O<sub>3</sub> thin-film transistors on Ultrasmooth and clear nanopaper. ACS Appl Mater Interfaces 9:27792–27800

- Tsao SW, Chang TC, Huang SY et al (2010) Hydrogen-induced improvements in electrical characteristics of a-IGZO thin-film transistors. Solid State Electron 54:1497–1499

- 25. Nakashima M, Oota M, Ishihara N et al (2014) Origin of major donor states in In-Ga-Zn oxide. J Appl Phys 116:213703

- Xu L, Chen Q, Liao L et al (2016) Rational hydrogenation for enhanced mobility and high reliability on ZnO-based thin film transistors: from simulation to experiment. ACS Appl Mater Interfaces 8:5408–5415

- Chen C, Cheng KC, Chagarov E, Kanicki J (2011) Crystalline In–Ga–Zn–O density of states and energy band structure calculation using density function theory. Jpn J Appl Phys 50:091102

- 28. Chen C, Yang BR, Li G et al (2019) Analysis of ultrahigh apparent mobility in oxide field-effect transistors. Adv Sci:1801189

- Kim Y, Kim S, Kim W et al (2012) Amorphous InGaZnO thin film transistors—PART II: modeling and simulation of negative bias illumination stress-induced instability. IEEE Trans Electron Devices 59:2699–2706

- Bang J, Matsuishi S, Hosono H (2017) Hydrogen anion and subgap states in amorphous In–Ga–Zn–O thin films for TFT applications. Appl Phys Lett 110:232105

- Xiao X, Zhang L, Shao Y et al (2017) Room-temperature-processed flexible amorphous InGaZnO thin film transistor. ACS Appl Mater Interfaces 10: 25850–25857

- 32. Lim W, Jang JH, Kim SH et al (2008) High performance indium gallium zinc oxide thin film transistors fabricated on polyethylene terephthalate substrates. Appl Phys Lett 93:082102

## Submit your manuscript to a SpringerOpen journal and benefit from:

- ► Convenient online submission

- ► Rigorous peer review

- ► Open access: articles freely available online

- ► High visibility within the field

- ► Retaining the copyright to your article

Submit your next manuscript at ▶ springeropen.com