### NANO EXPRESS Open Access

# Suppression of Filament Overgrowth in Conductive Bridge Random Access Memory by Ta<sub>2</sub>O<sub>5</sub>/TaO<sub>x</sub> Bi-Layer Structure

Jie Yu<sup>1,2</sup>, Xiaoxin Xu<sup>1\*</sup>, Tiancheng Gong<sup>1</sup>, Qing Luo<sup>1</sup>, Danian Dong<sup>1</sup>, Peng Yuan<sup>1</sup>, Lu Tai<sup>2</sup>, Jiahao Yin<sup>1</sup>, Xi Zhu<sup>1</sup>, Xiulong Wu<sup>2</sup>, Hangbing Lv<sup>1\*</sup> and Ming Liu<sup>1</sup>

#### **Abstract**

Bi-layer structure has been widely adopted to improve the reliability of the conductive bridge random access memory (CBRAM). In this work, we proposed a convenient and economical solution to achieve a  $Ta_2O_5/TaO_x$  bi-layer structure by using a low-temperature annealing process. The addition of a  $TaO_x$  layer acted as an external resistance suppressing the overflow current during set programming, thus achieving the self-compliance switching. As a result, the distributions of high-resistance states and low-resistance states are improved due to the suppression of the overset phenomenon. In addition, the LRS retention of the CBRAM is obviously enhanced due to the recovery of defects in the switching film. This work provides a simple and economical method to improve the reliability of CBRAM.

**Keywords:** Conductive bridge resistive switching memory (CBRAM), CMOS-compatible process, Bi-layer structure, Reliability

#### Introduction

Conductive bridge resistive switching memory (CBRAM) is a breakthrough technology and is considered as next-generation non-volatile memory (NVM) due to its high scalability, simple structure, ease of 3D integration, and high-speed operation [1-3]. For practical application, the reliability issues, including the data retention and endurance, hinder the definitive introduction of these memory devices into the memory market. Structure engineering is the most popular approach to improve the reliability of CBRAM [4-7]. Zhao et al. confined cation injection to enhance CBRAM performance by nano-pore graphene layer [8]. Although the reliability of the device has highly improved, it makes costs of difficulty on material control and cannot be used in a standard CMOS process. In order to address this problem, Gong et al. proposed a CMOS-compatible and self-aligned method to form a CuSiN interfacial layer in Cu electrode for improving the low-resistance state (LRS) retention [9]. Cao et al. proposed a TiN barrier layer to improve the device reliability in CBRAM devices by eliminating the nano-filament overgrowth phenomenon and negative-SET behavior [10]. The above methods utilized the bi-layer structure to optimize the reliability of CBRAM effectively. However, they make costs of complex process flow or programming speed.

In this work, we propose a CMOS-compatible method to form a bi-layer device by a simple low-temperature annealing process. The double-layer device of  ${\rm Ta_2O_5/TaO_x}$  structure was formed spontaneously, which shows better reliability characteristics compared with the un-annealed device. The enhanced reliability of the annealed device can be explained by the concentrated filaments formed along the grain boundary during programming. Furthermore, for a bi-layer annealing device, due to the existence of  ${\rm TaO_x}$ , the self-compliance behavior is achieved because the  ${\rm TaO_x}$  layer serves as a resistor in series with a  ${\rm Ta_2O_5}$ -resistive layer. This result provides a simple CMOS-compatible method to form a double-layer device and improve the reliability of CBRAM.

<sup>&</sup>lt;sup>1</sup>Key Laboratory of Microelectronics Devices and Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, Beijing, China Full list of author information is available at the end of the article

The W plug with a diameter of  $1 \mu m$  after CMP is served as the bottom electrode (BE). After depositing 5 nm Ta

<sup>\*</sup> Correspondence: xuxiaoxin@ime.ac.cn; lvhangbing@ime.ac.cn

Yu et al. Nanoscale Research Letters (2019) 14:111 Page 2 of 6

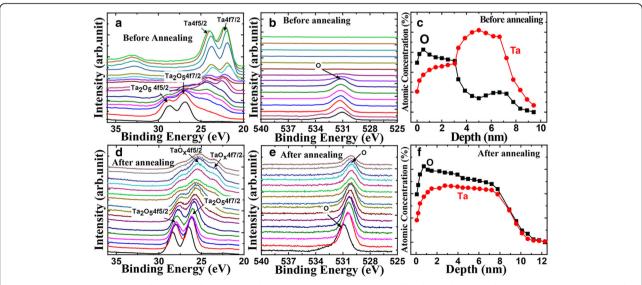

layer by DC magnetron sputtering, the Ta2O5 was formed through a thermal oxidation process, under 350 °C, in plasma O2 for 300 s by plasma-enhanced chemical vapor deposition (PECVD). Then, 40 nm Cu top electrode (TE) is sputtered and patterned by lithography. The memory cells are patterned through the etching process with a mixed gas of SF<sub>6</sub> and C<sub>3</sub>F<sub>8</sub> by using the TE as the hard mask. Afterward, the BE is extracted out by the Al pad. Finally, the device is completed with a CMOS-compatible low-temperature annealing process under 400 °C for 30 min. The size of the device is defined by the area of the bottom electrode, which is 1 µm<sup>2</sup>. As a reference, the device without the annealing process is also prepared. The electrical DC measurements are carried out by using a Keithley 4200-SCS semiconductor parameter analyzer. For all measurements, the voltage is applied to the Cu TE with the W BE grounded. For a profound insight into the annealing process, the composition and chemical bonding state in the Ta<sub>2</sub>O<sub>5</sub> films before and after annealing process are analyzed by X-ray photoelectron spectroscopy (XPS). The etch rate of the sample is 0.5 nm/point. In Fig. 1a, the peaks of Ta<sub>2</sub>O<sub>5</sub> 4f doublet with peak binding energies of  $26.70\,\text{eV}$  (Ta<sub>2</sub>O<sub>5</sub>  $4f_{7/2}$ ) and  $28.60 \,\mathrm{eV} \, (\mathrm{Ta}_2\mathrm{O}_5 \, 4\mathrm{f}_{5/2})$  with peak separation of 1.9 eV are observed at the surface [11-13]. This case demonstrates the existence of Ta<sub>2</sub>O<sub>5</sub> layer.

With the depth increasing, the peaks of  ${\rm Ta_2O_5}$  4f doublet disappear and the peaks at 22.33 eV, 23.96 eV corresponding to Ta  $4{\rm f_{7/2}}$ , Ta  $4{\rm f_{5/2}}$  appear. Figure 1b verifies that there is no O signal at the same depth where the Ta  $4{\rm f_{7/2}}$  and Ta  $4{\rm f_{5/2}}$  exist. In other words, there is metallic Ta on the surface of  ${\rm Ta_2O_5}$  for the un-annealed

device. The depths of the Ta2O5 and Ta analyzed from Fig. 1c are 4 nm and 2.5 nm, respectively. In addition, there is the peak of the O atomic concentration in the depth of 7 nm, indicating the existence of the absorbed oxygen. Figure 1d and e show the depth profiles of XPS spectra from the Ta<sub>2</sub>O<sub>5</sub> films after the annealing process. The peaks of Ta 4f doublet and Ta<sub>2</sub>O<sub>5</sub> 4f doublet exist together at a certain depth. The intensity of the Ta<sup>5+</sup> oxidation state gradually weakens with the increasing depth. Combined with the all-around oxygen signal along the film depth, we confirm that the TaOx exists on the surface of Ta2O5 [11, 14]. Calculated from Fig. 1f, the thickness of the  $Ta_2O_5$  is 4 nm and  $TaO_x$  is 3.5 nm. Therefore, the TaO<sub>x</sub> is formed by changing the adsorbed oxygen to lattice oxygen in the annealing process. The oxygen re-distribution would reach a saturation point saturated after the annealing process. The thickness of TaOx as well as the Forming voltage will not increase even though the annealing time increases, proving the large process margin of this annealing process.

Figure 2a and b are the resistive switching characteristics of Cu/Ta<sub>2</sub>O<sub>5</sub>/W before and after annealing under DC sweeping mode. The initial resistances ( $R_{\rm initial}$ ) of the two devices are both in high-resistance state (HRS) with values of  $\sim 10^9$   $\Omega$  and  $10^{10}$   $\Omega$ , respectively. The higher  $R_{\rm initial}$  of the annealed device is due to the thicker oxide film formed under thermal process. Notably, this device does not need a forming process, which is quite expected in practical application. For the un-annealed device, it switches to LRS abruptly when the applied voltage reached to a critical value during positive voltage sweeping. Some ultra-low LRS occurred during the set

Fig. 1 The XPS shows depth profile of Ta before (a) and after (d) annealing. b, e Depth profile of O before and after annealing, respectively. c, f Atomic concentration profile of O and Ta with depth before and after annealing, respectively

Yu et al. Nanoscale Research Letters (2019) 14:111 Page 3 of 6

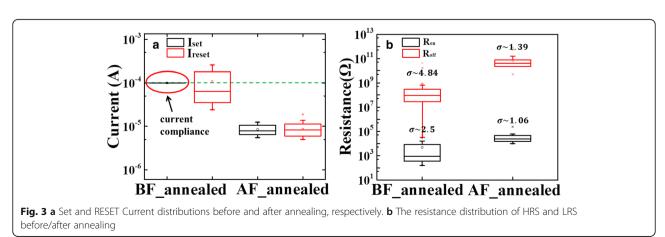

process. The RESET current in such case is much higher than the pre-set compliance current, indicating the overshoot phenomenon happened in this device. Figure 3b exhibits the unstable LRS and HRS within 200 cycles for the un-annealed device. The large variation between cycle-to-cycle leads to the memory window reduced to be as small as 20. Figure 2b shows the switching behavior of the annealed devices. The current flowing through the cell increases gradually and reaches the compliance current. No obvious switching point is observed, avoiding the overshoot phenomenon happened in the un-annealed devices. A memory window as high as  $10^4$  was achieved during the switching cycles, owing to the uniform distribution of HRS and LRS.

The suppression of the overset phenomenon in the annealed device could also be verified by the improved distribution of the RESET current ( $I_{\rm RESET}$ ) and Set current ( $I_{\rm Set}$ ) in the annealed device, as shown in the Fig. 3a. The  $I_{\rm Set}$  of the un-annealed device is stuck at the  $I_{\rm CC}$  but  $I_{\rm RESET}$  distributes widely. In contrast, for the annealed device, the  $I_{\rm RESET}$  is similar to  $I_{\rm Set}$ . The device-to-device uniformity is evaluated by analyzing the  $R_{\rm on}$  and  $R_{\rm off}$  in 20 different devices under DC mode. As shown in Fig. 3

(b), the  $R_{\rm on}$  extracted under  $V_{\rm read}$  of 0.1 V for the un-annealed device distributes from  $10^2\,\Omega$  to  $10^5\,\Omega$ , while the  $R_{\rm on}$  of the annealed device distributes from  $10^4\,\Omega$  to  $10^5\,\Omega$ . The relatively higher  $R_{\rm on}$  of the annealed device resulted from the series resistance of the  ${\rm TaO_x}$  layer. Moreover, the HRS distribution of the annealed device is also much improved. As shown in Fig. 3b, the standard deviation (SD) of  $R_{\rm off}$  is reduced from 4.84 to 1.39.

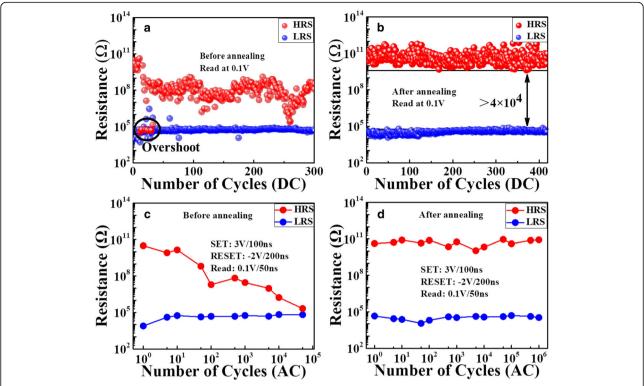

The cycling results under DC sweeping are shown in Fig. 4a and b. For the un-annealed device, the HRS/LRS ratio is around  $10^5$  at first, and then decreases gradually and finally sticks at LRS. Note that a few soft errors could be observed during cycling, in the form of HRS (red dots) and LRS (blue dots) run back and forth occasionally. For the annealed device, the HRS/LRS ratio remains stable ( $\sim 10^4$ ) without any degradation. During pulse measurements, the proper pulse programming conditions are optimized as 3 V/100 ns for set operation, -2 V/200 ns for RESET operation, and 0.1 V/50 ns for read operation. The sensing time for Set/RESET/Read operation is 15 ns/12 ns/25 ns, respectively. As can be seen from Fig. 4c, the endurance for the un-annealed device is

Yu et al. Nanoscale Research Letters (2019) 14:111 Page 4 of 6

**Fig. 4** The cycling results of **a** the devices without annealing under 300 DC cycles and **b** the devices with annealing under 400 DC cycles. **c, d** Endurance characteristics under AC mode with the optimized operation configuration: set 3 V/100 ns; RESET - 2 V/200 ns. Up to  $10^6$  cycles were obtained for the device after annealing

usually less than  $5 \times 10^4$  switching cycles. However, from Fig. 4d, it is surprising that the annealed device still works well without failure after more than  $10^6$  switching cycles. Based on our previous study [15], the endurance failure in CBRAM is related to the unstable RESET operation resulted from the filament overgrowth into the counter electrode. On the one hand, the overgrown filament needs more energy to rupture and tends to cause incomplete RESET and lower HRS. On the other hand, the overgrowth of filament into the counter electrode leads to residual Cu ions in the

counter electrode, which could serve as a reservoir of metal ions and make unexpected negative-SET. For the annealed device, the filament overgrowth is well suppressed by the incorporation of  ${\rm TaO_x}$  layer and results in more stable RESET operation. As a result, the memory window is well maintained and the cycling characteristic is much improved.

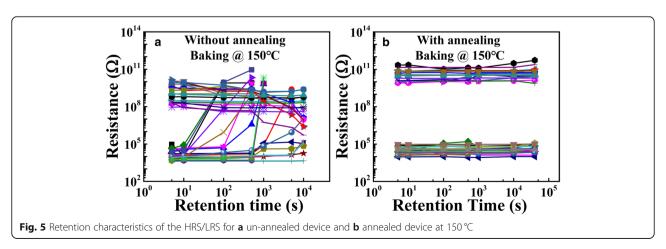

Considering the retention characteristic plays a crucial role for practical application of CBRAM [16]. The retention characteristics are measured under 150 °C using the vacuum oven. The resistance of each cell is checked after

Yu et al. Nanoscale Research Letters (2019) 14:111 Page 5 of 6

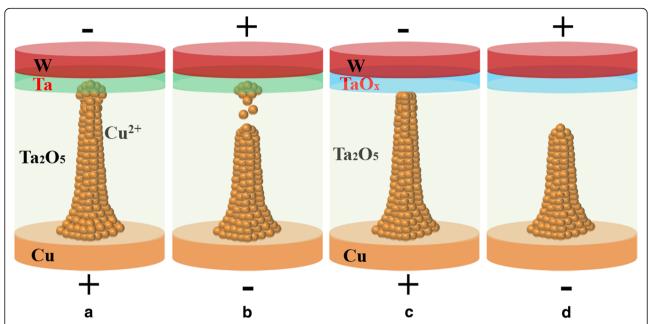

**Fig. 6** The physical modeling for the switching behavior of the annealed and un-annealed devices. The **a** Set and **b** RESET process for the un-annealed device with the structure of  $Cu/Ta_2O_5/Ta/W$ . **c** Set and **d** RESET process for the annealed device with the structure of  $Cu/Ta_2O_5/Ta/W$ . The filament overgrowth is suppressed by the  $TaO_x$  layer formed during the annealing process

cooling down to room temperature at every decade interval. Figure 5a and b show the dependence of the R<sub>HRS</sub>/R<sub>LRS</sub> on the baking time for the device without annealing and with annealing, respectively. For the un-annealed devices (Fig. 5a), as the time increases, the devices failed gradually within 10<sup>4</sup>s. However, for the annealed device (Fig. 5b), among the recorded 20 devices, the resistances of the LRS and HRS do not show any degradation as the baking time increases. That is to say, the retention of the devices is highly improved by the annealing process. The lifetime of the annealed device at 85 °C could be extracted as 10 years by Arrhenius plot, which is in good accordance to the CBRAMs reported [17, 18]. The achievement of better retention characteristic for the annealed device is because the annealing process recovers some defects in the switching film, which would slow down the diffusion of the Cu species.

Based on the above results, a physical model for the switching behavior of the annealed and un-annealed devices is illustrated in Fig. 6a–d. The filament growth in CBRAM is associated with the Cu ion transportation in the lattice of electrolyte [19]. The overshoot phenomenon that happened in the un-annealed device makes filament overgrowth into the counter electrode. During the RESET operation, the residual Cu ions stored in the counter electrode will drift into the tunnel gap between the filament tip and the counter electrode, resulting in the residual Cu<sup>+</sup> at the end of the RESET operation and serious variation of HRS. As the

diffusion coefficient of Cu in  ${\rm TaO_x}~(4.9\times 10^{-20}~{\rm cm^2/s})$  is much less than that in Ta  $(1.0\times 10^{-6}~{\rm cm^2/s})$ , the Cu diffuses into  ${\rm TaO_x}$  is much more difficult under the electric field during Set operation in the sample of Cu/Ta<sub>2</sub>O<sub>5</sub>/TaO<sub>x</sub>/W [20, 21]. Hence, the overset behavior and filament overgrowth could be well suppressed, and the RESET operation becomes more stable.

#### **Conclusions**

In this letter, we investigated the switching characteristics of a  ${\rm TaO_x}$ -based CBRAM device. A  ${\rm Ta_2O_5/TaO_x}$  bi-layer stack was formed after a post thermal annealing treatment. The  ${\rm TaO_x}$  layer could act as an external resistance suppressing the overflow current during set operation. Both HRS and LRS distribution are greatly improved due to the suppression of the overset phenomenon. Moreover, the data retention of the CBRAM is enhanced due to the recovery of defects in the switching film during thermal annealing. This work provides the most convenient and economical solution to achieve the bi-layer structure and improve the reliability of CBRAM.

#### Abbreviations

CBRAM: Conductive bridge random access memory; HRS: High-resistance states; LRS: Low-resistance states; NVM: Non-volatile memory; PECVD: Plasma-enhanced chemical vapor deposition; TE: Top electrode

#### Acknowledgements

Not applicable

Yu et al. Nanoscale Research Letters (2019) 14:111 Page 6 of 6

#### **Funding**

This work was supported in part by the MOST of China under Grants 2017YFA0206102, 2016YFA0203800, 2016YFA0201803, 2018YFB040163, 2018YFB0407502, and in part by the National Natural Science Foundation of China under Grants 61522408, 61521064, 61804173, 61804167, 61834009 and in part by Huawei Data Center Technology Laboratory.

#### Availability of data and materials

The datasets used during the current study are available from the corresponding author of this article.

#### Authors' contributions

JY and TG prepared the samples and electrical measurements. JY and XX contributed to the design and experimental results analyzing and wrote the manuscript. QL, DD, PY, LT, JY, XZ, XW, HL, and ML provide technical support to study. All authors read and approved the final manuscript.

#### Competing interests

The authors declare that they have no competing interests.

#### **Publisher's Note**

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

#### **Author details**

<sup>1</sup>Key Laboratory of Microelectronics Devices and Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, Beijing, China. <sup>2</sup>School of Electronics and Information Engineering, Anhui University, Hefei, Anhui, China.

#### Received: 10 December 2018 Accepted: 14 March 2019 Published online: 28 March 2019

#### References

- Waser R, Aono M (2007) Nanoionics-based resistive switching memories. Nature Mater 6:833–840. https://doi.org/10.1038/nm1t2023

- Waser R, Dittmann R, Staikov G, Szot K (2009) Redox-based resistive switching memories—nanoionic mechanisms, prospects, and challenges. Adv Mater 21:2632–2663. https://doi.org/10.1002/adma.200900375

- Jameson JR, Blanchard P, Cheng C, Dinh J, Gallo A, Gopalakrishnan V, Gopalan C, Guichet B, Hsu S, Kamalanathan D, Kim D, Koushan F, Kwan M, Law K, Lewis D, Ma Y, McCaffrey V, Park S, Puthenthermadam S, Runnion E, Sanchez J, Shields J, Tsai K, Tysdal A, Wang D, Williams R, Kozicki MN, Wang J, Gopinath V, Hollmer S, Buskirk MV (2013) Conductive-bridge memory (CBRAM) with excellent high-temperature retention. In: Electron Devices Meeting (IEDM), pp 9–11. https://doi.org/ 10.1109/IEDM.2013.6724721

- Choi BJ, Jeong DS, Kim SK, Rohde C, Choi S, Oh JH, Kim HJ, Hwang CS, Szot K, Waser R, Reichenberg B, Tiedke S (2005) Resistive switching mechanism of TiO<sub>2</sub> thin films grown by atomic-layer deposition. J Appl Phys 98:033715. https://doi.org/10.1063/1.2001146

- Chen B, Lu Y, Gao B, Fu YH, Zhang FF, Huang P, Chen YS, Liu LF, Liu XY, Kang JF, Wang YY, Fang Z, Yu HY, Li X, Wang XP, Singh N, Lo GQ, Kwong DL (2011) Physical mechanisms of endurance degradation in TMO-RRAM. IEEE Electron Device Lett:12.3.1–12.3.4. https://doi.org/10.1109/IEDM.2011.6131539

- Wei Z, Takagi T, Kanzawa Y, Katoh Y, Ninomiya T, Kawai K, Muraoka S, Mitani S, Katayama K, Fujii S, Miyanaga R, Kawashima Y, Mikawa T, Shimakawa K, Aono K (2011) Demonstration of high-density ReRAM ensuring 10-year retention at 85 °C based on a newly developed reliability model. IEEE Electron Device Lett:31.4.1–31.4.4. https://doi.org/ 10.1109/IEDM.2011.6131650

- Ninomiya T, Wei Z, Muraoka S, Yasuhara R, Katayama K, Takagi T (2013) Conductive filament scaling of TaO<sub>x</sub> bipolar ReRAM for improving data retention under low operation current. IEEE Transactions Electron Devices 60:1384–1389. https://doi.org/10.1109/TED.2013.2248157

- Zhao X, Liu S, Niu J, Liao L, Liu Q, Xiao X, Lv H, Long S, Banerjee W, Li W, Si S, Liu M (2017) Confining cation injection to enhance CBRAM performance by nanopore graphene layer. Small 13:160348(1–9). https://doi.org/10.1002/smll.201603948

- Gong TC, Luo Q, Xu XX, Yuan P, Ma HL, Chen C, Liu Q, Long SB, Lv HB, Liu M (2017) Uniformity and retention improvement of TaO<sub>x</sub> based conductive bridge random access memory by CuSiN interfacial layer engineering. IEEE Electron Device Lett 38:1232–1235. https://doi.org/10. 1109/LED.2017.2734907

- Cao R, Liu S, Liu Q, Zhao X, Wang W, Zhang X, Wu F, Wu Q, Wang Y, Lv HB, Long SB, Liu M (2015) Improvement of device reliability by introducing a BEOL-compatible TiN barrier layer in CBRAM. IEEE Electron Device Lett 36:129–131. https://doi.org/10.1109/LED.2017.2746738

- Lee CB, Lee DS, Benayad A, Lee SR, Chang M, Lee MJ, Hur J, Kim YB, Kim CJ, Chung UI (2011) Highly uniform switching of tantalum embedded amorphous oxide using self-compliance bipolar resistive switching. IEEE Electron Device Lett 32:399–401. https://doi.org/10.1109/ IEED.2010.2101044

- 12. Chen YC, Chung YL, Chen BT, Chen WC, Chen JS (2013) Revelation on the interrelated mechanism of polarity-dependent and multilevel resistive switching in TaOx-based memory devices. J Phys Chem C 117: 5758–5764. https://doi.org/10.1021/jp311951e

- Prakash A, Maikap S, Lai CS, Tien TC, Chen WS, Lee HY, Chen FT, Kao MJ, Tsai MJ (2012) Bipolar resistive switching memory using bilayer TaOx/WOx films. Solid State Electron 77:35–40. https://doi.org/10.1016/j.sse.2012.05.028

- Lee MJ, Lee CB, Lee D, Lee SR, Chang M, Hur JH, Kim YB, Kim CJ, Seo DH, Seo S, Chung UI, Yoo IK, Kim K (2011) A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>2-x</sub> bilayer structures. Nat Mater 10:625–630. https://doi.org/10.1038/nmat3070

- Lv HB, Wan H, Tang T (2010) Improvement of resistive switching uniformity by introducing a thin GST interface layer. IEEE Electron Device Lett 31:978– 980. https://doi.org/10.1109/LED.2010.2055534

- Liu H, Lv HB, Yang B, Xu XX, Liu R, Liu Q, Long SB, Liu M (2014) Uniformity improvement in 1T1R RRAM with gate voltage ramp programming. IEEE Electron Device Lett 35:1224–1226. https://doi.org/10.1109/LED.2014. 2364171

- Sakamoto T, Tada M, Banno N, Tsuji Y, Saitoh Y, Yabe Y, Hada H, Iguchi N, Aono M (2009) Nonvolatile solid-electrolyte switch embedded into Cu interconnect. In: Symposium on VLSI Technology. IEEE. https://doi.org/10. 1109/VLSI.2009.5200660

- Xu XX, Lv HB, Liu HT, Gong TC, Wang GM, Zhang MY, Li Y, Liu Q, Long SB, Liu M (2015) Superior retention of low-resistance state in conductive bridge random access memory with single filament formation. IEEE Electron Device Lett 36(2):129–131. https://doi.org/10. 1109/LED.2014.2379961

- Lv HB, Xu XX, Sun PX, Liu HT, Luo Q, Liu Q, Banerjee W, Sun HT, Long SB, Li L, Liu M (2015) Atomic view of filament growth in electrochemical memristive elements. Sci Rep 5:13311. https://doi.org/ 10.1038/srep13311

- Banno N, Sakamoto T, Iguchi N, Sunamura H, Terabe K, Hasegawa T, Aono M (2008) Diffusivity of Cu ions in solid electrolyte and its effect on the performance of nanometer-scale switch. IEEE Transactions Electron Devices 55: 3283–3287. https://doi.org/10.1109/TED.2008.2004246

- Manhas SK, Singh N, Lo GQ (2011) Barrier layer thickness analysis for reliable copper plug process in CMOS technology. Microelectronics Reliablity 51:1365–1371. https://doi.org/10.1016/j.microrel.2011.03.005

## Submit your manuscript to a SpringerOpen journal and benefit from:

- ► Convenient online submission

- Rigorous peer review

- ► Open access: articles freely available online

- ► High visibility within the field

- ► Retaining the copyright to your article

Submit your next manuscript at ▶ springeropen.com