## NANO EXPRESS

**Open Access**

Interfacial, Electrical, and Band Alignment Characteristics of HfO<sub>2</sub>/Ge Stacks with In Situ-Formed SiO<sub>2</sub> Interlayer by Plasma-Enhanced Atomic Layer Deposition

Yan-Qiang Cao<sup>\*</sup>, Bing Wu, Di Wu and Ai-Dong Li<sup>\*</sup>

### Abstract

In situ-formed SiO<sub>2</sub> was introduced into HfO<sub>2</sub> gate dielectrics on Ge substrate as interlayer by plasma-enhanced atomic layer deposition (PEALD). The interfacial, electrical, and band alignment characteristics of the HfO<sub>2</sub>/SiO<sub>2</sub> high-k gate dielectric stacks on Ge have been well investigated. It has been demonstrated that Si-O-Ge interlayer is formed on Ge surface during the in situ PEALD SiO<sub>2</sub> deposition process. This interlayer shows fantastic thermal stability during annealing without obvious Hf-silicates formation. In addition, it can also suppress the GeO<sub>2</sub> degradation. The electrical measurements show that capacitance equivalent thickness of 1.53 nm and a leakage current density of 2.  $1 \times 10^{-3}$  A/cm<sup>2</sup> at gate bias of V<sub>fb</sub> + 1 V was obtained for the annealed sample. The conduction (valence) band offsets at the HfO<sub>2</sub>/SiO<sub>2</sub>/Ge interface with and without PDA are found to be 2.24 (2.69) and 2.48 (2.45) eV, respectively. These results indicate that in situ PEALD SiO<sub>2</sub> may be a promising interfacial control layer for the realization of high-quality Ge-based transistor devices. Moreover, it can be demonstrated that PEALD is a much more powerful technology for ultrathin interfacial control layer deposition than MOCVD.

## Background

With the continuous scaling down of metal-oxidesemiconductor field-effect transistors (MOSFETs), Sibased MOSFET is approaching its physical and technical limitation. Alternative channel materials such as germanium (Ge) [1, 2] and III-V materials [3–5] have recently attracted a great deal of interest for high-performance logic device applications. Among them, Ge has the potential to replace silicon as the channel material in MOSFET because of its intrinsic higher hole carrier mobility [6]. However, direct deposition of high-k gate dielectrics on Ge substrates often causes high interface trap density (D<sub>it</sub>) and the unwanted formation of interfacial layer between Ge and high-k dielectrics layers [7]. Therefore, in order to achieve high-speed and lowpower Ge-based MOSFETs, it is very important to achieve a high-quality high-k/Ge interface. Fortunately, a lot of methods have been reported to improve the quality of high-k/Ge interface [8], such as the introduction of SiO<sub>2</sub> [9], Si [10], GeO<sub>2</sub> [11], Al<sub>2</sub>O<sub>3</sub> [12, 13], GeO<sub>x</sub>N<sub>y</sub> [14, 15], and rare earth oxides [16, 17] as the interfacial control layer between Ge substrate and high-k gate dielectrics. In particular, the GeO<sub>2</sub>/Ge structure has superior interface properties, an extremely low interface state density (D<sub>it</sub>) of less than  $1 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> can be achieved [18]. However, GeO<sub>2</sub> would decompose above 425 °C, and it is soluble in water. As a result, an unacceptable D<sub>it</sub> is always revealed for the Ge-MOS capacitor (MOSCAP) [6]. Fortunately, Kita et al. reported that capping layer on GeO<sub>2</sub> can suppress the GeO<sub>2</sub> degradation; however, the selection of the material for the cap layer should be very crucial [19-21]. For example, Si or Y<sub>2</sub>O<sub>3</sub> works more efficiently than HfO<sub>2</sub> to retard the Ge-O desorption. These results indicate the importance of high-k materials or interfacial control layer selection to inhibit the GeO<sub>2</sub> degradation. Nakashima et al. reported that a very thin SiO<sub>2</sub>/GeO<sub>2</sub> bilayer by physical vapor deposition (PVD) is a promising interlayer layer

© The Author(s). 2017 **Open Access** This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

<sup>\*</sup> Correspondence: 648779387@qq.com; adli@nju.edu.cn National Laboratory of Solid State Microstructures and Department of Materials Science and Engineering, College of Engineering and Applied sciences, Collaborative Innovation Center of Advanced Microstructures, Nanjing University, Nanjing 210093, People's Republic of China

for Ge passivation, a  $D_{it}$  of  $4 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> was achieved near the midgap [22, 23]. Li et al. introduced the SiO<sub>2</sub> interlayer on Ge by metal-organic chemical vapor deposition (MOCVD), and SiO<sub>2</sub> interlayer can effectively suppress Ge out-diffusion during HfO<sub>2</sub> growth and subsequent post-deposition annealing process [9]. Therefore, SiO<sub>2</sub> should be a wonderful interfacial control layer for Ge substrate. However, compared to PVD and MOCVD, PEALD can provide a much more uniform passivation layer, especially for ultrathin thickness. Hence, PEALD-formed SiO<sub>2</sub> may be a promising interfacial control layer to achieve high-performance Gebased transistor devices.

Herein, we introduced in situ PEALD-formed SiO<sub>2</sub> into HfO<sub>2</sub>/Ge stacks as interfacial layer. The interfacial, electrical, and band alignment characteristics of ALD HfO<sub>2</sub> films on n-type Ge substrates have been investigated carefully. The SiO<sub>2</sub> was first deposited on the Ge substrates as interfacial control layer by PEALD. Then, HfO2 gate dielectric was in situ deposited by thermal ALD mode. Post-deposition annealing (PDA) at 500 °C for 60 s in N<sub>2</sub> was performed for the HfO<sub>2</sub>/SiO<sub>2</sub> high-k gate dielectric stacks on Ge. The X-ray photoelectron spectroscopy analyses reveal that Si-O-Ge interlayer and GeO<sub>2</sub> layer is formed on the Ge surface during PEALD SiO<sub>2</sub> deposition. This Si-O-Ge interlayer not only shows fantastic thermal stability, but also it can suppress the thermal decomposition of GeO<sub>2</sub>. Therefore, good electrical properties were achieved for the HfO<sub>2</sub>/Si-O-Ge/ GeO<sub>2</sub>/Ge stacks. Compared to MOCVD SiO<sub>2</sub> interlayer, in situ PEALD SiO<sub>2</sub> exhibits much improved electrical properties. Therefore, PEALD is a much more powerful technology than MOCVD in the area of MOSFETs fabrication, especially for ultrathin interfacial control layer deposition.

#### Methods

N-type Sb-doped Ge (100) with a resistivity of 0.2-0.3  $\Omega$ ·cm were used as substrates. The substrates were firstly cleaned by sonication in acetone, ethanol, isopropanol, and deionized water for 5 min, respectively. Then, a dilute HBr solution  $(H_2O/HBr = 3:1)$  was used to etch the surface native oxides for 5 min. After wet chemical cleaning, the substrates were rinsed with deionized water and blown dry in pure N<sub>2</sub>. Subsequently, the substrates were immediately transferred to the PEALD (Picosun SUNALE<sup>TM</sup> R-200) chamber. Before the high-k HfO<sub>2</sub> films deposition, 10 cycles SiO<sub>2</sub> film was deposited at 250 °C by PEALD as interlayer, where one cycle consisted of 1 s Si source injection, 10 s  $N_2$  purging, 13.5 s oxidant injection, and 4 s N2 purging. Tris-(dimethylamino)-silane (TDMAS) and O2 plasma were used as Si precursor and oxidant for SiO<sub>2</sub> deposition, respectively. TDMAS was kept at room temperature. Pure  $O_2$  gas (99.999%) was used as  $O_2$  plasma source. The plasma power and  $O_2$  gas flow rate were 2500 W and 160 sccm, respectively. The growth rate of PEALD SiO<sub>2</sub> was determined to be ~0.7 Å/cycle by ex situ spectroscopy ellipsometry. Then ~4 nm-thick HfO<sub>2</sub> film was in situ deposited at 250 °C for 40 cycles by thermal ALD, where one cycle consisted of 0.1 s Hf source dosing, 4 s N<sub>2</sub> purging, 0.1 s H<sub>2</sub>O dosing, and 4 s N<sub>2</sub> purging. Tetrakis-(ethylmethylamino)-hafnium (TEMAH) and H<sub>2</sub>O were used as Hf precursor and oxidant for HfO<sub>2</sub> deposition, respectively. TEMAH was evaporated at 150 °C and H<sub>2</sub>O was kept at room temperature. Pure N<sub>2</sub> (99.999%) was used as carrier gas and purge gas. PDA was performed in N<sub>2</sub> ambient at 500 °C for 60 s under atmospheric pressure using rapid thermal annealing.

The interfacial structures and chemical bonding of the films were investigated by ex situ X-ray photoelectron spectroscopy (XPS, Thermo Fisher K-Alpha) with standard Al K $\alpha$  (1486.7 eV) X-ray source. XPS spectra were collected at a takeoff angle of 90°. The binding energy scale was calibrated using the Ge  $3d_{5/2}$  peak at 29.4 eV. In addition, XPS spectra were fitted with Gaussian-Lorentzian (G-L) functions after smart-type background subtraction. Pt top electrodes of area  $1.55 \times 10^{-4}$  cm<sup>2</sup> were deposited on the surface of HfO<sub>2</sub> films using a shadow mask by sputtering method for electrical measurements. The capacitance-voltage (C-V) and leakage current density-voltage (J-V) characteristics were measured by a Keithley 4200 semiconductor analyzer system with a probe platform (Cascade summit 12000B-M).

#### **Results and Discussion**

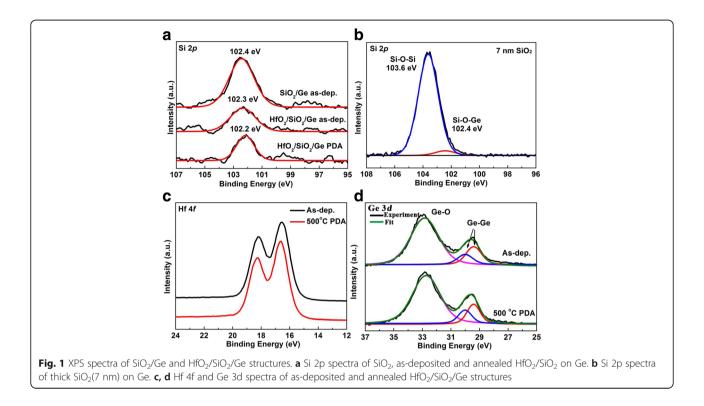

For the thin PEALD SiO<sub>2</sub> (~0.7 nm) on Ge, Si 2p exhibits a peak at 102.4 eV corresponding to Si-O bond (Fig. 1a), which is smaller than binding energy of ideal SiO<sub>2</sub> [24]. Both silicon suboxide (SiO<sub>x</sub>) deposition and Si-O-Ge formation on Ge surface during PEALD process can cause the Si 2p shift to lower energy. Therefore, Si 2p spectrum of thick PEALD (~7 nm) on Ge was also performed. It can be found that it exhibits a main peak at 103.6 eV corresponding to ideal SiO<sub>2</sub> bonding, as shown Fig. 1b. So, the silicon oxide deposited by PEALD here is ideal SiO<sub>2</sub>. However, besides the strong Si-O-Si peak, there is a weak peak located at ~102.4 eV, which should correspond to Si-O-Ge bonding on Ge surface. Therefore, it can be concluded that Si-O-Ge is formed on Ge surface in the initial PEALD SiO<sub>2</sub> growth. After in situ 4 nm HfO<sub>2</sub> deposition, the Si 2p peak intensity decreases without obvious chemical shift (102.3 eV), as shown in Fig. 1a. Furthermore, the Si 2p peak also exhibits no evident chemical shift (102.2 eV) after the 500 °C PDA in N<sub>2</sub>, suggesting the good thermal stability of the HfO<sub>2</sub>/SiO<sub>2</sub> interface during HfO<sub>2</sub> deposition and PDA process. In Hf 4f spectrum of as-deposited HfO<sub>2</sub>/

$SiO_2$  gate stacks (Fig. 1c), the doublet at 16.5 and 18.2 eV can be assigned to Hf  $4f_{7/2}$  and Hf  $4f_{5/2}$  peaks of  $HfO_2$  with the spin orbit splitting energy of 1.7 eV, consistent with the literature value of HfO<sub>2</sub> [25]. After 500 ° C PDA, the Hf 4f spectrum shows no obvious change with only 0.1 eV shift to higher energy. It implies that there are no evident Hf-silicates formed during PDA process. In Fig. 1d, the Ge 3d spectrum of as-deposited sample displays the doublet peaks at 29.4 and 30.0 eV, which can be assigned to the Ge 3d5/2 and Ge 3d3/2 peaks of Ge substrate with the spin orbit splitting energy of 0.6 eV. Except the signal of Ge substrate, there is a huge peak at 32.7 eV for Ge-O bonding. The Ge-O peak should be resulted from the formation of Ge-O-Si and GeO<sub>2</sub>. The GeO<sub>2</sub> layer was formed by surface oxygen plasma oxidation during PEALD SiO<sub>2</sub> deposition process. Therefore, the real fabricated structure here is HfO2/Si-O-Ge/GeO2/Ge stacks. Moreover, the Ge 3d spectrum shows no evident change after 500 °C PDA treatment, indicating the thermal stability of HfO<sub>2</sub>/Si-O-Ge/GeO<sub>2</sub>/Ge stacks without GeO<sub>2</sub> degradation. It has been reported by Kita et al. that some capping layers on GeO<sub>2</sub> could suppress the GeO<sub>2</sub> decomposition, such as Si or  $La_2O_3$  [19]. Therefore, the PEALD induced the Si-O-Ge interlayer here can also suppress the GeO<sub>2</sub> decomposition. Based on above XPS analysis, it can be concluded that an ultrathin Si-O-Ge interlayer is formed on Ge surface. Moreover, this interlayer exhibits fantastic thermal stability without Hf-silicates formation, it can also inhibit the GeO<sub>2</sub> degradation.

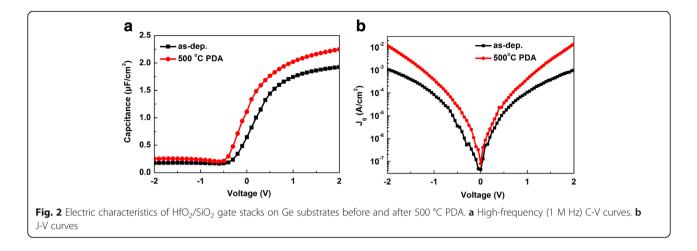

Figure 2a plots the high-frequency (1 MHz) C-V curves of HfO<sub>2</sub>/SiO<sub>2</sub> gate stacks on Ge before and after PDA. It can be found that flat band voltage ( $V_{\rm fb}$ ) values of HfO2/SiO2/Ge before and after PDA are 0.42 and 0.27 V, respectively. The calculated ideal  $V_{\rm fb}$  value is 0.55 V. The slightly negative  $V_{\rm fb}$  shift indicates positive fixed charges, which may be induced by the oxygen vacancies in the dielectrics [26, 27]. During the inert atmosphere annealing process, more oxygen vacancies may be induced, resulting in a slightly negative  $V_{\rm fb}$  shift. It has been demonstrated in many reported literatures that the GeO<sub>2</sub> degradation during the annealing will cause the positive  $V_{\rm fb}$  shift. The desorption process of Ge-O is believed to generate additional negative charges [28, 29]. Therefore, it can also be concluded that  $GeO_2$ decomposition is suppressed by Ge-O-Si interlayer from  $V_{\rm fb}$  shift. The accumulation capacitance evidently increases from the original 1.92 to 2.25  $\mu$ F/cm<sup>2</sup> after PDA. The corresponding capacitance equivalent thickness (CET) values of the MOS capacitors can be calculated from the accumulation capacitances of the C-V curves using  $\varepsilon_0 \varepsilon_r A/C_{acc}$  [30]. Therefore, a smaller CET of 1.53 nm is obtained after PDA compared to as-deposited sample of 1.80 nm. It can be ascribed to the fact that a denser and thinner high-k layer can be acquired after PDA process. Figure 2b shows the leakage current characteristics of HfO2/SiO2 films on Ge before and after PDA. At the bias voltage of  $V_{\rm fb}$  + 1 V, the leakage current density is  $2.1 \times 10^{-3}$  A/cm<sup>2</sup> and  $2.2 \times 10^{-4}$  A/cm<sup>2</sup> for the

sample before and after PDA, respectively. The increased leakage current density after PDA can be also attributed to the decrease of the gate dielectrics thickness.

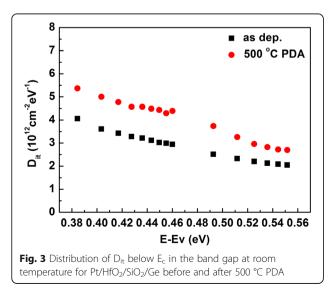

In order to examine the interface quality of HfO<sub>2</sub>/  $SiO_2/Ge$  quantitatively, the interface state density ( $D_{it}$ ) was determined by the conductance method [31]. Figure 3 shows the distribution of  $D_{it}$  below  $E_c$  in the band gap extracted by the conductance method at room temperature for Pt/HfO2/SiO2/Ge before and after 500 ° C PDA. The  $D_{it}$  can be roughly calculated from  $D_{it}$  =  $2.5 \times (G_p/w)_{max}/Aq$ , where  $(G_p/w)_{max}$  is the peak value of conductance-voltage characteristics,  $f(=w/2\pi)$  is the frequency, A is the electrode area, and q is the elemental charge. Therefore, Dit values of Pt/HfO2/SiO2/Ge structures without and with PDA are determined to be  $4.05\,\times$  $10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$  and  $5.37 \times 10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$  at  $\text{E-E}_{v}$  = 0.38 eV, respectively. The lower  $D_{\rm it}$  values of  $2.03 \times$  $10^{12} \text{ cm}^{-2} \text{eV}^{-1}$  and  $2.67 \times 10^{12} \text{ cm}^{-2} \text{eV}^{-1}$  near the bottom of conduction band are observed for the samples without and with PDA, respectively.

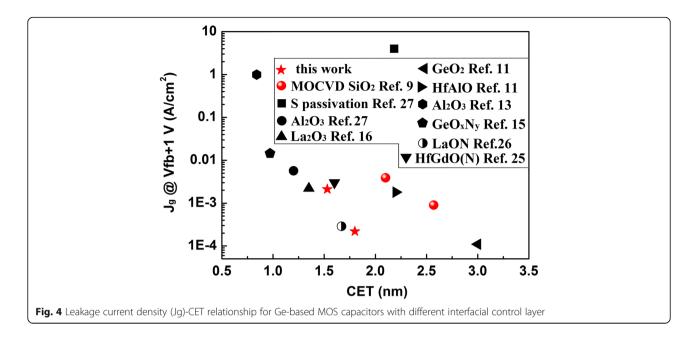

Figure 4 illustrates the leakage current density  $(J_{\sigma})$ -CET relationship of Ge-based MOS capacitor with different interfacial control laver [32, 33]. Compared to the S-passivated Ge without interlayer reported by our previous work [34], the HfO<sub>2</sub>/SiO<sub>2</sub>/Ge in this work exhibits much improved properties with smaller CET (1.53 vs 2.18 nm), leakage current density  $(2.1 \times 10^{-3} \text{ vs } 3.1 \text{ A})$ cm<sup>2</sup>), and  $D_{it}$  (4.37 × 10<sup>12</sup> vs 8.61 × 10<sup>12</sup> eV<sup>-1</sup> cm<sup>-2</sup>). It implies that in situ PEALD-formed SiO<sub>2</sub> is a wonderful passivation layer for Ge. Moreover, compared to the ex situ-formed SiO<sub>2</sub> interlayer by MOCVD [9], the sample with in situ PEALD-formed SiO<sub>2</sub> interlayer in this work shows better electrical performance with both smaller CET (1.53 vs 1.75 nm) and leakage current density (2.1 vs 3.9 mA/cm<sup>2</sup>). It can be ascribed to the fact that  $SiO_2$  deposited by PEALD are more uniform than MOCVD especially for ultrathin thickness.

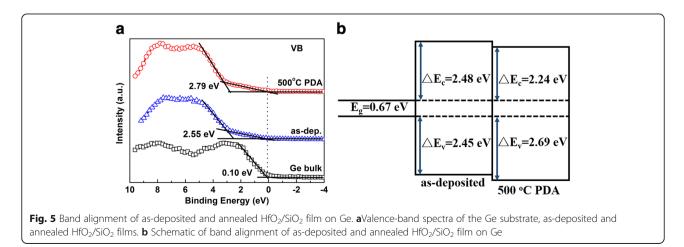

The band alignment at HfO<sub>2</sub>/SiO<sub>2</sub>/Ge interface was also determined by measuring the valence band offset  $\Delta E_{\nu}$  (VBO) using XPS. The VBO values can be obtained based on the assumption that the energy difference between the core level and the valence band (VB) edge of the substrate remains constant with/without the deposition of dielectrics films [35]. Here, the Ge substrate was chosen as the reference to determine the VBO between gate dielectrics stack and Ge substrate. Figure 5a presents the VB spectra of the clean Ge substrate, as-deposited and annealed HfO<sub>2</sub>/SiO<sub>2</sub>/Ge stacks determined by linear extrapolation method, respectively. The VB edge of the clean Ge substrate has been determined to be 0.10 eV. And, the VB edges of as-deposited and annealed HfO<sub>2</sub>/SiO<sub>2</sub> samples are found to be 2.55 and 2.79 eV, respectively. It can be noticed that there is a small tail in VB spectra for HfO<sub>2</sub>/SiO<sub>2</sub>/Ge stacks, which is corresponding to Ge substrate signal [36]. The leading edge of this weak tail is measured to be 0.10 eV and the same as the VB edge of Ge substrate. Therefore, the VBOs at the interface of HfO<sub>2</sub>/SiO<sub>2</sub>/Ge with and without PDA are estimated to be

2.69 and 2.45 eV, respectively. The conduction-band offset  $\Delta E_c$  (CBO) can be obtained by subtracting the VBO and the bandgap of the substrate from the bandgap of HfO<sub>2</sub>:

$$\Delta E_c = E_g(\mathrm{HfO}_2) - E_g(\mathrm{Ge}) - \Delta E_v,$$

where  $E_g(HfO_2)$  and  $E_g(Ge)$  are the bandgap of  $HfO_2$ and Ge, respectively. The bandgaps of Ge and  $HfO_2$  are 0.67 and 5.6 eV, respectively. Therefore, the CBO values at the interface of  $HfO_2/SiO_2/Ge$  with and without PDA are estimated to be 2.24 and 2.48 eV, respectively. The CBO values are consistent with the previously reported data of 1.8–2.6 eV [37]. Figure 5b illustrates the corresponding band alignment of as-deposited and annealed  $HfO_2/SiO_2/Ge$  structures. Evidently, the  $HfO_2/SiO_2$ high-k gate dielectric stacks on Ge exhibit large VBO and CBO values with huge barrier heights to inhibit leakage current.

#### Conclusions

In summary, SiO<sub>2</sub> interlayer was introduced into HfO<sub>2</sub> gate dielectrics on n-Ge substrates successfully by in situ PEALD. We have investigated the interfacial, electrical properties, and band alignment of HfO<sub>2</sub>/SiO<sub>2</sub>/Ge MOS. It has been demonstrated that Ge-O-Si interlayer and GeO<sub>2</sub> layer is formed on Ge surface during the in situ SiO<sub>2</sub> deposition. This Ge-O-Si interlayer shows fantastic thermal stability during PDA without Hf-silicates formation. Moreover, Ge-O-Si interlayer can also inhibit the GeO<sub>2</sub> degradation during annealing process. The HfO<sub>2</sub>/SiO<sub>2</sub>/Ge sample after PDA exhibits a CET value of 1.53 nm with low leakage current density of  $2.1 \times 10^{-3}$  A/cm<sup>2</sup> at V<sub>fb</sub> + 1 V. The VBO values at the HfO<sub>2</sub>/SiO<sub>2</sub>/Ge

with and without PDA are determined to be 2.69 and 2.45 eV, and the CBO values to be 2.24 and 2.48 eV, respectively. Compared to the ex situ-formed  $SiO_2$  interlayer by MOCVD, the sample with in situ PEALD-formed  $SiO_2$  interlayer in this work shows improved electrical performance, ascribed to the fact that  $SiO_2$  deposited by PEALD are more uniform than MOCVD. Therefore, PEALD is a much more powerful technology for ultrathin interfacial control layer deposition than MOCVD.

#### Acknowledgements

This project is supported by the Natural Science Foundation of China and Jiangsu Province (51571111 and BK2016230), a grant from the State Key Program for Basic Research of China (2015CB921203).

#### Authors' Contributions

YQC and BW carried out the sample fabrication and device measurements. YQC and BW did the data analysis and interpreted the results. ADL and DW participated in the discussion of results. YQC drafted the manuscript. ADL supervised the whole work and revised the manuscript. All authors critically read and commented on the manuscript. All authors read and approved the final manuscript.

#### **Competing Interests**

The authors declare that they have no competing interests.

#### **Publisher's Note**

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

#### Received: 16 March 2017 Accepted: 13 April 2017 Published online: 25 May 2017

#### References

- Lee ML, Leitz CW, Cheng Z, Pitera AJ, Langdo T, Currie MT et al (2001) Strained Ge channel p-type metal-oxide-semiconductor field-effect transistors grown on Si<sub>1-x</sub>Ge<sub>x</sub>/Si virtual substrates. Appl Phys Lett 79(20): 3344–6

- Chui CO, Ito F, Saraswat KC (2006) Nanoscale germanium MOS dielectricspart I: Germanium oxynitrides. Electron Devices IEEE Trans 53(7):1501–8

- Ye PD, Wilk GD, Yang B, Kwo J, Chu SNG, Nakahara S et al (2003) GaAs metal-oxide-semiconductor field-effect transistor with nanometer-thin dielectric grown by atomic layer deposition. Appl Phys Lett 83(1):180–2

- de Souza JP, Kiewra E, Sun Y, Callegari A, Sadana DK, Shahidi G et al (2008) Inversion mode n-channel GaAs field effect transistor with high-k/metal gate. Appl Phys Lett 92(15):153508

- Molle A, Spiga S, Andreozzi A, Fanciulli M, Brammertz G, Meuris M (2008) Structure and interface bonding of GeO<sub>2</sub>/Ge/In<sub>0.15</sub>Ga<sub>0.85</sub>As heterostructures. Appl Phys Lett 93(13):133504

- Kamata Y (2008) High-k/Ge MOSFETs for future nanoelectronics. Mater Today 11(1-2):30–8

- Caymax M, Van Elshocht S, Houssa M, Delabie A, Conard T, Meuris M et al (2006) HfO<sub>2</sub> as gate dielectric on Ge: Interfaces and deposition techniques. Mater Sci Eng B 135(3):256–60

- Xie Q, Deng S, Schaekers M, Lin D, Caymax M, Delabie A et al (2012) Germanium surface passivation and atomic layer deposition of high-k dielectrics-a tutorial review on Ge-based MOS capacitors. Semicond Sci Technol 27(7):1528–30

- Li XF, Liu XJ, Fu YY, Li AD, Zhang WQ, Li H et al (2012) Effect of annealing on interfacial and band alignment characteristics of HfO<sub>2</sub>/SiO<sub>2</sub> gate stacks on Ge substrates. J Vacuum Sci Technol B 30(1):010602

- Taoka N, Harada M, Yamashita Y, Yamamoto T, Sugiyama N, Takagi S-i (2008) Effects of Si passivation on Ge metal-insulator-semiconductor interface properties and inversion-layer hole mobility. Appl Phys Lett 92(11):113511

- 11. Li XF, Liu XJ, Zhang WQ, Fu YY, Li AD, Li H, et al (2011) Comparison of the interfacial and electrical properties of HfAlO films on Ge with S and  $GeO_2$  passivation. Appl Phys Lett 98(16):162903.

- Zhang L, Li H, Guo Y, Tang K, Woicik J, Robertson J et al (2015) Selective passivation of GeO<sub>2</sub>/Ge interface defects in atomic layer deposited high-k MOS structures. ACS Appl Mater Interfaces 7(37):20499–506

- Asahara R, Hideshima I, Oka H, Minoura Y, Ogawa S, Yoshigoe A et al (2015) Comprehensive study and design of scaled metal/high-k/Ge gate stacks with ultrathin aluminum oxide interlayers. Appl Phys Lett 106(23): 15–4

- Xie Q, Musschoot J, Schaekers M, Caymax M, Delabie A, Qu XP et al (2010) Ultrathin GeO<sub>x</sub>N<sub>y</sub> interlayer formed by in situ NH<sub>3</sub> plasma pretreatment for passivation of germanium metal-oxide-semiconductor devices. Appl Phys Lett 97(22):2902

- 15. Cao YQ, Chen J, Liu XJ, Li X, Cao ZY, Ma YJ et al (2015)  $HfO_2/GeO_xN_y/Ge$  gate stacks with sub-nanometer capacitance equivalent thickness and low interface trap density by in situ  $NH_3$  plasma pretreatment. Appl Surf Sci 325:13–9

- Li XF, Liu XJ, Cao YQ, Li AD, Li H, Wu D (2013) Improved interfacial and electrical properties of atomic layer deposition HfO<sub>2</sub> films on Ge with La<sub>2</sub>O<sub>3</sub> passivation. Appl Surf Sci 264:783–6

- 17. Zimmermann C, Bethge O, Winkler K, Lutzer B, Bertagnolli E (2016) Improving the ALD-grown  $Y_2O_3/Ge$  interface quality by surface and annealing treatments. Appl Surf Sci 369:377–83

- Matsubara H, Sasada T, Takenaka M, Takagi S (2008) Evidence of low interface trap density in GeO<sub>2</sub>/Ge metal-oxide-semiconductor structures fabricated by thermal oxidation. Appl Phys Lett 93(3):032104–3

- Kita K, Lee CH, Nishimura T, Nagashio K, Toriumi A (2009) Control of properties of GeO<sub>2</sub> films and Ge/GeO<sub>2</sub> interfaces by the suppression of GeO volatilization. ECS Trans 19(2):101–16

- Kita K, Suzuki S, Nomura H, Takahashi T, Nishimura T, Toriumi A (2007) Dramatic improvement of GeO<sub>2</sub>/Ge MIS characteristics by suppression of GeO volatilization. Ecs Trans 11(4):111–22

- Kita K, Suzuki S, Nomura H, Takahashi T, Nishimura T, Toriumi A (2008) Direct evidence of GeO volatilization from GeO<sub>2</sub>/Ge and impact of its suppression on GeO<sub>2</sub>/Ge metal-insulator-semiconductor characteristics. Jpn J Appl Phys 47(4):2349

- Nakashima H, Iwamura Y, Sakamoto K, Wang D, Hirayama K, Yamamoto K et al (2011) Postmetallization annealing effect of TiN-gate Ge metal-oxidesemiconductor capacitor with ultrathin SiO<sub>2</sub>/GeO<sub>2</sub> bilayer passivation. Appl Phys Lett 98(25):252102

- Yamamoto K, Ueno R, Yamanaka T, Hirayama K, Yang H, Wang D et al (2011) High-performance Ge metal-oxide-semiconductor field-effect transistors with a gate stack fabricated by ultrathin SiO<sub>2</sub>/GeO<sub>2</sub> bilayer passivation. Appl Phys Express 4(5):051301–3

- 24. Di Z, Zhang M, Liu W, Shen Q, Luo S, Song Z et al (2005) Interfacial and electrical characteristics of  $Al_2O_3$  gate dielectric on fully depleted SiGe on insulator. Appl Phys Lett 86(26):262102

- Renault O, Samour D, Damlencourt JF, Blin D, Martin F, Marthon S et al (2002) HfO<sub>2</sub>/SiO<sub>2</sub> interface chemistry studied by synchrotron radiation x-ray photoelectron spectroscopy. Appl Phys Lett 81(19):3627–9

- Deng S, Xie Q, Deduytsche D, Schaekers M, Lin D, Caymax M et al (2011) Effective reduction of fixed charge densities in germanium based metaloxide-semiconductor devices. Appl Phys Lett 99(5):437

- Choi C, Lee JC (2010) Scaling equivalent oxide thickness with flat band voltage (VFB) modulation using in situ Ti and Hf interposed in a metal/highk gate stack. J Appl Phys 108(6):197

- 28. Cheng CC, Chien CH, Luo GL, Yang CH, Kuo ML, Lin JH et al (2007) Study of thermal stability of  $HfO_xN_y/Ge$  capacitors using postdeposition annealing and  $NH_3$  plasma pretreatment. Entrepreneurship Regional Dev 154(7):229–52

- Bai W, Lu N, Kwong DL (2005) Si interlayer passivation on germanium MOS capacitors with high-к dielectric and metal gate. IEEE Electron Device Lett 26(6):378–80

- Kraut E, Grant R, Waldrop J, Kowalczyk S (1980) Precise determination of the valence-band edge in x-ray photoemission spectra: application to measurement of semiconductor interface potentials. Phys Rev Lett 44(24):1620

- 31. Nicollian EH, Brews JR (1982) MOS (metal oxide semiconductor) physics and technology. Wiley, New York, Chapter 5

- 32. Gao J, He G, Fang Z, Lv J, Liu M, Sun Z (2016) Interface quality modulation, band alignment modification and optimization of electrical properties of HfGdO/Ge gate stacks by nitrogen incorporation. J Alloys Compd 695:2199–206

- 33. Cheng ZX, Liu L, Xu JP, Huang Y, Lai PT, Tang WM (2016) Impact of nitrogen incorporation on the interface between Ge and  $La_2O_3$  or  $Y_2O_3$  gate dielectric: a study on the formation of germanate. IEEE Trans Electron Devices 63(12):4888–92

- Li XF, Cao YQ, Li AD, Li H, Wu D (2012) HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/Ge gate stacks with small capacitance equivalent thickness and low interface state density. ECS Solid State Lett 1(2):N10–N2

- Mi Y, Wang S, Chai J, Pan J, Huan A, Ning M et al (2006) Energy-band alignments at LaAlO<sub>3</sub> and Ge interfaces. Appl Phys Lett 89(20):2107

Dalapati GK, Oh HJ, Lee SJ, Sridhara A, Wong ASW, Chi D (2008) Energy-

- band alignments of HfO<sub>2</sub> on p-GaAs substrates. Appl Phys Lett 92(4):042120

- 37. Seo KI, Mcintyre PC, Sun S, Lee DI, Pianetta P, Saraswat KC (2005) Chemical states and electronic structure of a HfO<sub>2</sub>/Ge(001) interface. Appl Phys Lett 87(4):042902–3

# Submit your manuscript to a SpringerOpen<sup>™</sup> journal and benefit from:

- Convenient online submission

- Rigorous peer review

- Immediate publication on acceptance

- Open access: articles freely available online

- ► High visibility within the field

- ► Retaining the copyright to your article

Submit your next manuscript at ► springeropen.com