### NANO EXPRESS Open Access

# The Role of Air Adsorption in Inverted Ultrathin Black Phosphorus Field-Effect Transistors

Qiangian Li<sup>1</sup>, Jiancui Chen<sup>2</sup>, Zhihong Feng<sup>2</sup>, Liefeng Feng<sup>1\*</sup>, Dongsheng Yao<sup>1</sup> and Shupeng Wang<sup>1</sup>

#### **Abstract**

Few-layer black phosphorus (BP) attracts much attention owing to its high mobility and thickness-tunable band gap; however, compared with the commonly studied transition metal dichalcogenides (TMDCs), BP has the unfavorable property of degrading in ambient conditions. Here, we propose an inverted dual gates structure of ultrathin BP FET to research the air adsorption on BP. In fabrication process of back-gate BP FET, BP was transferred directly onto a wafer covered with electrodes. Thus, we can exclude the BP degradation during the process of electrodes fabrication, such as electron beam lithography (EBL) and thermal evaporation process. Furthermore, without any electrode covering BP, BP could be in full contact with the air; then the accurate effect of the air adsorption on BP can be researched in detail. The results clearly show that annealing can remove the *p*-doping resulted from the metastable oxygen adsorbed on the surface of BP, but the adsorption can be restored in a few hours exposure. In addition, both back and top gate inverted BP FETs exhibit a favorable performance. Therefore, this inverted structure is also an optional structure to reduce the influence of the instability of BP devices.

**Keywords:** Inverted structure, Field-effect transistors (FET), Annealing, Air adsorption

#### **Background**

Phosphorus is the second discovered monotypic Van der Waals two-dimensional (2D) material. Its bandgap achieves both larger on/off ratios than in graphene transistors and higher field-effect mobility compared with TMDCs such as MoSe<sub>2.</sub> It was found to be naturally ptype with a direct bandgap of 0.3 eV, which was predicted to increase to approximate 2.0 eV in a monolayer remaining direct bandgap [1, 2]. Therefore, it is suitable for transistor, logic, and optoelectronic applications. Despite the good points of BP, a major challenge for its practical application is the instability in the ambient environment. It gets degradation upon exposure to ambient air [3, 4]. Previous studies suggested that the performance of degradation upon exposure to the air is mainly attributed to the adsorption of water or oxygen on the material surfaces and the chemical reactions [5],

In order to get the detailed effect of the adsorption on BP, we propose an inverted structure of BP FET. In fabrication process of back-gate BP FET, the BP was transferred directly onto a wafer covered with electrodes. In traditional FET, the electrodes are fabricated on BP directly. Compared with it, the inverted few layers backgate BP FET has two advantages to getting the role of air adsorption on BP. Firstly, the degradation of BP during the EBL and the thermal evaporation process could be eliminated. Secondly, it can ensure sufficient contact between the air condition and BP because the effect of electrodes covering on BP is avoided. For example, if the device had been fabricated into the traditional structure in our fabrication process, the electrodes should have covered more than half effect area of BP. Both advantages ensure that we could clearly observe the change process of the dominant carrier type. Results provide a conclusive proof that annealing can remove the p-doping that resulted from the metastable oxygen adsorption on the surface of BP [9, 10]. In addition, both this inverted

<sup>&</sup>lt;sup>1</sup>Tianjin Key Laboratory of Low Dimensional Materials Physics and Preparing Technology, School of Science, Tianjin University, Tianjin 300072, China Full list of author information is available at the end of the article

and this adsorption of few-layer BP is generally supposed to lead to *p*-doping upon exposure to air [6–8].

<sup>\*</sup> Correspondence: fengliefeng@tju.edu.cn

back- and top-gate BP FETs exhibit favorable mobility. Therefore, this inverted structure could be an optional structure to reduce the influence of the instability of BP devices.

#### **Methods**

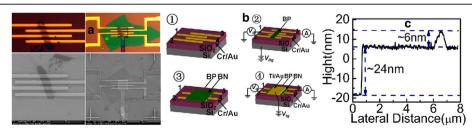

The fabrication process is illustrated in Fig. 1b. Metal contacts were deposited on degenerately doped silicon wafer covered with a layer of thermally grown silicon dioxide by EBL and thermal evaporation of chromium and gold (typically 15 and 60 nm, respectively), then a scotch type-based mechanical exfoliation method was used to peel a few layers of BP from bulk crystal onto silicon wafer-fabricated polyvinyl alcohol (PVA) and polymethyl methacrylate (PMMA). Then BP was transferred onto a wafer covered with electrodes already. The PMMA was removed by overnight treatment with acetone and then 15 min treatment with IPA [11]. After annealing at 200 °C for 3 min, we measured the transport characteristic before and after annealing of the back-gate devices. We passivated the BP surface with h-BN which has been demonstrated to protect the devices from degrading in the ambient environment for 1 week [12], the transfer method of h-BN is the same as BP, followed by a second EBL and thermal evaporation process to obtain the top-gate electrode. Optical microscopy and atomic force microscopy (AFM) were used to find few layer samples and to determine their thickness (Fig. 1a, c). The surface roughness of BP was verified using SEM before and after fabrication (Fig. 1a). In traditional 2D material FET structure, the ultrathin BP is transferred before EBL patterning, which could contribute to momentary exposure in ambient conditions and thereby cause slightly degraded performance. In this inverted structure, the BP back-gate FET device did not go through the step of EBL patterning, metal deposition, and lift-off process.

#### **Results and Discussion**

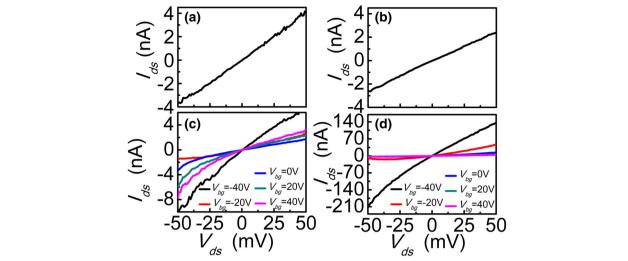

Figure 2a, b show the drain current-voltage curves of the inverted FET without annealing and just after annealing as no gate swept, at a small drain-to-source voltage ( $V_{ds}$ ) of 50 mV, respectively. Both the drain currents vary

linearly in this region with the small  $V_{ds}$ . However, there is no significant increase in the source current of the inverted FET just after annealing, as shown in Fig. 2b, which goes contrary to the theory that annealing will lead to a better contact [13]. Under various back-gate biases (–40, –20, 0, 20, and 40 V), the output characteristics of the inverted device just after annealing and after annealing about 5 h with the small  $V_{ds}$  of 50 mV are shown in Fig. 2c, d, respectively. Compared with just after annealing, the source current after annealing about 5 h significantly increases.

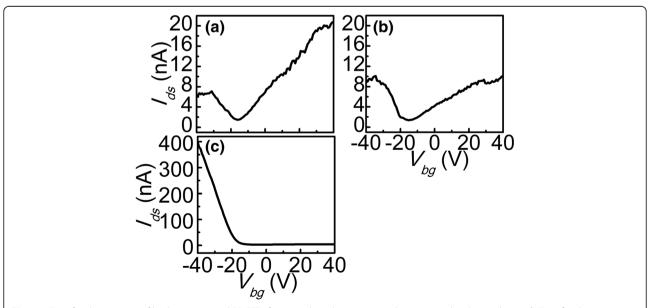

In order to explain the above experiments that  $I_{ds}$  does not increase just after annealing but sharply increases after annealing about 5 hours, we measured the transfer characteristics under these two conditions, as shown in Fig. 3. Theoretical and experimental studies have shown that metastable oxygen adsorbed on the surface of fewlayer BP will lead to p-doping upon exposure to air, but the adsorption can be removed during the annealing [13, 14], then leading to a reduction in p-doping. In Fig. 3a, the absorption should be removed just after annealing, then the dominant carrier type in BP changes from naturally p-type to n-doping. With the increasing of exposure time, re-adsorption of the metastable oxygen on BP surface leads to p-doping enhancing slowly while *n*-doping fading away, as shown in Fig. 3b. After enough exposure time, the n-doping of the device reduces to near zero, the dominant carrier type changes to p-doping again, as shown in Fig. 3c.

Normally, the high work function of the metal electrodes such as Cr/Au we used will cause hole accumulation at the metal-semiconductor interface, which forms a low-resistance ohmic contact for the *p*-doping device; while for the *n*-doping device a depletion region is formed at the interface, which leads to Schottky barriers [15, 16]. According to this theory, in our devices the dominant carrier type changes to *n*-type just after annealing, then Schottky barriers are formed and consequently a small current; however, with the re-adsorption of the metastable oxygen on the BP surface, the *p*-type recovers, which matches well with the high work function metal electrodes as we used. At the same time,

Fig. 1 a Optical image and SEM image of the inverted FET. **b** Fabrication process of the device. ① The first EBL patterning obtain the Cr/Au electrode (15/60 nm), the channel of each electrode is 2 μm. ② Transfer of the ultrathin BP. ③ Transfer of the *h*-BN. ④ The second EBL patterning obtain the Ti/Au electrode (20/60 nm). **c** The AFM integrated data, BP thickness of 6 nm on the top of 24 nm *h*-BN

Fig. 2 a *I-V* characteristic without annealing as no gate swept. **b** *I-V* characteristic just after annealing as no-gate swept. **c** Output characteristic for back-gate swept from –40 to 40 V just after annealing. **d** Output characteristic for back-gate inverted BP FET swept from –40 to 40 V after annealing about 5 h

annealing will result in better contact, so the current sharply increases after annealing about 5 h. In summary, according to the results of Fig. 3 we can conclude that the work function mismatch between the metal contacts and few-layer BP should be the main reason that the current does not increase in Fig. 2b, c but significantly increases in Fig. 2d.

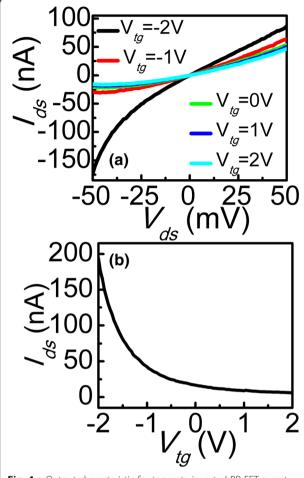

Previous reports have proved that the BP degradation process can be slowed down considerably by covering the material with appropriate passivation layers, and it is stable for more than a week [17, 18]. Here we passivated the device with h-BN and then fabricated a top-gate. Figure 4a, b show the output and transfer characteristics of the device. Obviously nonlinear behavior of  $I_{ds}$  varying with different  $V_{ds}$  indicates the formation of Schottky barrier at the contacts. It may be caused by the residue of PMMA. On the other hand, residue could increase the thickness of the dielectric layer, which could weaken the effective control of the channel carrier concentration by the gate electrode [19]. Therefore,

**Fig. 3** a Transfer characteristic of back-gate inverted BP FET after annealing about 5 min, *p*-doping is weaker than *n*-doping. **b** Transfer characteristic of back-gate inverted BP FET after annealing about 10 min, *p*-doping enhances slowly while *n*-doping fades away. **c** Transfer characteristic of back-gate inverted BP FET after annealing about 5 h, *n*-doping reduces to near zero

Fig. 4 a Output characteristic for top-gate inverted BP FET swept from –2 to 2 V. b Transfer characteristic of top-gate inverted BP FET

if the gate is not adequately strong, the drain will decrease the gate over the channel control, resulting in poor-gate dependence shown in Fig. 4b compared with Fig. 3c. In addition, both back- and top-gates devices exhibit a respectable on/off ratio of  $10^2$  with small  $V_{ds}$  of 0.05 V. In our measurement, due to the doping level limited by the breakdown electric field of the gate dielectric, the on-state current of our devices does not yet reached saturation. It is therefore possible to achieve even higher drain-current modulation by using high-k materials as gate dielectrics for higher doping [20, 21].

The field-effect mobility of devices was exacted from the linear scales shown in Figs. 3c and 4b using the expression:

$$\mu_{FE} = \frac{dI_{ds}}{dV_g} \frac{L}{WC_i V_{ds}} \tag{1}$$

where L/W is channel length/width ratio, in our experiments L is 6  $\mu$ m, W is about 5  $\mu$ m, then the ratio is 1.2.

$C_i = \varepsilon_0 \varepsilon/d$  is the capacitance per unit area [5],  $\varepsilon_{0=} 8.854 \times 10^{-12} \mathrm{fm}^{-1}$  is the permittivity of vacuum,  $\varepsilon = 3.9$  is the relative dielectric constant of SiO<sub>2</sub>, and the relative dielectric constant of h-BN is ranging from 3 to 4 [22]. d is the thickness of the dielectric layer, for SiO<sub>2</sub> is 300 nm, and for h-BN is 24 nm. By using the maximum slope of the  $I_{ds}$ - $V_g$  plots, at  $V_{ds} = 0.05$  V, a field mobility for back-gate sweeps and top-gate sweeps are, respectively, 50 cm<sup>2</sup>v<sup>-1</sup>s<sup>-1</sup> and 75 cm<sup>2</sup>v<sup>-1</sup>s<sup>-1</sup> in our measurement range. From  $S = dV_{bg}/d\log I_{sd}$ , we can obtain an excellent subthreshold swing  $S \approx 1.3$  V/dec of top-gate FET on h-BN compared with  $S \approx 6.8$  V/dec of back-gate FET on SiO<sub>2</sub>

#### **Conclusions**

In summary, we prepared an inverted ultrathin BP FET to get the role of air adsorption on BP. In fabrication process of back-gate BP-FET, the BP was transferred directly onto a wafer covered with electrodes. In traditional FET, the electrodes are fabricated on BP directly. Compared with it, our inverted back-gate BP FET could keep BP complete contact with air condition and does not need to consider BP degradation during BEL and thermal evaporation process as well as the cover effect of electrodes on BP. Therefore, the effects of annealing and exposure time after annealing on the electrical behaviors of ultrathin BP back-gate FET could be measured accurately. Just after annealing the adsorption is removed, then the dominant carrier type in BP changes from naturally *p*-type to *n*-doping. With the increasing of exposure time, re-adsorption of the metastable oxygen on BP surface leads to p-doping enhancing slowly while n-doping fading away. After enough exposure time, the *n*-doping of the device reduces to near zero, the dominant carrier type changes to p-doping again. In addition, top-gate ultrathin h-BN BP FET also exhibits favorable mobility and lower subthreshold swing compared with back-gate FET. On the whole, both back- and top-gate ultrathin inverted BP FETs exhibit high performance. Therefore, this inverted structure is an optional structure to reduce influence of the instability of BP devices because of two potential advantages, one is to avoid the time of BP exposure to air as long as it is timely covered by h-BN, and the other is to reduce an electrode preparation after BP transfer.

#### Abbreviations

2D: Two-dimensional; AFM: Atomic force microscopy; BP: Black phosphorus; EBL: Electron beam lithography;  $V_{ds}$ : Drain-to-source voltage

#### Acknowledgements

This work was supported by the National Natural Science Foundation of China (Grant Nos. DMR-11204209 and 60876035), and the Tianjin Natural Science Foundation of the Key Project of China (Grant No 13JCZDJC32800)

#### Authors' Contributions

QQ completed the experiments with the help of JC and ZH, under LF supervision. JC fabricated electrodes and ZH measured the behavior of devices. LF and DS suggested the structure and discussion of the electrical characteristics. QQ, SP, and LF wrote and revised the paper with input from all other authors. All authors read and approved the final manuscript.

#### Competing Interests

The authors declare that they have no competing interests.

#### **Author details**

<sup>1</sup>Tianjin Key Laboratory of Low Dimensional Materials Physics and Preparing Technology, School of Science, Tianjin University, Tianjin 300072, China. <sup>2</sup>State Key Laboratory of Precision Measuring Technology & Instruments, College of Precision Instrument and Opto-electronics Engineering, Tianjin University, Tianjin 300072, China.

## Received: 17 May 2016 Accepted: 16 November 2016 Published online: 25 November 2016

#### References

- Keys RW (1953) The electrical properties of black phosphorus. Phys Rev 92: 580–584

- Asahina H, Shindo K, Morita A (1982) Electronic structure of black phosphorus in tight binding approach. J Phys Soc Jpn 51:1193–1199

- Schwierz F (2013) Graphene transistors: status, prospects, and problems. Proc IFFE 101:1567–1584

- Wang QH, Kalantar-Zadeh K, Kis A, Coleman JN, Strano MS (2012) Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat Nanotechnol 7:699–712

- Wan BS, Yang BC, Wang Y, Zhang JY, Zeng ZM, Liu ZY, Wan WH (2015) Enhanced stability of black phosphorus field-effect transistors with SiO2 passivation. Nanotechnol 26:453702

- Ziletti A, Carvalho A, Campbell DK, Coker DF, CastroNeto AH (2015) Oxygen defects in phosphorene. Phys Rev Lett 114:046801

- Wang H, Wang XM, Xia FN, Wang LH, Jiang H, Xia QF, Chin ML, Dubey M, Han SJ (2014) Black phosphorus radio-frequency transistors. Nano Lett 14: 6424–6429

- Wood JD, Wells SA, Jariwala D, Chen KS, Cho E, Sangwan VK, Liu XL, Lauhon LJ, Marks TJ, Hersam MC (2014) Effective passivation of exfoliated black phosphorus transistors against ambient degradation. Nano Lett 14:6964–6970

- Castellanos-Gomez A, Vicarelli L, Prada E, Island JO, Narasimha-Acharya KL, Blanter SI, Groenendijk DJ, Buscema M, Steele GA, Alvarez JV, Zandbergen HW, Palacios JJ, van der Zant HSJ (2014) Isolation and characterization of few-layer black phosphorus. 2D Materials 1(2):23–29

- Buscema M, Groenendijk DJ, Blanter SI, Steele GA, van der Zant HSJ, Castellanos-Gomez A (2014) Fast and broadband photoresponse of fewlayer black phosphorus field-effect transistors. Nano Lett 14:3347–3352

- Island JO, Steele GA, van der Zant HSJ, Castellanos-Gomez A (2015)

Environmental instability of few-layer black phosphorus. 2D Materials 2(1):011002

- Gillgren N, Wickramaratne D, Shi Y, Espiritu T, Yang J, Hu J, Wei J, Liu X, Mao ZQ, Watanabe K, Taniguchi T, Bockrath M, Barlas Y, Lake RK, Lau CN (2014) Gate tunable quantum oscillations in air-stable and high mobility few-layer phosphorene heterostructures. 2D Materials 2:011001

- Zhao LD, Zhang BP, Liu WS, Zhang HL, Li JF (2009) Effects of annealing on electrical properties of n-type Bi 2 Te 3 fabricated by mechanical alloying and spark plasma sintering. J Alloys Compd 467:91–97

- Doganov RA, Koenig SP, Yeo Y, Watanabe K, Taniguchi T, Özyilmaz B (2015) Transport properties of ultrathin black phosphorus on hexagonal boron nitride. Appl Phys Lett 106:083505

- Perello DJ, Chae SH, Song S, Lee YH (2015) High-performance n-type black phosphorus transistors with type control via thickness and contact-metal engineering. Nat Commun 6:7908

- Fontana M, Deppe T, Boyd AK, Rinzan M, Liu AY, Paranjape M, Barbara P (2013) Electron-hole transport and photovoltaic effect in gated MoS2 Schottky junctions. Sci Rep 3:1634

- Chen XL, Wu YY, Wu ZF, Han Y, Xu SG, Wang L, Ye WG, Han TY, He YH, Cai Y, Wang N (2014) High-quality sandwiched black phosphorus heterostructure and its quantum oscillations. Nat Commun 6:7315

- De Visser PJ, Chua R, Island JO, Finkel M, Katan AJ, Thierschmann H, van der Zant HSJ, Klapwijk TM (2016) Spatial conductivity mapping of unprotected

- and capped black phosphorus using microwave microscopy. 2D Materials 3(2):021002

- 19. Miao J, Zhang S, Cai L, Scherr M, Wang C (2015) Ultrashort channel length black phosphorus field-effect transistors. ACS Nano 9:9236–9243

- Kim JS, Jeon PJ, Lee J, Choi K, Lee HS, Cho Y, Lee YT, Hwang DK, Im S (2015) Dual gate black phosphorus field effect transistors on glass for NOR logic and organic light emitting diode switching. Nano Lett 15:5778–5783

- 21. Luo X, Rahbarihagh Y, Hwang J, Liu H, Du Y, Ye PD (2014) Temporal and thermal stability of  $Al_2O_3$ -passivated phosphorene MOSFETs. Electron Device Letters, IEEE 35:1314–1316

- Dean CR, Young AF, Meric I, Lee C, Wang L, Sorgenfrei S, Watanabe K, Taniguchi T, Kim P, Shepard KL, Hone J (2010) Boron nitride substrates for high-quality graphene electronics. Nat Nanotechnol 5:722–726

# Submit your manuscript to a SpringerOpen journal and benefit from:

- ► Convenient online submission

- ► Rigorous peer review

- ► Immediate publication on acceptance

- ▶ Open access: articles freely available online

- ► High visibility within the field

- Retaining the copyright to your article

Submit your next manuscript at ▶ springeropen.com