# NANO EXPRESS

**Open Access**

# Gate-Controlled WSe<sub>2</sub> Transistors Using a Buried Triple-Gate Structure

M. R. Müller<sup>1,5,6</sup>, R. Salazar<sup>2</sup>, S. Fathipour<sup>3</sup>, H. Xu<sup>3</sup>, K. Kallis<sup>1</sup>, U. Künzelmann<sup>4</sup>, A. Seabaugh<sup>3</sup>, J. Appenzeller<sup>2</sup> and J. Knoch<sup>5\*</sup>

# Abstract

In the present paper, we show tungsten diselenide (WSe<sub>2</sub>) devices that can be tuned to operate as *n*-type and *p*-type field-effect transistors (FETs) as well as band-to-band tunnel transistors on the same flake. Source, channel, and drain areas of the WSe<sub>2</sub> flake are adjusted, using buried triple-gate substrates with three independently controllable gates. The device characteristics found in the tunnel transistor configuration are determined by the particular geometry of the buried triple-gate structure, consistent with a simple estimation of the expected off-state behavior.

Keywords: Electrostatic doping, Tungsten diselenide (WSe<sub>2</sub>), Reconfigurable device

# Background

In recent years, two-dimensional layered materials, such as graphene and transition metal dichalcogenides (TMDs), have attracted a great deal of interest as channel material in high-performance field-effect transistors (FETs) [1–8]. A major advantage of these materials is their ability to drive high electrical currents in only few layers or even a monolayer (<1 nm). In addition, there are a number of semiconducting TMDs that exhibit band gaps  $\geq 1$  eV. Thus, they are in principle ideally suited for ultimately scaled FETs as well as for band-to-band tunnel FETs tunnel field-effect transistors (TFETs) since the ultrathin channel layer enables excellent gate control yielding ultimate scalability and a large band-to-band tunnel probability [9–16].

However, a major challenge for the application of TMDs is the realization of an appropriate source-channel-drain doping profile because conventional (e.g., impurity, chemical) doping is extremely challenging [17, 18], and in the case of TFETs, the right amount of doping is subject to tedious optimization: if the doping concentration is too small, the gate action is not sufficiently screened, and the band-to-band tunneling probability cannot be made large enough. On the other hand, a large doping concentration may lead to a large Fermi

\* Correspondence: knoch@iht.rwth-aachen.de

<sup>5</sup>Institute of Semiconductor Electronics, RWTH Aachen University, Sommerfeldstr. 24, 52074 Aachen, Germany

energy, and as a result, carriers are injected from the Boltzmann tail of the source Fermi distribution function giving rise to a TFET with an inverse subthreshold slope close to 60 mV/dec [19-21]. A viable alternative is source-drain doping by means of electrostatic potentials, which has already been employed to investigate carbon nanotube, graphene, and nanowire FETs as well as optoelectronic devices [9, 22-28]. This approach not only allows convenient doping, but in a TFET, it enables to disentangle screening in source from the position of the Fermi energy [21]. Moreover, electrostatic doping adds device level functionality through the tunability to operate the same device in various transistor configurations. Specifically, if the electrostatic doping is controllable individually for source and drain, not only the *n*-type and *p*-type FETs can be realized [29] but the device can also be switched into a TFET mode of operation which allows tuning to devices from conventional to low-power operation.

Here, we present a tungsten diselenide (WSe<sub>2</sub>) device which we tune by electrostatic doping to function as an *n*FET (*n-n* doping profile), *p*FET (*p-p* doping profile), and TFET (*n-p* doping profile). WSe<sub>2</sub> is used here since, in contrast to molybdenum disulfide (MoS<sub>2</sub>), it provides an approximately mid-gape Fermi level line-up for (e.g., nickel) ensuring that electrons as well as holes can be injected efficiently in the different device configurations [30]. In addition, it exhibits a smaller band gap and lower effective masses compared to MoS<sub>2</sub>,

© The Author(s). 2016 **Open Access** This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

Full list of author information is available at the end of the article

both known to improve the performance of TFETs [13–16, 21]. The electrostatic doping is realized by a modified version of our previously employed buried triple-gate (BTG) structure [31]. This structure features three independently controllable gates: one center-gate and two side-gates for electrostatic doping. Since all three gates are buried and the BTG's surface is entirely flat, the structure serves as a platform for convenient deposition and investigation of devices from various kinds of novel channel materials. The electrostatic environment is fully determined by the BTG structure, therefore, allows true comparison of various materials in terms of their suitability for future FET or TFET devices.

# Methods

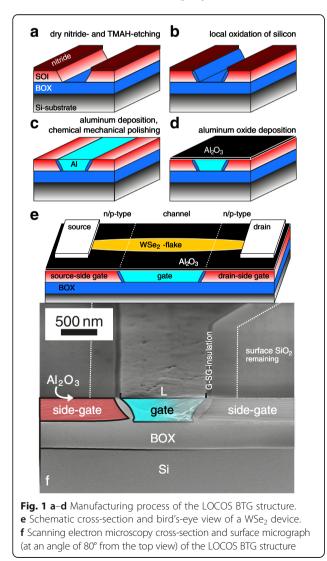

Figure 1 illustrates the manufacturing process of the BTG structure. The starting material is a 4'' silicon-on-insulator (SOI) wafer with a top layer of 340 nm (100) Si

and a 400 nm buried oxide (BOX). The silicon is implanted with 10<sup>15</sup> cm<sup>-2</sup> of phosphorous at 75 keV, 7.5°, vielding a peak implantation depth of 104 nm. Afterwards, the wafer is RCA-cleaned, and a 200-nm layer of Si<sub>3</sub>N<sub>4</sub> is deposited by a plasma-enhanced chemical vapor deposition. Subsequently, a furnace treatment at 900 °C for 20 min heals the implantation damage, activates the dopants, and condenses the nitride. Optical lithography in combination with CHF<sub>3</sub> + O<sub>2</sub> plasma etching is used to pattern the nitride layer. After the removal of the photoresist (PR) and directly after an additional buffered oxide etch dip, tetramethylammonium hydroxide (TMAH), 25 wt% at 80 °C, is used to anisotropically etch through the SOI top layer (cf. Fig. 1a). Wet thermal oxidation is used to grow the gate-side-gate (G-SG) insulation (Fig. 1b). Afterwards, the nitride mask is removed by a two-step procedure: (i)  $CHF_3 + O_2$  plasma removes the oxidized nitride and (ii) H<sub>3</sub>PO<sub>4</sub> at 160 °C removes the remaining nitride. No apparent oxidation under the nitride mask (bird's beak) is present. A thin oxide (~10 nm) is grown on the silicon surface in order to serve as an additional insulation and as a stopping layer for the following damascene process: After sputter-deposition of aluminum onto the surface, chemical-mechanical planarization (CMP) is employed to remove the Al overburden yielding an entirely planar structure (Fig. 1c). To reduce the thermally induced growth of hillocks on the Al-surface, a repolishing procedure is used [32]. The gate dielectric is obtained by atomic layer deposition (ALD) of 7 nm Al<sub>2</sub>O<sub>3</sub> (Fig. 1d). The BTG structures are completed by selectively etching the oxides using  $CHF_3$  + Ar plasma in the contact regions and subsequent deposition of 10 nm Ti + 170 nm Au as side and top-gate contact metals using a lift-off technique. The finished wafer is cut into sample pieces of  $7.5 \times$ 7.5 mm<sup>2</sup>; Fig. 1e shows a schematic device cross-section and bird's-eye view.

Figure 1f presents a scanning electron microscopy (SEM) micrograph of the BTG's surface and crosssection. Clearly visible is the G-SG insulation of 90 nm. Not visible is the 7 nm  $Al_2O_3$  dielectric cap layer on the surface. An excellent topography, with a dishing of only ~1 nm per micron, and quality (only few pits and scratches, roughness down to 1-nm root mean square) of the polished aluminum is achieved [32, 33].

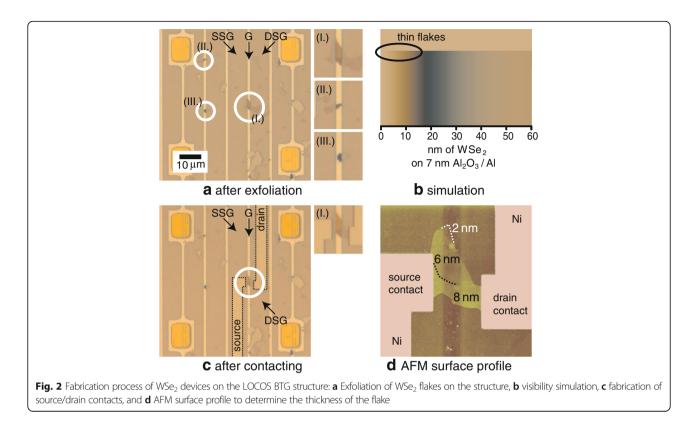

For the fabrication of the WSe<sub>2</sub> devices on the BTG structure, first, WSe<sub>2</sub> is exfoliated from bulk material using a blue tack tape. Figure 2a shows a section of a BTG meander with additional electron-beam lithography markers. The sample is inspected using optical microscopy in order to identify thin flakes (<10 nm) lying across the aluminum gate, e.g., a flake as in location (I.). Thin flakes were found to exhibit a characteristic yellowish color on the gate region (Al<sub>2</sub>O<sub>3</sub>/Al) with a strong contrast to thicker flakes of ~15–25 nm, which appear

distinctly blue-colored (cf. locations (II.) and (III.)). Interestingly, such a clear distinction is not present on the side-gate region  $(Al_2O_3/SiO_2/Si/SiO_2/Si)$ . The characteristic swing from blue to yellowish colors identifying the thinnest flakes is also confirmed by our simulations, as shown in Fig. 2b [34].

After identification of appropriate flakes, electronbeam lithography is used to pattern source/drain contact structures into polymethyl methacrylate (PMMA). Subsequently, deposition of 90 nm nickel and lift-off are employed to obtain the contact structures and complete the devices. Figure 2c depicts the flake from (a) after contact formation. In order to determine the thickness of the flakes, atomic force microscopy (AFM) is conducted. Figure 2d shows the AFM surface profile of the presented flake, indicating a thickness of  $\sim$ 6–8 nm.

## **Results and Discussion**

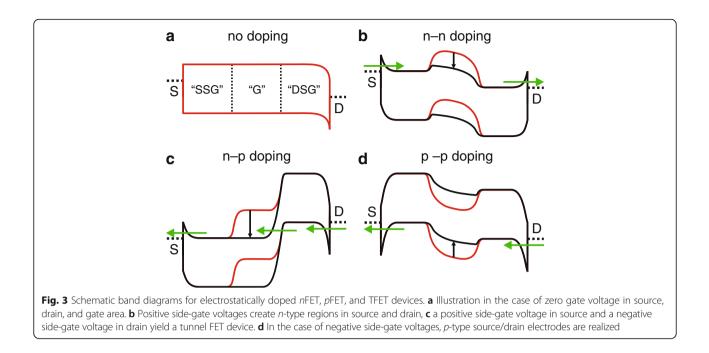

Figure 3 illustrates the operational principle of our devices: For the realization of an *n*FET (Fig. 3b), positive and equal voltage is applied to both side-gates (this means that  $V_{\rm SSG} = V_{\rm DSG} > 0$ . For simplicity, this will be called side-gate voltage  $V_{\rm SG}$  in the following) which lowers the bands in the regions controlled by the side-gates (SSG and DSG) and yields an *n*-*n* doping profile. Note that all given voltages are in reference to the ground potential at the source contact. The described electrostatic doping yields a thinning of the source and

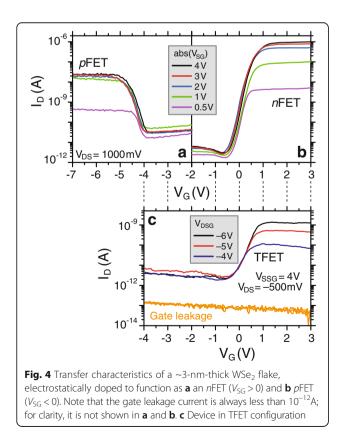

drain Schottky barriers (SB) for electron injection while suppressing hole injection at the same time. As a result, a unipolar device behavior is expected in contrast to the usually observed ambipolar behavior of WSe<sub>2</sub> transistors. Applying positive voltage to the center gate, i.e., the actual gate of the device (denoted with  $V_G$  in the following), yields a lowering of the bands in the gate-controlled region (G) and switches the device on. The described mechanism can be employed similarly to realize a *p*FET device (i.e., a *p-p* doping profile) by applying  $V_{SG} < 0$ ,  $V_G < 0$ (cf. Fig. 3d). Figure 4 displays transfer characteristics of a WSe<sub>2</sub> with a thickness of  $d_{WSe2} = 3$  nm determined by AFM. The source-drain bias  $(V_{\rm DS})$  is constant at 1 V and the various curves presented are from different side-gate voltages. The n-doping (Fig. 4a) leads to an increase of the drain current up to an  $I_{\rm on}/I_{\rm off}$  ratio of  $>3 \times 10^5$  at  $V_{\rm SG}$  = 4 V. As already mentioned above, a pFET device is realized for  $V_{SG} < 0$ ,  $V_G < 0$ . In this case, we find an  $I_{on}/I_{off}$  ratio of  $\sim 10^3$  at  $V_{\rm SG} = -4$  V (cf. Fig. 4b). The  $\sim 100 \times$  larger *n*-current in comparison to the *p*-current (as well as the larger leakage current on the pFET compared to the *n*FET) is attributed to the influence of the nickel contacts, which were shown to be slightly more *n*-type [7, 30]. The subthreshold swings are 180 mV/dec (nFET) and 240 mV/dec (pFET), respectively. Note, that the current for large positive (n-type device) and negative (*p*-type device) gate voltages  $V_{\rm G}$  saturates, and current flow is then limited by the injection

through the source-side SB. Since the tunneling probability is a function of the barrier height (0.54 and 0.74 eV in the case of electron and hole injection, respectively) and effective mass (0.34 and 0.44  $m_0$  for electrons and holes, respectively), a different modulation of

the tunneling probability through the SB is obtained for the *n*-type and the *p*-type [30]. As a result, the side-gates have considerably less impact on the SB in the *p*-type device which is reflected in the drain current for  $abs(V_{SG}) > 2 V$  that hardly changes anymore.

In addition, for this device we are also able to set up a TFET device configuration with an *n*-type source and a *p*-type drain contact using  $V_{\rm DS}$  = -500 mV,  $V_{\rm SSG}$  = 4 V,  $V_{\rm DSG}$  <-4 V. As displayed in Fig. 4c, the gate leakage current in the TFET device configuration is at least 30× lower than the drain current. It is important to note that usually temperature-dependent measurements of the off-state are used to demonstrate TFET behavior. However, in the present case, we were able to demonstrate *n*and *p*-type device behavior proving that a conduction-/ valence-band profile appropriate for TFETs can be adjusted using the BTG. And since gate leakage can be neglected, we ascribe the exponential increase of current around  $V_{\rm G} = 0$  V to band-to-band tunneling. This is also consistent with the fact that increasingly negative DSG voltages improve the band-to-band tunneling probability (by increasing the electric field at the G/DSG junction) while at the same time hinder thermionic transport due to an increased potential barrier carriers from drain have to overcome.

The  $I_{\rm on}/I_{\rm off}$  ratio is ~4.5 × 10<sup>2</sup> at  $V_{\rm DSG}$  = -6 V, and the inverse subthreshold slope is  $S \approx 366$  mV/dec. This rather large value is due to the fact that overpolishing during the CMP fabrication process leads to a G-SG insulation of approximately  $d_{\rm G-SG}$  = 90 nm (cf. Fig. 1f). Interpreting the band-to-band tunneling barrier as a SB, the expected inverse subthreshold slope can be computed

with  $S \approx k_B T/q \cdot ln(10) (1/2 + 1/3 \cdot \sqrt{d_{G-SG}} d_{WSe2})$  [35, 36] yielding  $S \approx 358$  mV/dec. This agrees very well with the experimental value showing that it is the G-SG insulation that limits the performance of the device with *n*-*p* doping. Further improvements in the BTG fabrication will therefore allow a substantial performance increase. In addition, the channel layer thickness, i.e., the WSe<sub>2</sub> flake thickness, plays a prominent role for the device performance of the TFETs [15, 16]. Indeed, in the case of a device with an approximately 13-nm-thick WSe<sub>2</sub> flake, we found a strongly deteriorated TFET behavior (not shown here). In turn, a thinner flake should allow substantial improvements in terms of inverse subthreshold slope and on-state current in the TFET configuration.

From the mere consideration of the band gap of WSe<sub>2</sub>, we would expect a larger on/off current ratio with significantly smaller off-state currents. However, an explanation of this phenomenon requires a detailed simulation of the device structure including the fact that in the present device, the distribution of the injected current among the various WSe<sub>2</sub> layers [37] depends on the different (side-) gate voltages. We therefore speculate that band-to-band tunneling as well as interlayer coupling is responsible for the electrical behavior of the device in TFET configuration.

## Conclusions

We demonstrated that electrostatic doping allows the realization of a tunable device to function as *n*FET, *p*FET, and as band-to-band tunnel FET on the same  $WSe_2$  flake. Based on a BTG substrate, we were able to dope source and drain regions independently to create the required band-profiles for the three transistor configurations. An optimized triple-gate configuration thus enables to dynamically switch transistors from conventional (*n*FET, *p*FET) to low-power (TFET) operation.

#### Acknowledgments

The authors would like to thank the cleanroom teams of the University of Notre Dame and TU Dortmund University for their support. The partial financial support by the German Research Foundation (DFG) (grant number KN545/3-2) is acknowledged.

#### Authors' contributions

MM carried out the bulk part of the device fabrication and wrote the paper. RS, SF and HX carried out device processing and did electrical measurements together with MM. KK and MM developed tha modified LOCOS process. UK and MM developed the chemical mechanical polishing process. AS, JA and JK provided device physics know-how and helped interpreting the experimental data. JK developed the layout of the BTG structures, provided processing know-how and revised the manuscript. All authors read and approved the final manuscript.

#### **Competing interests**

The authors declare that they have no competing interests.

#### Author details

<sup>1</sup>Intelligent Microsystems Chair, TU Dortmund, Emil-Figge-Str. 68, 44227 Dortmund, Germany. <sup>2</sup>Birck Nanotechnology Center, Purdue University, 1205 W. State Street, West Lafayette, IN 47907, USA. <sup>3</sup>Department of Electrical Engineering, University of Notre Dame, Notre Dame, IN 46556, USA. <sup>4</sup>Institute of Semiconductor and Microsystems Technology, TU Dresden, 01062 Dresden, Germany. <sup>5</sup>Institute of Semiconductor Electronics, RWTH Aachen University, Sommerfeldstr. 24, 52074 Aachen, Germany. <sup>6</sup>Present address: Infineon Technologies, Siemensstrasse 2, 9500 Villach, Austria.

#### Received: 18 July 2016 Accepted: 8 November 2016 Published online: 22 November 2016

#### References

- Jena D (2013) Tunneling transistors based on graphene and 2-D crystals. Proc IEEE 101:1585–1602

- Fiori G, Bonaccorso F, Iannaccone G, Palacios T, Neumaier D, Seabaugh A, Banerjee S, Colombo L (2014) Electronics based on two-dimensional materials. Nat Nanotechnol 9:768–779

- 3. Sik Hwang W, Remskar M, Yan R, Protasenko V, Tahy K, Doo Chae S, Zhao P, Konar A, Xing HG, Seabaugh A, Jena D (2012) Transistors with chemically synthesized layered semiconductor  $WS_2$  exhibiting  $10^5$  room temperature modulation and ambipolar behavior. Appl Phys Lett 101:013107-1–3

- Radisavljevic B, Radenovic A, Brivio J, Giacometti V, Kis A (2011) Single-layer MoS<sub>2</sub> transistors. Nat Nanotechnol 6:147–150

- Fathipour S, Remskar M, Varlec A, Ajoy A, Yan R, Vishwanath S, Rouvimov S, Hwang WS, Xing HG, Jena D, Seabaugh A (2015) Synthesized multiwall MoS<sub>2</sub> nanotube and nanoribbon field-effect transistors. Appl Phys Lett 106: 022114 1–3

- Fathipour S, Ma N, Hwang WS, Protasenko V, Vishwanath S, Xing HG, Xu H, Jena D, Appenzeller J, Seabaugh A (2014) Exfoliated multilayer MoTe<sub>2</sub> fieldeffect transistors. Appl Phys Lett 105:192101-1–3

- Das S, Appenzeller J (2013) WSe<sub>2</sub> field effect transistors with enhanced ambipolar characteristics. Appl Phys Lett 103:103501-1–3

- Fathipour S, Hwang WS, Kosel T, Xing HG, Haensch W, Jena D, Seabaugh A (2013) Exfoliated MoTe<sub>2</sub> field-effect transistor. Dev Res Conf (DRC) 71:115–116

- 9. Appenzeller J, Lin Y-M, Knoch J, Avouris P (2004) Band-to-band tunneling in carbon nanotube field-effect transistors. Phys Rev Lett 93:196805-1-4

- Bhuwalka KK, Born M, Schindler M, Schmidt M, Sulima T, Eisele I (2006) Pchannel tunnel field-effect transistors down to sub-50 nm channel lengths. J J Appl Phys 45:3106

- 11. Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-k gate dielectric. IEEE Trans Electron Dev 54:1725–1733

- Knoll L, Schmidt M, Zhao Q, Trellenkamp S, Schaefer A, Bourdelle K, Mantl S (2013) Si tunneling transistors with high on-currents and slopes of 50 mV/dec using segregation doped NiSi2 tunnel junctions. Solid-State Electron 84:211–215

- 13. lonescu A, Riel H (2011) Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479:329–337

- 14. Seabaugh AC, Zhang Q (2010) Low-voltage tunnel transistors for beyond CMOS logic. Proc IEEE 98:2095–2110

- Sandow C, Knoch J, Urban C, Zhao Q-T, Mantl S (2009) Impact of electrostatics and doping concentration on the performance of silicon tunnel field-effect transistors. Solid-State Electron 53:1126–1129

- Knoch J (2009) Optimizing tunnel FET performance—impact of device structure, transistor dimensions and choice of material. Internat. Symp. VLSI Technol., Syst. Appl VLSI-TSA. 45–46

- Gong Y, Liu Z, Lupini AR, Shi G, Lin J, Najmaei S, Lin Z, Elias AL, Berkdemir A, You G, Terrones H, Terrones M, Vajtai R, Pantelides ST, Pennycook SJ, Lou J, Zhou W, Ajayan PM (2014) Band gap engineering and layer-by-layer mapping of selenium-doped molybdenum disulfide. Nano Lett 14:442–449

- 18. Kiriya D, Tosun M, Zhao P, Kang JS, Javey A (2014) Air-stable surface charge transfer doping of  $MoS_2$  by benzyl viologen. J Am Chem Soc 136:7853–7856

- Knoch J, Mantl S, Appenzeller J (2007) Impact of the dimensionality on the performance of tunneling FETs: bulk versus one-dimensional devices. Solid-State Electron 51:572–578

- Gnani E, Gnudi A, Reggiani S, Baccarani G (2013) Drain-conductance optimization in nanowire TFETs by means of a physics-based analytical model. Solid-State Electron 84:96–102

- Knoch J (2016) Chapter eight—nanowire tunneling field-effect transistors. Semicond Semimet 94:273–295

- 22. Appenzeller J, Knoch J, Bjork MT, Riel H, Schmid H, Riess W (2008) Toward nanowire electronics. IEEE Trans Electron Dev 55:2827–2845

- 23. Das A, Pisana S, Chakraborty B, Piscane S, Saha S, Waghmare U, Novoselov K, Krishanmurthy H, Geim A, Ferrari A, Sood A (2008) Monitoring dopants by

Raman scattering in an electrochemically top-gated graphene transistor. Nat Nanotechnol  $3{:}210{-}215$

- Zhang Y, Tang T-T, Girit C, Hao Z, Martin M, Zettl A, Crommie M, Shen Y, Wang F (2009) Direct observation of a widely tunable bandgap in bilayer graphene. Nature 459:820–823

- Knoch J, Chen Z, Appenzeller J (2012) Properties of metal-graphene contacts. IEEE Trans Nanotechnol 11:513–519

- Xu H, Fathipour S, Kinder EW, Seabaugh AC, Fullerton-Shirey SK (2015) Reconfigurable ion gating of 2H-MoTe<sub>2</sub> field-effect transistors using poly(ethylene oxide)-CsCIO<sub>4</sub> solid polymer electrolyte. ACS Nano 9:4900–4910

- Wang Z, Wang F, Yin L, Huang Y, Xu K, Wang F, Zhan X, He J (2016) Electrostatically tunable lateral MoTe2 p-n junction for use in highperformance optoelectronics. Nanoscale 27:5534–5540

- Baugher BWH, Churchill HOH, Yang Y, Jarillo- Herrero P (2014) Optoelectronic devices based on electrically tunable p–n diodes in a monolayer dichalcogenide. Nat Nanotechnol 9:262–267

- Heinzig A, Slesazeck S, Kreupl F, Mikolajick T, Weber WM (2012) Reconfigurable silicon nanowire transistors. Nano Lett 12:119–124

- Appenzeller J, Zhang F, Das S, Knoch J (2016) Transition metal dichalcogenide Schottky barrier transistors: a device analysis and material comparison. In "2D Materials for Nanoelectronics", CRC Press, Taylor and Francis Group, Boca Raton, p. 207–240

- Mueller MR, Gumprich A, Schuette F, Kallis K, Kuenzelmann U, Engels S, Stampfer C, Wilck N, Knoch J (2014) Buried triple-gate structures for advanced field-effect transistor devices. Microelectron Engin 119:95–99

- Mueller MR, Kallis K, Menzel S, Kuenzelmann U, Petrov I, Knoch J (2014) Tackling hillocks growth after aluminum CMP. Internat. Conf. Planarization/ CMP Technol. (ICPT). 129–132

- Kuenzelmann U, Mueller MR, Kallis KT, Schuette F, Menzel S, Engels S, Fong J, Lin C, Dysard J, Bartha JW, Knoch J (2012) Chemical-mechanical planarization of aluminium damascene structures, Internat. Conf. Planarization/CMP Technol. (ICPT); 1–6

- Mueller MR, Gumprich A, Ecik E, Kallis KT, Winkler F, Kardynal B, Petrov I, Kunze U, Knoch J (2015) Visibility of two-dimensional layered materials on various substrates. J Appl Phys 118:145305

- Knoch J, Zhang M, Mantl S, Appenzeller J (2006) On the performance of single-gated ultrathin-body SOI Schottky-barrier MOSFETs. IEEE Trans Electron Dev 53:1669–1674

- Das S, Prakash A, Salazar R, Appenzeller J (2014) Toward low-power electronics: tunneling phenomena in transition metal dichalcogenides. ACS Nano 8:1681–1689

- Das S, Appenzeller J (2013) Where does the current flow in twodimensional layered systems? Nano Lett 13:3396–3402

# Submit your manuscript to a SpringerOpen<sup>®</sup> journal and benefit from:

- Convenient online submission

- Rigorous peer review

- Immediate publication on acceptance

- Open access: articles freely available online

- High visibility within the field

- Retaining the copyright to your article

Submit your next manuscript at > springeropen.com