Abstract

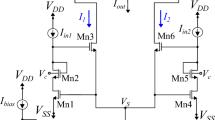

In this paper we present a new, adaptive spatial-derivative circuit for CMOS image sensors. The circuit removes its offset as a natural part of its operation using a combination of electron tunneling and hot-electron injection to add or remove charge on a floating-gate of an auto-zeroing amplifier. We designed, fabricated and successfully tested a chip with the circuit. Test results show that the circuit reduces the offsets by more than an order of magnitude.

Similar content being viewed by others

References

Cauwenberghs, G., Neugebauer, C. F. and Yariv, A., “Analysis and verification of an analog VLSI incremental outer-product learning system.” IEEE Trans. on Neural Networks 3(3), pp. 488-497, 1992.

Glasser, L. A., “A UV write-enabled PROM.” In: H. Fuchs (ed.), Chapel Hill Conference on VLSI, Computer Science Press, Rockville, MD, 1985, pp. 61-65.

Mead, C., “Adaptive Retina.” In: C. Mead and M. Ismail (eds.), Analog VLSI Implementation of Neural Systems. Kluwer Academic Publishers, Boston, MA, 1989, pp. 239-246.

Kerns, D. A., “Experiments in very large-scale analog computation.” Ph.D. Thesis, Electrical Engineering, California Institute of Technology, 1993.

Lenzlinger, M. and Snow, E. H., “Fowler-Nordheim tunneling into thermally grown SiO2.” Journal of Applied Physics 40(1), pp. 278-283, 1969.

Sackinger, E. and Guggenbuhl, W., “An analog trimming circuit based on a floating-gate device.” IEEE Journal of Solid State Circuits SC-23, pp. 1437-1440, 1998.

Carley, L. R., “Trimming analog circuits using floating-gate analog MOS memory.” IEEE J. Solid State Circ. 24(6), pp. 1569-1575, 1989.

Lande, T. S., Ranjbar, H., Ismail, M. and Berg, Y., “An analog floating-gate memory in a standard digital technology,” in Proc. 5th Intl. Conf. on Microelectronics for Neural Networks and Fuzzy Systems-MicroNeuro96. IEEE Computer Society Press, Lausanne, Switzerland, Los Alamitos, CA, February 12-14, pp. 271-276, 1996.

Diorio, C., Hasler, P., Minch, B. and Mead, C., “A complementary pair of four-terminal silicon synapses.” Analog Integrated Circuits and Signal Processing 13(1/2), pp. 153-166, 1997.

Harrison, R. R., Hasler, P. and Minch, B. A., “Floating-gate CMOS analog memory cell array,” in Proceedings of the 1998 IEEE ISCAS Meeting. Monterey, CA, pp. 204-207, 1998.

Lazzaro, J., Wawrzynek, J. and Kramer, A., “Systems technologies for silicon auditory models.” IEEE Micro 14(3), pp. 7-15, 1994.

Sin, C. K., Kramer, A., Hu, V., Chu, R. R. and Ko, P. K., “EEPROM as an analog storage device, with particular applications in neural networks.” IEEE Trans. on Electron Devices 39(6), pp. 1410-1419, 1992.

Castro, H., Tam, S. and Holler, M., “Implementation and performance of an analog non-volatile neural-network.” Analog Integrated Circuit and Signal Processing 4(2), pp. 97-113, 1993.

Murray, A. F., Churcher, S., Hamilton, A., Holmes, A. J., Jackson, G. B., Reekie, H. M. and Woodburn, R. J., “Pulse stream VLSI neural networks.” IEEE Micro 14(3), pp. 29-39, 1994.

Devos, F., Zhang, M., Ni, Y. and Pone, J. F., “Trimming CMOS smart imager with tunnel-effect nonvolatile analog memory.” Electronic Letters 29(20), pp. 1766-1767, 1993.

Aslam-Siddiqi, A., Brockherde, W., Schanz, M. and Hosticka, B. J., “A 128-pixel CMOS image sensor with integrated analog nonvolatile memory.” IEEE Journal of Solid-State Circuits 33(10), pp. 1497-1501, 1998.

Douglas, R., Mahowald, M. and Mead, C., “Neuromorphic analogue VLSI.” In: W. M. Cowan, E. M. Shooter, C. F. Stevens and R. F. Thompson (eds.), Annual Reviews in Neuroscience, Annual Reviews Inc., Palo Alto, CA, 1995, vol. 18, pp. 255-281.

Hasler, P., Minch, B. A., Diorio, C. and Mead, C. A., “An autozeroing amplifier using PFET hot-electron injection,” in Proceedings of the 1996 IEEE ISCAS Meeting, Atlanta, pp. 325-328, 1996.

Kramer, J. and Indiveri, G., “Neuromorphic vision sensors and preprocessors in system applications,” Advanced Focal Plane Arrays and Electronic Cameras (AFPAEC'98). Zürich, Switzerland, 1998.

Horiuchi, T. K., Morris, T. G., Koch, C. and DeWeerth, S. P., “Analog VLSI circuits for attention-based visual tracking.” In: M. Mozer, M. Jordan and T. Petsche (eds.), Advances in Neural Processing Systems 9, MIT Press, 1997, pp. 706-712.

Delbrück, T. and Mead, C. A., “Photoreceptor circuit with a wide dynamic range.” CNS Memo 30, California Institute of Technology, 1996.

Diorio, C., “Neurally inspired silicon learning: from synapse transistors to learning arrays.” Ph.D. Thesis, Electrical Engineering, California Institute of Technology, 1997.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Pesavento, A., Horiuchi, T., Diorio, C. et al. Adaptation of Current Signals with Floating-Gate Circuits. Analog Integrated Circuits and Signal Processing 30, 137–147 (2002). https://doi.org/10.1023/A:1013703711427

Issue Date:

DOI: https://doi.org/10.1023/A:1013703711427