mater.scichina.com link.springer.com

### ARTICLES

Published online 4 December 2020 | https://doi.org/10.1007/s40843-020-1534-2 Sci China Mater 2021, 64(5): 1219-1229

# Floating-gate photosensitive synaptic transistors with tunable functions for neuromorphic computing

Lingkai Li, Xiao-Lin Wang, Junxiang Pei, Wen-Jun Liu, Xiaohan Wu<sup>\*</sup>, David Wei Zhang and Shi-Jin Ding<sup>\*</sup>

ABSTRACT Synaptic devices that merge memory and processing functions into one unit have broad application potentials in neuromorphic computing, soft robots, and humanmachine interfaces. However, most previously reported synaptic devices exhibit fixed performance once been fabricated, which limits their application in diverse scenarios. Here, we report floating-gate photosensitive synaptic transistors with charge-trapping perovskite quantum dots (PQDs) and atomic layer deposited (ALD) Al<sub>2</sub>O<sub>3</sub> tunneling layers, which exhibit typical synaptic behaviors including excitatory postsynaptic current (EPSC), pair-pulse facilitation and dynamic filtering characteristics under both electrical or optical signal stimulation. Further, the combination of the high-quality Al<sub>2</sub>O<sub>3</sub> tuning layer and highly photosensitive PQDs charge-trapping layer provides the devices with extensively tunable synaptic performance under optical and electrical co-modulation. Applying light during electrical modulation can significantly improve both the synaptic weight changes and the nonlinearity of weight updates, while the memory effect under light modulation can be obviously adjusted by the gate voltage. The pattern learning and forgetting processes for "0" and "1" with different synaptic weights and memory times are further demonstrated in the device array. Overall, this work provides synaptic devices with tunable functions for building complex and robust artificial neural networks.

**Keywords:** synaptic device, floating-gate transistor, perovskite quantum dot, tunable synaptic function, optical and electrical co-modulation

#### INTRODUCTION

With the advent of the "Big Data Era" and the "Internet of Things", various tasks ranging from big data analysis, vehicle autonomous driving, real-time health monitoring to visual and auditory recognition have proliferated worldwide [1,2]. Digital logic computers based on the von Neumann architecture are no longer efficient when processing such large amounts of complex data because it requires complex algorithms, long processing time and huge energy consumption. Fortunately, brain-inspired computing technology has shown the potential for highspeed, low-energy consumption in big data processing and intelligent perception [3,4]. The main idea of braininspired computing is to imitate the structure and working functions of the brain [5]. Since synaptic plasticity has been proven to be the physiological basis of brain computing and learning, great attention has been paid to the development of synapse-like devices [6–14].

By using two-terminal non-volatile devices (e.g., twoterminal memristors, phase change memories) and threeterminal/multi-terminal transistors (e.g., floating-gate transistors, electrochemical transistors), synaptic functions have been well mimicked [15-19]. More encouragingly, these synapse-like devices have already made some important advances in data classification [20], machine vision [21], neural prosthesis [22], soft robotics [23], and neural signal analysis [24]. Although significant progress has been made, most of these devices exhibit fixed performance once been made. Synaptic devices with tunable functions are highly desirable for powerful computing systems that can be applied to various scenarios. Recently, several strategies have been developed to adjust the intrinsic synaptic plasticity in fixed materials and device structures. For example, Han et al. [25] reported the use of the low-temperature solvent engineering, i.e., altering solvent compositions, to tune the synaptic plasticity of crystallized poly(3-hexylthiophene) (P3HT) nanowire-based synaptic transistors. By adjusting the composition of the co-solvent, it is easy to achieve adjustable synaptic plasticity between short-term and

State Key Laboratory of ASIC and System, School of Microelectronics, Fudan University, Shanghai 200433, China <sup>\*</sup> Corresponding authors (emails: sjding@fudan.edu.cn (Ding SJ); wuxiaohan@fudan.edu.cn (Wu X))

long-term on crystalline P3HT nanofiber-based synaptic devices. Kim et al. [26] demonstrated artificial synapses composed of 2D, quasi-2D, and 3D halide perovskite film, and investigated the dimensionality-dependent plasticity. By adjusting the dimensionality of the perovskite layer, the retention time can be controlled. However, the method of co-solvent engineering and adjusting the material dimensionality can only be used to adjust the device performance before the device has been made. Li et al. [27] reported on floating-gate synaptic transistors capable of accelerated learning through temperature-facilitated synaptic plasticity modulation. Although the temperature can be controlled to achieve dynamic adjustment of synaptic plasticity, it also means that the ambient temperature may affect the device performance. In addition, it is difficult to adjust the temperature for each synaptic device in practical applications.

Herein, we report a floating-gate synaptic transistor with adjustable functions/performance by introducing photosensitive materials as the charge-trapping layer. Allinorganic cesium lead bromide (CsPbBr<sub>3</sub>) perovskite quantum dots (PQDs) are used as the photosensitive charge-trapping material because of their excellent optoelectronic properties and good environmental stability. The atomic layer deposited (ALD) Al<sub>2</sub>O<sub>3</sub> films with precisely controllable thicknesses are utilized as the tunneling layer. The combination of the photosensitive chargetrapping CsPbBr<sub>3</sub> PQDs and the Al<sub>2</sub>O<sub>3</sub> tuning layer provides the devices with adjustable synaptic plasticity under optical and electrical co-modulation. Light, as another input signal control terminal besides gate voltage, can significantly increase the weight change and meanwhile avoid the deterioration of weight update non-linearity (NL). The memory effect under light stimulation can also be tuned by different gate biases. The pattern learning and forgetting processes for "0" and "1" with different synaptic weights and memory times are successfully simulated in the device array.

#### **EXPERIMENTAL SECTION**

#### **Device fabrication**

The CsPbBr<sub>3</sub> PQD solution was synthesized according to previous report [28]. The charge-trapping layer was fabricated by spin-coating the PQD solution onto a precleaned Si wafer with 300-nm  $\text{SiO}_2$  at 3000 r min<sup>-1</sup> for 60 s, followed by drying under vacuum for 1 h. Then, 8-nm-thick Al<sub>2</sub>O<sub>3</sub> tunneling layer was deposited on the top of the CsPbBr<sub>3</sub> PQD layer by using ALD technology (Picosun ALD R200), and trimethylaluminum (TMA)

and oxygen plasma (O<sub>2</sub>) were used as precursor and reactant, respectively. Subsequently, 60-nm pentacene film was deposited by thermal evaporation. Finally, 70-nm Au electrodes were thermally evaporated onto the films through a shadow mask under a vacuum of  $8 \times 10^{-4}$  Pa. The width (W) and length (L) of the device are 500 and 100 µm, respectively.

#### Material and device characterization

UV-vis absorption spectra and photoluminescence (PL) spectra were taken from a Lambda 750 UV-visible spectrophotometer and an F-320 spectrophotometer (Tianjin Gangdong Sci.&Tech. Co., Ltd), respectively. Dynamic light scattering (DLS) curve was measured by a light scattering instrument (Modulated 3D LS, Switzerland). Xray diffraction (XRD) spectra were measured by using an X-Ray diffractometer (Bruker Advance D8) with Cu Ka radiation (1.54 Å) at 40 kV. Transmission electron microscopy (TEM) image was observed by an FEI TECNAI G2 S-TWIN F20. Scanning electron microscopy (SEM) images were obtained from a field emission electron microscope (Zeiss SIGAMA HD). The monochromatic lights were provided by Xenon arc lamp filtered with a double grating monochromator (Omno 330150, Beijing NBeT, China) or mounted collimated LEDs (Thorlabs). The transistor characteristics and synaptic functions were measured on a Cascade probe station (Summit 11000M) by using a semiconductor device analyzer (Agilent B1500A) in air at room temperature.

#### **RESULTS AND DISCUSSION**

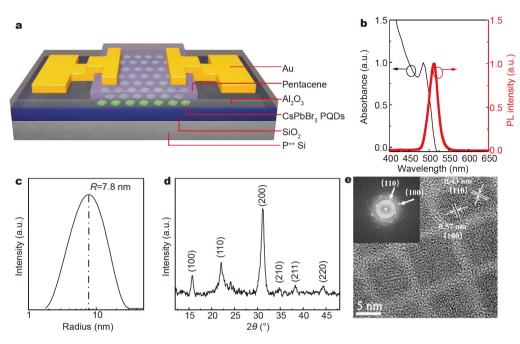

A schematic diagram of the floating-gate synaptic transistor with pentacene channel and Au source/drain electrodes fabricated on  $p^{++}$  Si substrate is shown in Fig. 1a. Pentacene is a commonly used organic semiconductor in thin-film transistors and synaptic devices, which exhibits relatively high mobility, simple fabrication, decent stability and low cost [29]. A thermally grown SiO<sub>2</sub> film (300 nm), spin-coated CsPbBr<sub>3</sub> PQDs and an ALD Al<sub>2</sub>O<sub>3</sub> film (10 nm) were employed as the blocking layer, charge-trapping layer and tunneling layer, respectively. In a certain range (5-15 nm), larger thickness of the tuning layer generally leads to longer retention time, but also higher writing and erasing voltages [30]. The CsPbBr<sub>3</sub> PQD solution was prepared according to previous report [28], and characterized by using PL, UV-Vis spectrophotometer, and DLS. The PL and UV-Vis absorption spectra exhibit emission peak and absorption edge both at around 520 nm, indicating the bandgap of the CsPbBr<sub>3</sub> PQDs is about 2.35 eV (Fig. 1b). The average size of the

**Figure 1** Schematic and characterizations of the device with CsPbBr<sub>3</sub> PQDs. (a) A schematic diagram of the floating-gate synaptic transistor with the CsPbBr<sub>3</sub> PQD charge-trapping layer and Al<sub>2</sub>O<sub>3</sub> tunneling layer; (b) UV-Vis absorption and PL spectra and (c) size distribution of the CsPbBr<sub>3</sub> PQDs; (d) XRD pattern and (e) HRTEM image of the spin-coated CsPbBr<sub>3</sub> PQD film (inset: electron diffraction corresponding to the selected area).

CsPbBr<sub>3</sub> PQDs is 7.8 nm according to the DLS results (Fig. 1c). Then, the charge-trapping layer was deposited by spin-coating the CsPbBr<sub>3</sub> PQD solution on the SiO<sub>2</sub> film. XRD was used to investigate the structure of the CsPbBr<sub>3</sub> PQDs (Fig. 1d). The diffraction peaks at  $2\theta$  = 15.1°, 21.5°, 30.5°, 34.3°, 37.7° and 43.7° correspond to (100), (110), (200), (210), (211) and (220) crystal planes of cubic CsPbBr<sub>3</sub> QDs, respectively [31]. The SEM images of the CsPbBr<sub>3</sub> PQD layer show well distributed nanoparticles (Fig. S1). Further, the CsPbBr<sub>3</sub> PQD layer exhibits highly crystalline cubic structure with an average size of 8 nm, as observed under the high-resolution TEM (HRTEM) (Fig. 1e). The lattice spacings of 0.57 and 0.43 nm observed in the selected area electron diffraction are well corresponding to the (100) and (110) planes of cubic crystal CsPbBr<sub>3</sub> PQDs, which further reveals the formation of cubic perovskite phases [32].

The transfer curves  $(I_d - V_g)$  and output characteristics  $(I_d - V_d)$  of the floating-gate synaptic transistor are presented in Fig. S2a–c. The large hysteresis window observed from the  $I_d - V_g$  curve could be attributed to the charge-trapping effect of CsPbBr<sub>3</sub> PQDs, because the hysteresis window of the device without CsPbBr<sub>3</sub> PQDs is rather small (Fig. S2d). On the other hand, PQDs have been widely utilized to fabricate optoelectronic devices including photosensors [33], photomemories [34] and

photo-sensory neurons [8] because of their excellent photosensitivity. In our case, the introduction of CsPbBr<sub>3</sub> PQDs is expected to provide the devices with photosensitivity, so that light can be used as another control signal to adjust the device performance. Therefore, the photosensitivity of the floating-gate synaptic transistors was investigated. As the light wavelength was reduced from 530 to 350 nm, the channel current increased significantly, indicating an excellent photosensitivity (Fig. S2c). It should be noted that the photosensitivity of the device is induced by the CsPbBr<sub>3</sub> PQD layer instead of the pentacene channel (Fig. S2e and f). Fig. S3a shows the writing/erasing characteristics of the floating-gate synaptic transistor under positive and negative gate voltages. After being written at -20 V/2 s, the  $I_{\rm d}$ - $V_{\rm g}$  curves showed a large threshold voltage shift ( $I_d$ - $V_g$  curve window of 9 V) to the left of the initial curve. However, when a positive voltage pulse of 20 V/8 s was applied to the gate, the  $I_{d}$ - $V_{g}$  curves exhibited a very limited change, indicating that the device is difficult to erase electrically. With the assist of light (wavelength of 490 nm), the device presented larger threshold voltage shifts in both writing and erasing processes as compared with the only electrical writing/erasing. The above results reveal that the CsPbBr<sub>3</sub> PQD layer provides the device with enhanced photosensitivity and photomemory behavior (Fig. S3b and c).

The mechanism of the photomemory behavior is illustrated with the energy band diagram of the device, as shown in Fig. S4.

A biological synapse refers to a specialized structure that transmits the impulse of one neuron to another [35]. The bio-signal processing, learning and memory are established in the human brain through modifying the release of neurotransmitters in synapses. The coexistence of computing and memory in synapses has inspired scientists to imitate synapse functions to overcome the "von Neumann bottleneck" of traditional digital computers [7,14,36–39]. Over the past few years, floating-gate transistors have received extensive attention in mimicking synaptic functions because of their gate controllable channel conductance and nonvolatile memory effect [40-42]. Since our floating-gate device has two control terminals (gate voltage and light), it can realize adjustable synaptic functions, thus providing the possibility of building a robust neural circuit for different application scenarios. To simulate biological synapses, the gate and the channel of the transistors are generally regarded as the presynaptic membrane and postsynaptic membrane, respectively. In our device, both gate and light can be regarded as the presynaptic membrane, while the channel is regarded as the postsynaptic membrane. The channel current or the conductance is defined as the synaptic weight.

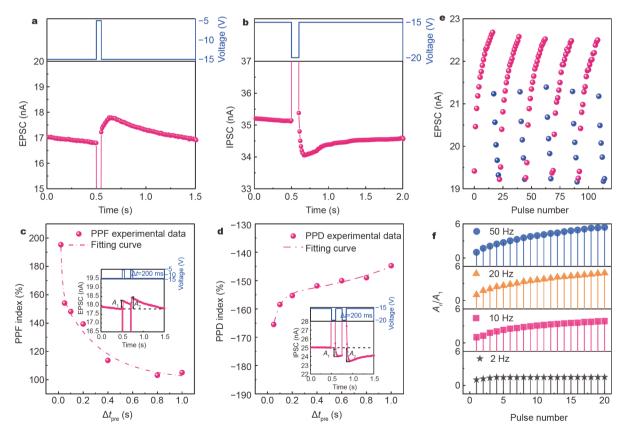

We firstly investigated the synaptic performance under electrical signals only. In order to emulate the simple synaptic event induced by the electrical stimulus, i.e., excitatory postsynaptic current (EPSC), a relative positive presynaptic pulse (-15 to -5 V/50 ms) was applied to the bottom gate while keeping the  $V_{ds} = 50$  mV, as shown in Fig. 2a. After the relative positive gate pulse, the current increased rapidly to 18 nA, and then slowly decreased to the initial current, which indicates that a typical EPSC behavior was successfully simulated. Besides, the current with an instantaneous drop followed by a slow recovery, i. e., inhibitory postsynaptic current (IPSC), was similarly realized by applying relative negative pulses (Fig. 2b, -15

**Figure 2** Synaptic behaviors of the device under electrical modulation. (a) EPSC triggered by a relative positive presynaptic pulse (-15 to -5 V/ 50 ms); (b) IPSC response to a relative negative presynaptic pulse (-15 to -20 V/100 ms). Dependence of the (c) PPF and (d) PPD indexes on interspike interval (inset: EPSC or IPSC generated by two successive presynaptic pulses). (e) The increase and decrease of channel current induced by the continuous and repeated stimuli; (f) dynamic filtering characteristics.

to -20 V/100 ms). Fig. S5 shows the energy band diagram of the floating-gate synaptic transistor under electrical pulse stimulation. At the base voltage  $V_{\rm g} = -15$  V, the trapped and de-trapped holes will reach a dynamic equilibrium, thus the current remains stable (Fig. S5a). When the relative positive voltage pulse (-15 to -5 V/ 50 ms) is applied, the equilibrium state is broken, causing extra holes to be transferred from the CsPbBr<sub>3</sub> PQD floating-gate to the channel (Fig. S5b). This generates a sharp increase in the concentration of holes in the channel, and thus instantaneously enhances the current (EPSC). After the voltage pulse, the hole distribution in the device would go back to the dynamic equilibrium state, hence the current gradually decreases back to the baseline. The IPSC behaviors under relative negative voltage pulse (-15 to -20 V/100 ms) can be explained similarly (Fig. S5c). Pair-pulse facilitation and depression (PPF and PPD) are typical forms of short-term plasticity (STP). As shown in the inset of Fig. 2c, two consecutive relative positive pulses (-15 to -5 V/50 ms) with an interval of 200 ms lead to superimposed enhancements of the current. The peak value of the EPSC generated by the second voltage pulse is larger than the peak value of the EPSC generated by the first one, indicating a PPF behavior. Similarly, PPD behavior was also mimicked by two consecutive relative negative pulses (-15 to -20 V/ 100 ms) with an interval of 200 ms, as shown in the inset of Fig. 2d. In order to briefly describe the relationship between the weight change and the interval of two consecutive pulses, the ratio of the amplitude of the second EPSC (or IPSC)  $(A_2)$  to the first one  $(A_1)$  is defined as the facilitation ratio  $(A_2/A_1)$ , which illustrates the degrees of weight strengthening and weakening. Thus, the PPF (PPD) index as a function of interval time ( $\Delta t_{pre}$ ) was studied, as shown in Fig. 2c and d. Both the PPF and PPD indexes gradually decay as the interval time increases. Generally, the decay of the PPF (PPD) indexes as a function of the pulse interval can be fitted with the following double exponential function [43]:

$$PPF(PPD) = 1 + C_1 \exp\left(-\frac{t}{\tau_1}\right) + C_2 \exp\left(-\frac{t}{\tau_2}\right), \qquad (1)$$

where *t* is the pulse interval,  $C_1$  and  $C_2$  are the initial facilitation magnitudes of the rapid and slow phases, respectively.  $\tau_1$  and  $\tau_2$  are the characteristic relaxation times of the rapid and slow phases, respectively. The well-fitted curve indicates that the biological PPF and PPD behaviors were successfully emulated. Besides, synaptic potentiation and depression were also realized by using numbers of continuous and repeated stimuli (Fig. 2e). The interval

between two adjacent stimuli should be much shorter than the time for the charge distribution to return back to the equilibrium state, otherwise no superimposed potentiation or depression will be observed. This behavior can be utilized to mimic the high-pass filter function of the bio-synapse. For the lower-frequency pulses, the current remains almost unchanged. As the pulse frequency gradually increases, the potentiation of the current becomes increasingly obvious, which indicates the ability to filter information by frequency (Fig. 2f).

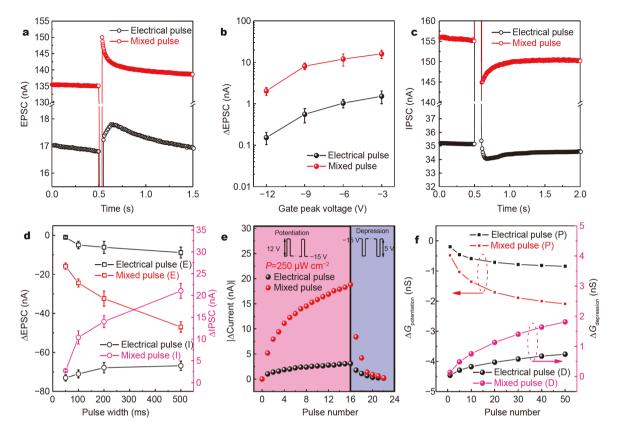

Then, the effect of light, as another input signal control terminal, on synaptic functions of the floating-gate transistors during electrical modulation was further studied. Fig. 3a demonstrates the EPSCs generated by only the voltage pulse and the light-voltage mixed pulses (light:  $\lambda = 490 \text{ nm}, 250 \text{ }\mu\text{W cm}^{-2}, \text{ voltage: } -15 \text{ to } -5 \text{ V}/50 \text{ ms}),$ respectively. Both the currents presented similarly sharp increase and slow decay, while the EPSC significantly increased from 1 to 15 nA with the co-modulation of the light. Such EPSC enhancement under light co-modulation was found for many different voltage pulses (Fig. 3b). As shown in Fig. 3c, the IPSC induced by positive electrical pulses is also improved with light co-modulation. Fig. 3d summarizes the effect of light co-modulation on both EPSC and IPSC under electrical gate-voltage pulses with different widths, and the EPSCs and IPSCs were increased by light co-modulation for all the cases. This behavior is because that the CsPbBr<sub>3</sub> PQDs in the floating gate generate electron-hole pairs under light, hence the positive voltage pulses can transfer more holes from the floating gate to the channel, resulting in larger EPSCs/ IPSCs. Then, the effect of light co-modulation on synaptic weight during continuous and repeated electrical modulation was investigated, as shown in Fig. 3e. The current changes generated by light-assisted electrical pulses are larger than those caused by only electrical pulses, whether during weight increase or decrease. The differences in current changes are more significant in the first several enhancements/reductions, and tend to be smaller as the number of pulses increases. The training caused by each pulse will produce different responses to the weight update according to the present weight state. Therefore, the cumulative effect on the weight update ( $\Delta G$ ) does not follow a simple linear relationship. In order to investigate the NL change under the electrical modulation and the light-electrical co-modulation, 50 pulses were applied to induce the increase or decrease of the weights, respectively. The  $\Delta G$  under different modulations is plotted as a function of the number (N) of the pulses, as shown in Fig. 3f. The change of NL can be quantitatively described

**Figure 3** Comparison of synaptic behaviors of the device under electrical modulation only with that under light-assisted electrical modulation. (a) EPSCs triggered by electrical and light-electrical mixed pulses; (b) EPSC changes induced by electrical and mixed pulses as a function of the pulse amplitude; (c) IPSCs triggered by electrical and mixed pulses; (d) EPSC (labeled as E) and IPSC (labeled as I) changes induced by electrical and mixed pulses; (f)  $\Delta G$  generated by electrical and mixed pulses as a function of the pulse as a function of the pulse as a function of the pulse number in potentiation (labeled as P) and depression (labeled as D) state. Error bars in (b) and (d) are obtained from five different measurements.

as [41]

$$NL = \frac{\max \left| G_{p}(n) - G_{d}(n) \right|}{G_{p}(50) - G_{p}(1)},$$

(2)

where  $G_p(n)$  and  $G_d(n)$  are the conductance increment and reduction caused by the corresponding pulse  $(1 \le N \le 50)$ . The NL values calculated by Equation (2) under 20, 40, and 50 electrical modulation pulses are 0.118, 0.296 and 0.409, respectively. Interestingly, the calculated NL values under the same number of pulses under the comodulation are 0.080, 0.239 and 0.356, respectively, which are lower than those under the electrical modulation. Thus, the floating-gate photosensitive device shows enhanced degree and linearity of synaptic weight changes under light-electrical co-modulation, which is beneficial for improving the recognition rate in image identification applications.

Moreover, the floating-gate transistors also possess sy-

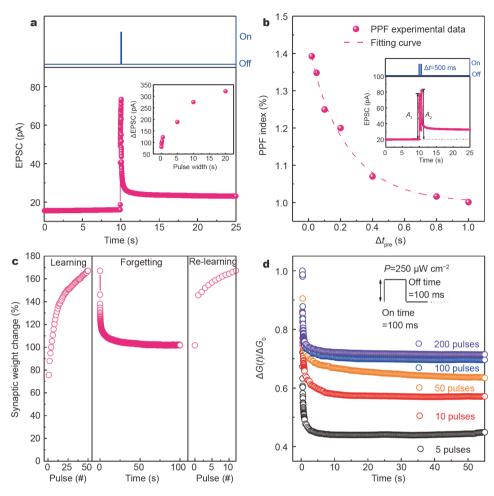

naptic behaviors induced by only light modulation, which is benefited from the strong light absorption capability of the CsPbBr<sub>3</sub> PQDs. Fig. 4a shows a typical EPSC behavior triggered by a light pulse ( $\lambda = 490 \text{ nm}$ , 100 ms,  $P = 250 \,\mu\text{W cm}^{-2}$ ) recorded at constant  $V_{ds} = -10 \,\text{V}$  and  $V_{\rm gs} = 0$  V. The inset illustrates that as the light pulse width increases from 50 ms to 20 s, the amplitude of the associated EPSC increases from 50 to 375 pA. The EPSC trigged by the optical stimulus keeps at a stable intermediate value instead of returning back to the initial value after the light pulse. The non-volatile memory effect could be attributed to the floating-gate device structure, and the detailed mechanism is illustrated in Fig. S6a. Optical-stimulated PPF was successfully imitated in the device by applying two consecutive light pulses (Fig. 4b). Further, the "learning experience" functions, including the processes of physiological learning, forgetting, and relearning behaviors, were demonstrated in the device un-

**Figure 4** Synaptic behaviors of the device under optical modulation. (a) EPSC triggered by a presynaptic light spike ( $\lambda = 490 \text{ nm}$ , 100 ms,  $P = 250 \,\mu\text{W cm}^{-2}$ ) and recorded at constant  $V_{ds} = -10 \text{ V}$  and  $V_{gs} = 0 \text{ V}$  (inset: EPSC change as a function of the pulse width); (b) dependence of the PPF index on the inter-spike interval (inset: EPSC generated by two successive light pulses); (c) demonstration of learning, forgetting, and re-learning behaviors; (d) decay of normalized channel conductance change ( $\Delta G/\Delta G_0$ ) recorded after the last pulse for various pulse numbers.

der optical modulation. As shown in Fig. 4c, the synaptic weight changes induced by 50 consecutive light stimuli exhibit gradual increase, which refers to the learning process. After the light pulses, the synaptic weight appears an immediate decay firstly and then shows a slow reduction process, which is similar to the behavior of forgetting in human psychology. Interestingly, it only takes 12 same light pulses to increase the synaptic weight back to the preceding level at the second "learning process", which can be considered as the imitation of the "relearning" behavior. In addition, the forgetting behavior was further investigated with different numbers of light pulses, as shown in Fig. 4d. The final normalized channel conductance change increases from 0.45 to 0.74 as the number of light pulses increases from 5 to 100, namely the memory level improves as the light pulse number

increases.

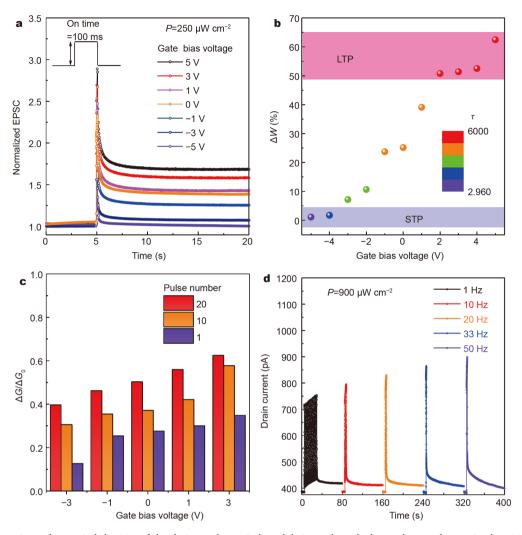

The effect of gate voltage on the synaptic performance of floating-gate synaptic transistors under light modulation was also investigated. Under different gate biases, the device showed different light-stimulated synaptic plasticity, as shown in Fig. 5a. At  $V_{gs} = -5$  V, the normalized EPSC curve eventually returned to the baseline eventually, demonstrating an obvious volatility memory and typical STP. As  $V_{gs}$  increased from -5 to 5 V, the endcurrents of the EPSC curves increased gradually, and the devices showed a long-term plasticity (LTP) under  $V_{gs} = 5$  V. Fig. 5b illustrates the synaptic weight change as a function of gate bias. At  $V_{gs} = -5$  V, the steady-state weight change is 3% and the fitted decay  $\tau$  is 2.96 s, while at  $V_{gs} = 5$  V, the steady-state weight change and the fitted decay  $\tau$  are 63% and 5456 s, respectively. The detailed

Figure 5 Comparison of synaptic behaviors of the device under optical modulation only with that under gate bias-assisted optical modulation. (a) EPSCs trigged by light pulses under different gate biases; (b) synaptic weight change as a function of gate bias; (c) normalized channel conductance change ( $\Delta G/\Delta G_0$ ) for different pulse numbers and gate biases; (d) EPSC curves ( $V_{ds} = -10$  V and  $V_{gs} = -5$  V) in response to the successive light stimulus ( $\lambda = 490$  nm, 100 ms,  $P = 900 \,\mu$ W cm<sup>-2</sup>, 20 light pulses) with different frequencies.

mechanism is illustrated in Fig. S6b. Therefore, the memory effect of the device under light modulation, from short-term to long-term plasticity, can be adjusted by the gate bias. We further investigated the effect of light pulse number on the normalized synaptic weight change at different gate voltages. In brief, larger light pulse number and higher positive gate bias result in higher steady-state weight changes (Fig. S7). Fig. 5c summarizes the relationship between the normalized synaptic weight change and the gate bias under different light pulse numbers. Apparently, the synaptic weight can be extensively modulated *via* both pulse number and gate bias. A typical dynamic high-pass filtering function under light modulation was also achieved in our devices, as shown in

Fig. 5d and Fig. S8.

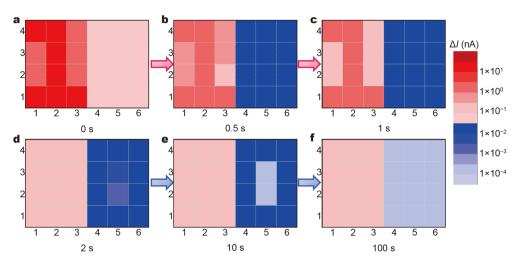

Finally, a device array was employed to demonstrate the pattern-learning and forgetting processes with tunable synaptic functions under optical and electrical co-modulation (Fig. 6). In a  $4\times6$  device array, gate bias pulses and light-assisted electrical modulation were applied to the devices in the left half part to generate a number pattern "1" (devices labeled as ① and ②, respectively, Fig. S9); while light pulses and gate bias-assisted light modulation were applied to the devices in the right half part to generate pattern "0" (devices labeled as ③ and ④, respectively, Fig. S9). Then, the current changes of the device array as a function of time are plotted in Fig. 6. The left part displays the pattern "1" immediately after the voltage

**Figure 6** Learning and forgetting processes of the patterns "0" and "1" with different synaptic weights and memory times in the device array under optical and electrical co-modulation. Current changes as compared with the baselines for the device array after the stimulating pulses at (a) 0, (b) 0.5, (c) 1, (d) 2, (e) 10 and (f) 100 s.

pulses, because the light-assisted electrical modulation leads to larger EPSCs for the associated devices. Afterwards, the display of pattern "1" weakens gradually and completely disappears at 2 s, corresponding to STP. In contrast, the right part devices present similar current changes in a short time (around 1 s) after the stimulating pulses. After 2 s, the pattern "0" starts to appear since the gate bias-assisted light modulation provides the devices with higher steady-state current change after the pulses, as compared with the only light modulation. The display of the pattern "0" can last till dozens of seconds, which is associated with LTP. These results thus demonstrate that our device possesses tunable synaptic weights and memory times.

#### **CONCLUSIONS**

To summarize, we have reported a floating-gate photosensitive synaptic transistor with charge-trapping CsPbBr<sub>3</sub> PQDs and ALD-grown Al<sub>2</sub>O<sub>3</sub> tunneling layer. With combining advantages of the ultrathin Al<sub>2</sub>O<sub>3</sub> film and the photosensitive CsPbBr<sub>3</sub> PQD charge-trapping layer, the synaptic functions of the devices can be extensively adjusted by electrical and optical signal comodulation. Using light as a modulation terminal can significantly increase the weight change under electrical stimulation while avoiding the deterioration of the weight update NL. Meanwhile, the memory effect under light stimulation can be significantly enhanced by applying gate bias. The device array further demonstrated learning and forgetting processes of the patterns "0" and "1" with different synaptic weights and memory times. Therefore, our device with tunable synaptic functions possesses potential for building complex and robust artificial neural networks.

## Received 10 August 2020; accepted 30 September 2020; published online 4 December 2020

- Mennel L, Symonowicz J, Wachter S, *et al.* Ultrafast machine vision with 2D material neural network image sensors. Nature, 2020, 579: 62–66

- 2 Shi W, Guo Y, Liu Y. When flexible organic field-effect transistors meet biomimetics: A prospective view of the internet of things. Adv Mater, 2020, 32: 1901493

- 3 Roy K, Jaiswal A, Panda P. Towards spike-based machine intelligence with neuromorphic computing. Nature, 2019, 575: 607– 617

- 4 Zidan MA, Strachan JP, Lu WD. The future of electronics based on memristive systems. Nat Electron, 2018, 1: 22–29

- 5 Kuzum D, Yu S, Philip Wong HS. Synaptic electronics: Materials, devices and applications. Nanotechnology, 2013, 24: 382001

- 6 Zhu LQ, Wan CJ, Guo LQ, et al. Artificial synapse network on inorganic proton conductor for neuromorphic systems. Nat Commun, 2014, 5: 3158

- 7 van de Burgt Y, Melianas A, Keene ST, et al. Organic electronics for neuromorphic computing. Nat Electron, 2018, 1: 386–397

- 8 Wang Y, Lv Z, Chen J, et al. Photonic synapses based on inorganic perovskite quantum dots for neuromorphic computing. Adv Mater, 2018, 30: 1802883

- 9 Sanchez Esqueda I, Yan X, Rutherglen C, et al. Aligned carbon nanotube synaptic transistors for large-scale neuromorphic computing. ACS Nano, 2018, 12: 7352–7361

- 10 Tian H, Cao X, Xie Y, et al. Emulating bilingual synaptic response using a junction-based artificial synaptic device. ACS Nano, 2017, 11: 7156–7163

- 11 Wang H, Zhao Q, Ni Z, et al. A ferroelectric/electrochemical modulated organic synapse for ultraflexible, artificial visual-perception system. Adv Mater, 2018, 30: 1803961

- 12 John RA, Liu F, Chien NA, *et al.* Synergistic gating of electro-ionophotoactive 2D chalcogenide neuristors: Coexistence of Hebbian and homeostatic synaptic metaplasticity. Adv Mater, 2018, 30: 1800220

- 13 Dai S, Zhao Y, Wang Y, *et al.* Recent advances in transistor-based artificial synapses. Adv Funct Mater, 2019, 29: 1903700

- 14 Yu JJ, Liang LY, Hu LX, *et al.* Optoelectronic neuromorphic thinfilm transistors capable of selective attention and with ultra-low power dissipation. Nano Energy, 2019, 62: 772–780

- 15 Zhu J, Zhang T, Yang Y, *et al.* A comprehensive review on emerging artificial neuromorphic devices. Appl Phys Rev, 2020, 7: 011312

- 16 Park HL, Lee Y, Kim N, et al. Flexible neuromorphic electronics for computing, soft robotics, and neuroprosthetics. Adv Mater, 2020, 32: 1903558

- 17 Tang J, Yuan F, Shen X, *et al.* Bridging biological and artificial neural networks with emerging neuromorphic devices: Fundamentals, progress, and challenges. Adv Mater, 2019, 31: 1902761

- 18 Fuller EJ, Keene ST, Melianas A, et al. Parallel programming of an ionic floating-gate memory array for scalable neuromorphic computing. Science, 2019, 364: 570–574

- 19 Dai S, Wu X, Liu D, *et al.* Light-stimulated synaptic devices utilizing interfacial effect of organic field-effect transistors. ACS Appl Mater Interfaces, 2018, 10: 21472–21480

- 20 Sun Z, Pedretti G, Bricalli A, *et al.* One-step regression and classification with cross-point resistive memory arrays. Sci Adv, 2020, 6: eaay2378

- 21 Wang CY, Liang SJ, Wang S, *et al.* Gate-tunable van der Waals heterostructure for reconfigurable neural network vision sensor. Sci Adv, 2020, 6: eaba6173

- 22 Kim Y, Chortos A, Xu W, *et al.* A bioinspired flexible organic artificial afferent nerve. Science, 2018, 360: 998–1003

- 23 Shim H, Sim K, Ershad F, *et al.* Stretchable elastic synaptic transistors for neurologically integrated soft engineering systems. Sci Adv, 2019, 5: eaax4961

- 24 Zhu X, Wang Q, Lu WD. Memristor networks for real-time neural activity analysis. Nat Commun, 2020, 11: 2439

- 25 Han H, Xu Z, Guo K, *et al.* Tunable synaptic plasticity in crystallized conjugated polymer nanowire artificial synapses. Adv Intelligent Syst, 2020, 2: 1900176

- 26 Kim S, Lee Y, Park M, et al. Dimensionality dependent plasticity in halide perovskite artificial synapses for neuromorphic computing. Adv Electron Mater, 2019, 5: 1900008

- 27 Li E, Lin W, Yan Y, *et al.* Synaptic transistor capable of accelerated learning induced by temperature-facilitated modulation of synaptic plasticity. ACS Appl Mater Interfaces, 2019, 11: 46008–46016

- 28 Li X, Wu Y, Zhang S, et al. CsPbX<sub>3</sub> quantum dots for lighting and displays: Room-temperature synthesis, photoluminescence superiorities, underlying origins and white light-emitting diodes. Adv Funct Mater, 2016, 26: 2435–2445

- 29 Lv Z, Chen M, Qian F, et al. Mimicking neuroplasticity in a hybrid biopolymer transistor by dual modes modulation. Adv Funct Mater, 2019, 29: 1902374

- 30 Liu Y, Tang S, Banerjee SK. Tunnel oxide thickness dependence of activation energy for retention time in SiGe quantum dot flash memory. Appl Phys Lett, 2006, 88: 213504

- 31 Yan D, Shi T, Zang Z, *et al.* Ultrastable CsPbBr<sub>3</sub> perovskite quantum dot and their enhanced amplified spontaneous emission by surface ligand modification. Small, 2019, 15: 1901173

- 32 Wang K, Dai S, Zhao Y, et al. Light-stimulated synaptic transistors

fabricated by a facile solution process based on inorganic perovskite quantum dots and organic semiconductors. Small, 2019, 15: 1900010

- 33 Shen K, Xu H, Li X, *et al.* Flexible and self-powered photodetector arrays based on all-inorganic CsPbBr<sub>3</sub> quantum dots. Adv Mater, 2020, 32: 2000004

- 34 Chen JY, Chiu YC, Li YT, *et al.* Nonvolatile perovskite-based photomemory with a multilevel memory behavior. Adv Mater, 2017, 29: 1702217

- 35 Abbott LF, Regehr WG. Synaptic computation. Nature, 2004, 431: 796–803

- 36 Sun J, Oh S, Choi Y, *et al.* Optoelectronic synapse based on IGZOalkylated graphene oxide hybrid structure. Adv Funct Mater, 2018, 28: 1804397

- 37 Fu YM, Wan CJ, Yu F, *et al.* Electrolyte gated oxide pseudodiode for inhibitory synapse applications. Adv Electron Mater, 2018, 4: 1800371

- 38 Shi J, Ha SD, Zhou Y, *et al.* A correlated nickelate synaptic transistor. Nat Commun, 2013, 4: 2676

- 39 Ryu JJ, Jeon K, Kim G, *et al.* Highly linear and symmetric weight modification in HfO<sub>2</sub>-based memristive devices for high-precision weight entries. Adv Electron Mater, 2020, 6: 2000434

- 40 Chen X, Pan J, Fu J, et al. Polyoxometalates-modulated reduced graphene oxide flash memory with ambipolar trapping as bidirectional artificial synapse. Adv Electron Mater, 2018, 4: 1800444

- 41 Kim S, Choi B, Lim M, *et al.* Pattern recognition using carbon nanotube synaptic transistors with an adjustable weight update protocol. ACS Nano, 2017, 11: 2814–2822

- 42 Ren Y, Yang J, Zhou L, *et al.* Gate-tunable synaptic plasticity through controlled polarity of charge trapping in fullerene composites. Adv Funct Mater, 2018, 28: 1805599

- 43 Yu F, Zhu LQ, Gao WT, *et al.* Chitosan-based polysaccharidegated flexible indium tin oxide synaptic transistor with learning abilities. ACS Appl Mater Interfaces, 2018, 10: 16881–16886

**Acknowledgements** This work was supported by the National Natural Science Foundation of China (61874029).

**Author contributions** Wu X and Ding SJ designed the devices and experiments; Li L performed the experiments; Li L and Wu X wrote the paper; all the authors discussed the results.

**Conflict of interest** The authors declare that they have no conflict of interest.

**Supplementary information** Experimental details and supporting data are available in the online version of the paper.

Lingkai Li received his BE degree in microelectronics from Xidian University, Xi'an, China, in 2017, and MSc degree from the School of Microelectronics, Fudan University, Shanghai, China, in 2020. His research interest is thin-film synaptic transistors. He is currently an integrated circuit (IC) verification engineer in Huawei company.

Xiaohan Wu is now an associate professor at the School of Microelectronics, Fudan University, China. He received his PhD degree from the University of Montpellier I, France in 2013, and was employed as an Assistant Professor in the School of Materials Science and Engineering, Tongji University till 2018. His research interest refers to optoelectronics, flexible devices and atomic layer technology.

Shi-Jin Ding received his PhD degree from Fudan University in China in 2001. He worked at Kiel University in Germany from 2001 to 2002, and at the National University of Singapore from 2003 to 2004. He joined Fudan University in 2005, and became a full professor in 2008. His current research interests include metal oxide semiconductor thin-film transistor and memory devices, solid-state ultrahigh density capacitors, and atomic layer deposition of novel materials for advanced integration circuits.

# 用于神经形态计算的具有可调功能的浮栅光敏突触晶体管

李凌凯, 王晓琳, 裴俊翔, 刘文军, 吴小晗\*, 张卫, 丁士进\*

摘要 将记忆和处理功能整合为一个单元的突触器件在神经形态 计算、软机器人和人机交互等方面具有广泛的应用潜力. 然而,先 前报道的大多数突触器件一旦制造出来就表现出固定的性能,这 限制了它们在不同场景中的应用. 在这里,我们报道了一种以钙钛 矿量子点为电荷俘获层、以原子层沉积的Al<sub>2</sub>O<sub>3</sub>为隧穿层的浮栅光 敏突触晶体管. 在电或者光信号的刺激下,该器件都能展示出典型 的突触行为,包括兴奋性突触后电流、双脉冲异化和动态滤波特 性. 进一步地,器件中高质量Al<sub>2</sub>O<sub>3</sub>隧穿层和高光敏的钙钛矿量子 点电荷俘获层使得其突触可塑性可以在光和电信号的共同调制下 实现大范围的调节. 在电调制过程中施加光信号可以显著改善突 触权重的变化和权值更新的非线性,而光调制下的记忆效应可以 明显地受到栅极电压的调节. 该器件的阵列进一步展示了对图案 "0"和"1"的不同突触权重或记忆时间的学习和遗忘过程. 综上,这 项工作为构建复杂而稳固的人工神经网络提供了具有可调功能的 突触器件.