Abstract

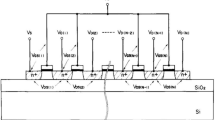

For the semiconductor industry, Complementary metal oxide semiconductor is contemplated to be outstanding because of synthesis in Integrated Circuits (ICs). As transistor size is lessened exponentially, there is a rampant increment in the number of transistors on a chip. This potential increase in the number of transistors on a chip is achieved by scaling of Metal oxide semiconductor field-effect transistor (MOSFET). In the traditional MOSFET, with the proper applied gate voltage, the electric field penetrates through the channel with the associated junctions. But as the technology is scaling down, for the proper device operation the concentration in the channel should be high. But with the introduction of Buried oxide and ground plane, the electric field passes through this buried oxide layer but this inturn increases the oxide capacitance. So there is a need for advanced MOSFET structures. With scaling, the attributes of gadgets have also deteriorated. Considerable advanced MOSFETs like Multigate transistors (Double gate, triple gate, Gate all around), Junctionless transistors, and Tunnel FETs are recommended recently. These are expected to promote Moore’s law and scaling of transistors to the next decade and extended enhancement in computer work. A lot of transistors (TFT, Multigate transistors, Junctionless transistors, and TFETs) are investigated dealing with their structure and technology. The attributes of these transistors are also deliberated in this paper.

Similar content being viewed by others

Data Availability

The referred papers will be available on request.

References

Ferain I, Colinge C, Colinge J (2011) Multigate transistors as the future of classical metal–oxide–semiconductor field-effect transistors. Nature 479:310–316

Girija Sravani K, Guha K, Srinivasa Rao K (2018) An investigation on capacitance modeling of step strcture RF MEMS perforated shunt switch. Proceedings of International Conference on 2018 IEEE Electron Device Kolkata Conference, EDKCON 2018, pp 302- 311

Aditya M, Rao KS, Sravani KG, Guha K (2021) Simulation and drain current performance analysis of High-K Gate Dielectric FinFET. Silicon. https://doi.org/10.1007/s12633-021-01176-3

Srinivasa Rao K, Thalluri LN, Guha K, Girija Sravani K (2018) Fabrication and characterization of capacitive RF MEMS perforated switch. IEEE Access, pp 77519–77528

Girija Sravani K, Srinivasa Rao K (2018) ‘Analysis of RF MEMS shunt capacitive switch with uniform and non-uniform meanders. Microsyst Technol 24(2):1309–1315

Sateesh J, Girija Sravani K, Akshay Kumar R, Guha K, Srinivasa Rao K (2018) Design and flow analysis of MEMS based piezo-electric micro pump. Microsyst Technol 24(3):1609–1614

Samal A, Tripathi SL, Mohapatra SK (2020) A Journey from Bulk MOSFET to 3 nm and Beyond. Trans Electr Electron Mater 21:443–455

Mendiratta N, Tripathi SL (2020) A review on performance comparison of advanced MOSFET structures below 45 nm technology node. J Semicond 41(6):061401. https://doi.org/10.1088/1674-4926/41/6/061401

Uemoto Y, Fujii E, Emoto F, Nakamura A, Senda K (1991) A high-voltage polysilicon TFT with multigate structures. IEEE Trans Electron Devices 38(1):95–100

Yang J-W, Fossum JG (2005) On the feasibility of nanoscale triple-gate CMOS transistors. IEEE Trans Electron Devices 52(6):1159–1164

Castellani-Coulie K, Munteanu D, Autran JL, Ferlet-Cavrois V, Paillet P, Baggio J (2006) Analysis of 45-nm multi-gate transistors behavior under heavy ion irradiation by 3-D device simulation. IEEE Trans Nucl Sci 53(6):3265–3270

Ray B, Mahapatra S (2008) Modeling and analysis of body potential of cylindrical gate-all-around nanowire transistor. IEEE Trans Electron Devices 55(9):2409–2416

Sallese J, Chevillon N, Lallement C, Iniguez B, Pregaldiny F (2011) Charge-based modeling of Junctionless double-gate field-effect transistors. IEEE Trans Electron Devices 58(8):2628–2637

Ho B, Sun X, Shin C, Liu TK (2013) Design optimization of Multigate bulk MOSFETs. IEEE Trans Electron Devices 60(1):28–33

Yu R, Das S, Ferain I, Razavi P, Shayesteh M, Kranti A, Duffy R, Colinge J (2012) Device design and estimated performance for p-Type Junctionless transistors on bulk germanium substrates. IEEE Trans Electron Devices 59:2308–2313

Aditya M, Srinivasa Rao K, Sravani K, Guha K (2021) Design, simulation and analysis of high-K gate dielectric FinField effect transistor. Int J Nano Dimens 12(3):305–309. https://doi.org/10.22034/ijnd.2021.681554

Sonali M, Aravind K, Keerthika G, Srinivasa Rao K (2018) Design and electromechanical analysis of RF MEMS switch for low actuation voltage. J Adv Res Dyn Control Syst 10(2 Special Issue):357-362

Girija Sravani K, Guha K, Srinivasa Rao K (2018) Analysis on selection of beam material for novel step structured RF-MEMS switch used for satellite communication applications. Trans Electr Electron Mater 19(6):467–474

Vijaya Prasad K, Kishore PVV, Srinivasa Rao O (2019) ‘Skeleton based view invariant human action recognition using convolutional neural networks’. International Journal of Recent Technology Engineering 8(2):4860–4867

Girija Sravani K, Guha K, Srinivasa Rao K (2019) ‘Design and Analysis of Serpentine Flexure Based RF MEMS Switch for High Isolation with Low Pull-in voltage’. Trans Electr Electron Mater 20(2):154–164

Kolanti T, Vemu S, Vobulapuram R, Srinivasa K (2018) Modeling of CMS-based nonuniform interconnects using FDTD technique. Int J Circuit Theory Appl 47. https://doi.org/10.1002/cta.2568

Prasad GRK, Srinivas Babu PS, Siddaiah N, Srinivasa Rao K (2017),’Design and simulation of MEMS based sensor for early detection of PD’,2016 International Conference on Electrical, Electronics, Communication, Computer and Optimization Techniques, ICEECCOT

Hwang B-W, Yang J-W, Lee S-H (2015) Explicit analytical current-voltage model for double-gate Junctionless transistors. IEEE Trans Electron Devices Inst Electr Electron Eng (IEEE) 62(1):171–177

Pan A, Chen S, Chui CO (2013) Electrostatic modeling and insights regarding Multigate lateral tunneling transistors. IEEE Trans Electron Devices 60(9):2712–2720

Ramaswamy S, Kumar MJ (2017) Double gate symmetric tunnel FET: investigation and analysis. In: IET Circuits Devices Syst 11(4):365-370, 7

Bose R, Roy JN (2019) 2D Surface potential and mobility modelling of doped/undoped symmetric double gate MOSFET. In: IET Circuits Devices Syst 13(5):571-575, 8

Sirohi A, Sahu C, Singh J (2019) Analog/RF performance investigation of dopingless FET for ultra-low power applications. IEEE Access 7:141810-141816

Horst F, Farokhnejad A, Zhao Q, Iñíguez B, Kloes A (2019) 2-D physics-based compact DC modeling of double-gate tunnel-FETs. IEEE Trans Electron Devices 66(1):132–138

Horst F, Farokhnejad A, Zhao Q, Iñíguez B, Kloes A (2019) 2-D physics-based compact DC modeling of double-gate tunnel-FETs. IEEE Trans Electron Devices 66(1):132-138

Acknowledgements

The authors would like thank the anonymous reviewers.

Author information

Authors and Affiliations

Contributions

Author 1 (Marupaka Aditya) studied the comparative analysis of advanced FETs and wrote the paper. Author 2 (K.Srinivasa Rao) calibrated the results for applications and wrote the paper. Author 3 (Balaji B) compared the threshold voltage calculations of advanced FETs and wrote the paper. Author 4 (K. Girija Sravani) given future directions of advance FETs and wrote the paper.

Corresponding author

Ethics declarations

Conflict of Interest

Authors declare no conflict of Interest.

Ethics Approval

The authors declare that they have no known competing financial interest or personal relationships that could have appeared to influence the work reported in this paper.

Consent to Participate

All authors voluntarily agree to participate in this review paper.

Consent for Publication

All authors give the permission to the Journal to publish this review paper.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Aditya, M., Rao, K.S., Balaji, B. et al. Comparison of Drain Current Characteristics of Advanced MOSFET Structures - a Review. Silicon 14, 8269–8276 (2022). https://doi.org/10.1007/s12633-021-01638-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01638-8