# An 18-28 GHz dual-mode down-converter IC for 5G applications

Saeed Naghavi<sup>1</sup> · Kaisa Ryynänen<sup>1</sup> · Mahwish Zahra<sup>1</sup> · Aleksi Korsman<sup>1</sup> · Kari Stadius<sup>1</sup> · Marko Kosunen<sup>1</sup> · Vishnu Unnikrishnan<sup>2</sup> · Lauri Anttila<sup>2</sup> · Mikko Valkama<sup>2</sup> · Jussi Ryynänen<sup>1</sup>

Received: 4 July 2022 / Revised: 25 November 2023 / Accepted: 14 December 2023 / Published online: 21 January 2024 © The Author(s) 2024

#### **Abstract**

Emerging spectrum trends require a higher integration of 5G New Radio Frequency Range 1 (FR1) and Frequency Range 2 (FR2) bands to enhance the availability of spectrum and spectrum-sharing opportunities. To enable the reception of both FR1 and FR2 bands in a seamless hardware entity, we propose combining homodyne and heterodyne architectures. This necessitates the incorporation of a down-converter module that transfers the incoming signals from FR2 bands down to FR1, ensuring compatibility with an FR1 direct-conversion receiver (DCR) for the final signal reception. The primary focus of this paper is the design and implementation of the required integrated down-converter. The module includes an integrated balun, a low-noise amplifier (LNA) with a bypass mode, a dual-mode mixer, and an intermediate frequency (IF) amplifier. The introduced bypass mode helps to further elevate the linearity performance compared to the nominal mode. The bypass mode is designed for joint communication and sensing operation to avoid the compression of the receiver. This work also incorporates a local oscillator (LO) signal distribution network with phase tuning elements using a mixed-signal approach. The circuit is implemented in a 22-nm CMOS process, and the active die area is 0.6 mm². The measurements demonstrate that the implemented chip can efficiently perform the required frequency conversion over a wide frequency range of 18–28 GHz. Conversion gain of 4.5–7.5 dB, noise figure of 15–19.7 dB, 1 dB compression point (IP1dB) of – 16 to – 10 dBm, and input third-order intercept point (IIP3) of – 5 to 0 dBm are achieved. The measured IP1 dB and IIP3 for the bypass mode are +0.5 to +4.5 dBm and +8.5 to +10 dBm, respectively.

**Keywords**  $5G \cdot Down\text{-converter} \cdot Frequency converter \cdot Heterodyne \cdot Joint communication and sensing \cdot Millimeter wave \cdot Modular receiver \cdot New radio (NR)$

## 1 Introduction

5 G communication brings new features and applications to the users, such as high data-rate communication, sensing and security, industrial 5G, health and medical, and transceivers requiring ultra-low latency and high reliability. Millimeter wave frequency operation together with array transceivers will be widely utilized in future products. Within 3GPP standardization, first step is to shift to the FR2 band at 24.2–52.6 GHz [1]. Although several receiver front-ends have been published in the literature for either FR1 [2–4]

or FR2 [5–16], none of them can cover both FR1 and FR2 bands in one system. In the context of emerging spectrum trends, the combination of FR1 and FR2 bands increases the availability of spectrum and spectrum-sharing opportunities. This provides deployment flexibility, enhanced coverage (through the low frequency band FR1), and higher data rates (through the mmWave band FR2) for a 5G communication system. Therefore, developing hardware-efficient methods to enable communication over both FR1 and FR2 bands within a seamless hardware entity is a valid research direction for future 5G systems.

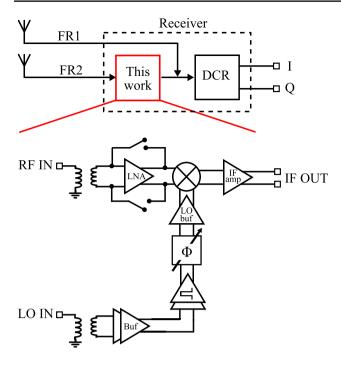

Our solution to cover both FR1 and FR2 bands is illustrated in Fig. 1. In this approach, the down-converter module converts the signal from FR2 bands down to the FR1 band in such a way that an FR1-compatible direct-conversion receiver (DCR) will follow for the final signal reception. In our approach, we convert the FR2 band signal down to 1–7 GHz which enables wideband signal

Saeed Naghavi saeed.naghavi@aalto.fi

Department of Electronics and Nanoengineering, Aalto University, Espoo, Finland

Department of Electrical Engineering, Tampere University, Tampere, Finland

Fig. 1 Concept of a 5G receiver for both FR1 and FR2 bands, and the structure of the implemented FR2 down-converter module

feed to the output. The module is a frequency converter consisting of an integrated balun, an LNA with a bypass mode, a dual-mode mixer, an IF amplifier, and an LO signal chain. The module has intentionally low gain and thus high linearity, to enable operation with a lower probability of compression in a hostile radio environment. Furthermore, it incorporates a bypass mode, as depicted in Fig. 1, in which the LNA is bypassed to further elevate linearity, and the dual-mode mixer is configured for passive operation. The bypass mode is used to avoid the compression of the receiver due to strong transmitter leakage during radar full-duplex operation for joint communication and sensing systems [17, 18].

We have designed a proof-of-concept IC for the down-converter module, fabricated on a 22-nm CMOS process. The circuit occupies an active die area of 0.6 mm<sup>2</sup> and operates over a frequency range of 18–28 GHz. Conversion gain of 4.5–7.5 dB, noise figure of 15–19.7 dB, 1-dB compression point (IP1dB) of – 16 to – 10 dBm, and input third-order intercept point (IIP3) of – 5 to 0 dBm are achieved. The measured IP1 dB and IIP3 for the bypass mode are +0.5 to +4.5 and +8.5 to +10, respectively. In Chapter II we describe the down-converter architecture in detail and Chapter III covers the circuit implementation. Chapter IV represents the measurement results and finally, Chapter V concludes the paper.

Figure 1 presents the overall system-level concept as well as the structure of the implemented down-converter module including the RF, LO, and IF blocks. The module is designed to work at 5G NR FR2 bands with a heterodyne operation, where the down-converted FR2 signals along with the received FR1 signals will be processed through a direct conversion receiver. The single-to-differential transformer and LNA are the first two stages of the implemented structure. The intention for employing an integrated transformer is to decouple the bonding pads from the gate terminals of the input transistors without using any electrostatic discharge (ESD) diodes. The LNA is followed by a double-balanced Gilbert-cell based mixer for down-converting the RF input signal to the desired IF. Finally, the last stage of the designed structure is a supersource-follower type IF-amplifier that provides a matched impedance for the IF output of the down-converter. This work also represents an inverter-based LO chain. Such a circuitry is usually designed by analog techniques for operation above 10 GHz, see e.g. [12, 19]. However, the deep submicron CMOS technology offers transit frequencies and maximum oscillation frequency of several hundreds of gigahertz [20], promoting the operation of the digital circuits above 10 GHz. The presented LO signal chain is designed by applying the mixed-signal techniques to explore this opportunity.

While operating at the highly occupied radio spectrum of modern urban environment, a radio receiver can potentially be affected by hostile signals from the nearby transmitters that can compress the signal path [21]. Furthermore, during radar-mode operation in joint sensing and communications scheme, strong signal may enter the receiver and the receiver needs to avoid compression. On the other hand, in this scenario sensitivity is not a major issue and we can tolerate high noise figure. As a counter-action for this issue an additional operating mode is implemented that can bypass the amplification stages and improve the linearity of the receiver. The mode control functionality of the proposed mixer is accomplished by switching between the resistive and capacitive loads in the IF outputs as well as whether or not to bypass the input transconductance stage of the mixer. In the nominal mode, the bypass switches around the LNA shown in Fig. 1 are open and the LNA can provide its nominal amplification. The next stage mixer is also configured to operate as an active mixer. In the bypass mode of operation, on the other hand, the bypass switches around the LNA are enabled and the input signal is directly applied to the common source nodes of the mixer's switching quad and in this way, the preceding gain stages including the LNA and the

transconductance stage of the mixer are both bypassed. The LNA employs a reconfigurable bias current using an IDAC and therefore it can be turned off in this mode so that the LNA's input and output nodes are sufficiently isolated. The mixer has also the capacitor loads enabled, and since the transconductance has already been bypassed, the mixer operates in passive mode with a good linearity as expected from the bypass mode.

# 3 Implementation

#### 3.1 LNA

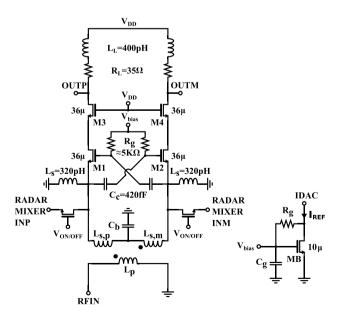

Figure 2 presents the structure of the LNA. The LNA is based on the capacitively cross-coupled common gate input stage structure [22, 23], and wideband gain response is achieved with a shunt-peaked load. Digital current control is utilized for tuning the bias current.

A transformer at the LNA input converts the input signal from single-ended to differential. In addition, the transformer provides ESD protection for the input transistor gates, and thus ESD protection diodes are avoided. The phase error of the differential signal was minimized with a center tap capacitor  $C_b$ . The transformer has a significant impact on the LNA operation, especially on the noise figure (NF) and input matching. The losses add to the total NF directly, since the transformer is the first stage in the chain. In this case, a stacked structure provided strong coupling and consequently minimized losses, and the EM-simulated transformer losses are 1.4–2.1 dB. The effect of the transformer on the input impedance was included in the LNA simulations by first

Fig. 2 The schematic of the LNA with the transformer at the input

EM-simulating the transformer and embedding the S-parameters to the LNA top-level simulations. The input matching circuit was designed by first tuning the transformer to the input frequency band. Then  $L_s$  and  $C_c$  were adjusted to provide the correct impedance.

The common-gate structure has a relatively high minimum NF, which is here decreased by a  $g_m$ -boosting method implemented with capacitive cross-coupling technique. The effective transconductance of the input transistors  $M_1$  and  $M_2$  is increased, and consequently their NF decreases. Furthermore, the structure provides wideband input matching together with the transformer. The wideband gain response was achieved with a shunt-peaked load implemented with a load inductor  $L_L$ , load resistor  $R_L$ , and the input capacitance of the following stage.  $L_L$  creates an additional zero to the transimpedance so the decreasing effect of the load capacitance is reduced [24]. The mixer input defines the load capacitance, and the frequency band of the gain response was tuned with the load inductor.

The LNA required configurable biasing because the LNA must be turned off in the bypass mode. The bypass switches were included in the LNA simulations, and in the off-state they degrade the LNA gain with less than 0.5 dB. IDAC provides the reference current  $I_{REF}$  for the current mirror visible in Fig. 2. Thus,  $I_{REF}$  can be tuned with control bits, and the LNA performance can be adjusted.

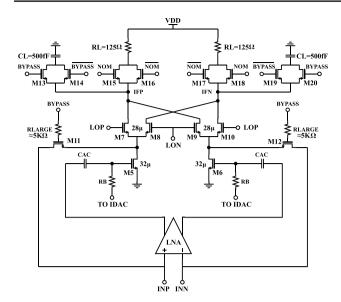

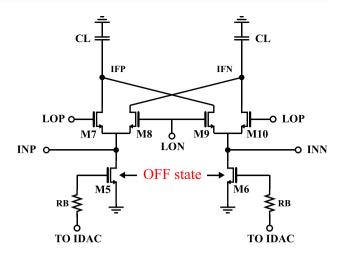

## 3.2 Dual-mode mixer

The overall structure of the implemented down-conversion mixer is shown in Fig. 3. The proposed mixer utilizes a well-known double-balanced Gilbert-cell based structure as the mixer core. The mixer is designed to enable both nominal and bypass modes. The mode control function is accomplished by switching between the resistive and capacitive loads in the IF outputs as well as whether or not to bypass the input transconductance stage of the mixer. The LNA is also bypassed via the M11 and M12 switches. As a specific design detail, the resistors in the gates of these switches improve the linearity by suppressing the fluctuations of the gate-drain and gate-source voltages [25, 26]. The achieved IIP3 improvement by employing this technique in the proposed structure is in the range of 3–5 dBm based on the simulation results.

#### 3.2.1 Nominal mode

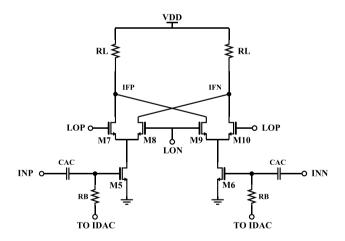

By enabling the nominal gain mode according to the requirements mentioned in Table 1 and neglecting the ON and OFF resistances of the configuration switches, the structure of the mixer can be redrawn as shown in Fig. 4. In this mode, resistive loads are in use and there will be a DC current flowing through the switching quad

Fig. 3 Overall structure of the dual mode mixer

Table 1 Configuration of the switches

| Switch                  | Nominal mode | Bypass mode |  |  |

|-------------------------|--------------|-------------|--|--|

| NOM                     | ON           | OFF         |  |  |

| $\overline{\text{NOM}}$ | OFF          | ON          |  |  |

| BYPASS                  | OFF          | ON          |  |  |

| BYPASS                  | ON           | OFF         |  |  |

Fig. 4 Down-conversion mixer: nominal mode

and consequently, the mixer operates as an active mixer. The implemented mixer in the nominal mode involves three main stages: input transconductance stage (M5, M6), switching stage (M7, M8, M9, M10), and load stage (RL). Resistive loads are preferred over the active load counterparts to provide a wider bandwidth for the mixer in the nominal mode. Transistors M5 and M6 are biased in

Fig. 5 Down-conversion mixer: bypass mode

the saturation region to provide enough gain for the input signal. On the other hand, the switch transistors, M7–M10, are all biased to conduct but near the pinch-off region to act as switches [27].

## 3.2.2 Bypass mode

By enabling the bypass mode according to the requirements mentioned in Table 1, the structure of the mixer can be redrawn as shown in Fig. 5. In the bypass mode, the input signal is directly applied from the output of the integrated transformer to the common-source nodes of the switching quad and in this way, the preceding gain stages are all bypassed. This will relax the saturation challenge of the down-converter in the presence of strong interferer. The mixer will also have capacitor loads enabled in this mode and since the transconductance has already been bypassed, there is no DC current flowing through the mixing quad. As a result, the mixer will operate in the passive mode with a good linearity performance as required in the bypass mode.

Passive mixers can operate in either ON or OFF overlap region depending on the dc gate bias of the switching quad. The ON overlap operation is preferred in the proposed structure since it is the desirable region from a linearity perspective [28]. In addition to the linearity performance, the input matching is another important parameter that should be taken into account since with the LNA bypassed the mixer is the first stage of the down-converter in the bypass mode. The required input matching is provided by a series combination of ON resistance of the switch transistors and scaled version of IF impedance formed by the implemented load capacitors (CL). These IF capacitors will also improve the linearity performance of the mixer by attenuating the out-of-band blockers [29, 30].

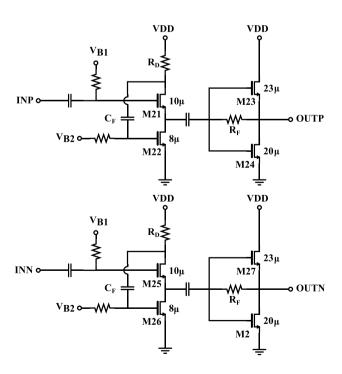

## 3.3 IF amplifier

The last circuit block of the implemented down-converter is the IF amplifier stage, which is shown in Fig. 6. This stage provides the required output matching for the implemented module. It also provides IF gain for the desired IF band as well as a sufficient suppression for the out-of-band interferences by the low-pass behavior. The proposed IF amplifier has a two-stage configuration composed of a super source follower followed by a self-biased inverter stage. The super-source follower is selected as the input stage because it provides wider bandwidth compared to the conventional common drain structure. The high input impedance of the super-source follower stage also prevents any loading effect and signal degradation on the mixer's output side. The output stage of the proposed IF amplifier is a self-biased inverter that provides few dB IF-signal amplification and a driving capability to external load. During the design phase the high-frequency non-ideal effects imposed by the chip pads, bonding wires, PCB pads, and PCB traces were taken into account while designing the proposed IF amplifier stage to be matched to a  $50\Omega$  load.

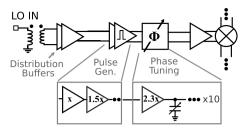

#### 3.4 LO chain

Figure 7 illustrates the block diagram for the LO signal chain. It was designed by applying mixed-signal techniques, and it serves as a step to analyze the feasibility of digital circuits operating above 10 GHz. The LO chain targets to provide

Fig. 6 Overall structure of the IF amplifier

Fig. 7 LO-signal chain

rail-to-rail signals for switching of mixers operating between 12 and 25 GHz LO frequency. It also incorporates varactor-based phase-tuning, to calibrate phase mismatches and study the possibility of LO phase-tuning for phased arrays.

The reference LO signal is fed in through a single-to-differential transformer and distributed across the chip with buffers. Located close to the mixers, pulse generation is the first block in the LO chain. At frequencies above 10 GHz, rail-to-rail signal generation and propagation requires special design considerations. The RC time-constant contributed by the load, interconnect and transistor parasitics limits the driving capability of CMOS circuits. Inverters are chosen as the building block for the LO signal chain as they present the smallest possible load. Pulse generation consists of a chain of inverters, and each inverter drives a load of 1.5 times its size. The inverter loading has been limited to allow amplification of the LO signal to create required waveforms.

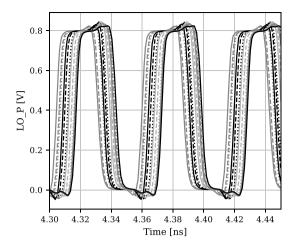

The pulse generator is followed by a phase-tuning element, which is composed of a series of 10 inverter-varactor pairs. The varactors are driven by 2.3 times the minimumsized inverter to maintain signal integrity at the highest frequency of the range, as well as drive the mixers. Digital controls (0,1) enable 1-bit of tuning control in each pair. The varactor-tuning block can calibrate phase mismatches between  $LO_P$  and  $LO_N$  signals or can serve phase-tuning for possible beamforming application. Figure 8 shows the post-layout simulation results at for the presented LO chain to demonstrate its phase-tuning capability. Here, one of the differential input signal LO<sub>P</sub> is phase-tuned by progressively changing varactor controls from V<sub>DD</sub> to ground. Overall delay tuning is 13 ps. This would correspond to a 30° beamsteering angle in a typical  $2 \times 2$  sub-array antenna at 28 GHz. These results indicate that the mixed-mode design methodology is feasible, yet the performance of this demonstration calls for improvements.

## 4 Measurements

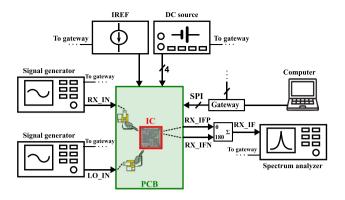

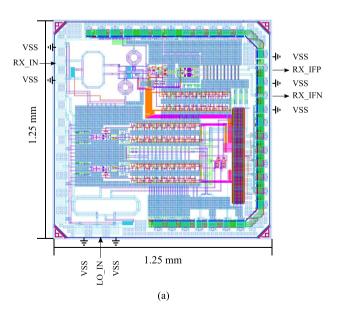

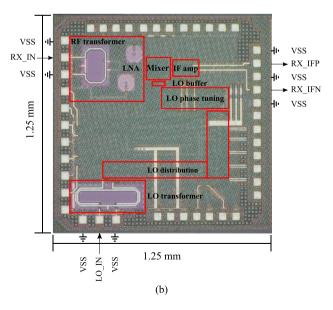

Figure 9 presents layout and microphotograph of the chip fabricated on a 22-nm CMOS process with a size of 1.25 mm × 1.25 mm including pads. RF transformer, LNA, mixer, IF

Fig. 8 Simulated time-domain waveforms for phase-tuning at 18 GHz

amplifier, and LO related blocks are the main elements of the receive path and are specified using red colored rectangles on the die microphotograph. Active die area is 0.6 mm². The implemented IC also includes two TX up-converting elements that are not the subject of this paper. The simplified measurement setup of the implemented down-converter is depicted in Fig. 10. The RF and LO inputs are provided using ground-signal-ground (GSG) probes through the custom designed low-parasitic pads. The EM-simulated parasitic capacitance of these mmw pads are only 20 fF. The IF outputs, on the other hand, are wire-bonded to the PCB and a micro-strip transmission line pair is employed to route them to the edge SMA connectors. Other lower frequency signals, including reference current, DC power supplies and SPIs are also provided through the PCB traces.

Fig. 10 Simplified measurement setup (CG)

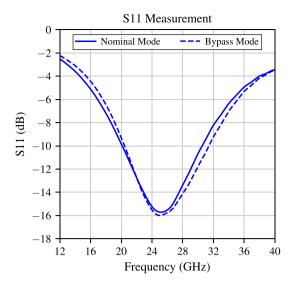

The functionality of the implemented down-converter module in both nominal and bypass modes was investigated through various measurements. Figure 11 shows the measured return loss at the RF input. The implemented on-chip transformer along with the input matching network of the nominal mode can preserve S11< -10 dB in a wide range of frequencies starting from 20 GHz up to 30 GHz. On the other hand, the input matching in the bypass mode is mostly defined by the on-chip transformer and the input impedance of the passive mixer. The measured S11 of the bypass mode verifies that the input power in this mode can also be efficiently transferred into the chip in a wide range of frequencies as nominal mode.

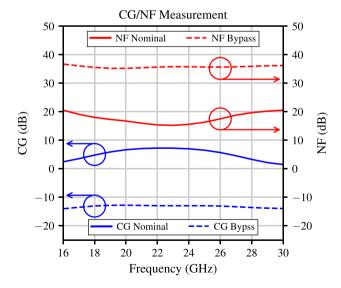

The measured conversion gain and noise figure of the module with an IF frequency of 7 GHz are shown in Fig. 12. The receive path can provide a conversion gain of 2.5–7.5

Fig. 9 Layout of the implemented down-converter IC (a), microphotograph of the implemented down-converter IC (b)

Fig. 11 Measured S11 in both modes of operations

dB and a noise figure of 15–20 dB over the frequency range in the nominal mode of operation. By enabling the bypass mode, the LNA and transconductance stage of the mixer are disabled and in this way, a good linearity performance at the cost of lower gain and higher noise figure is achieved from the bypass mode. As can be seen from Fig. 12, the bypass mode reduces the nominal conversion gain of the downconverter by about 18dB over the frequency range.

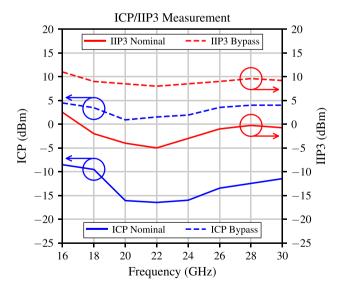

Finally, Fig. 13 presents the measured linearity performance of the implemented module, where the IIP3 is

measured using a two-tone separation of 100 MHz. The input P1dB is -16 to -10 dBm and the in-band IIP3 is -5 to 0 dBm at 18–28 GHz for the nominal mode of operation. For the bypass mode of operation, the input P1dB is +0.5 to +4.5 dBm and the in-band IIP3 is +8.5 to +10 dBm at 18–28 GHz. Performance summary and comparison with other down-converters in the same frequency range are provided in Table 2. As it can be seen, the implemented chip can achieve state of the art level performance metrics while providing a dual-mode operation at millimeter wave ranges.

#### 5 Conclusions

In this paper, a modular receiver architecture to enable the reception of input signals from both FR1 and FR2 bands using an hardware-efficient approach is presented. As the main requirement to achieve this goal, we have designed and implemented a proof-of-concept down-converter module that converts the signal from FR2 bands down to FR1. The measurement results show that the required frequency conversion is successfully implemented and a CG of 4.5–7.5 dB, NF of 15–19.7 dB, IP1dB of – 16 to – 10 dBm, and IIP3 of - 5 to 0 dBm were achieved for the proposed down-converter module over a wide frequency range of 18-28 GHz. The module also offers a bypass mode in addition to the nominal mode where even a higher linearity is achieved by bypassing the gain stages of the structure. The measured IP1dB and IIP3 for the bypass mode are +0.5 to +4.5 and +8.5 to +10, respectively.

Fig. 12 Measured conversion gain and noise figure in both modes of operations

Fig. 13 Measured 1-dB compression point and IIP3 in both modes of operations

Table 2 Performance summary and comparison with millimeter wave down-converters

|                         | This work                    | [31]<br>ICMMT<br>2022  | [32]<br>AICSP<br>2022 | [33]<br>EuMIC<br>2022  | [34]<br>IMS 2021       | [35]<br>RFIC 2021               | [36]<br>TCAS-II<br>2021   | [37]<br>TVLSI 2017      |

|-------------------------|------------------------------|------------------------|-----------------------|------------------------|------------------------|---------------------------------|---------------------------|-------------------------|

| Process<br>(CMOS)       | 22 nm                        | 65 nm                  | 180 nm                | 65 nm                  | 130 nm                 | 130 nm                          | 65 nm                     | 65 nm                   |

| Supply (V)              | 0.9                          | 1.1                    | 1.8                   | 1                      | 1.5                    | 2.7                             | 1                         | 1.2                     |

| RF Freq<br>(GHz)        | 18–28                        | 20–55                  | 5                     | 30–38                  | 23–25                  | 24–30                           | 24–40                     | 21.5–32.5               |

| IF Freq<br>(GHz)        | 1–7                          | 2                      | 0-0.1                 | 1                      | 0.1                    | 2–5                             | N/A                       | 0.001                   |

| CG (dB)                 | 4.5 –7.5                     | 2.41                   | $6^{2}$               | 4.3                    | 1.3-3                  | <b>-</b> 1                      | $7.2^{3}$                 | 15.5                    |

| NF (dB)                 | 15-20                        | 12.6-14.72             | $21^{2}$              | 21                     | 15.2-19.3              | < 15                            | $12.3^{3}$                | 11-20.5                 |

| S11 (dB)                | < - 8                        | N/A                    | N/A                   | N/A                    | < - 10                 | < - 10                          | N/A                       | < - 10                  |

| IP1dB<br>(dBm)          | $-11 \pm 4^{1}$              | -11.3                  | +1.92                 | - 1                    | -0.6-0                 | N/A                             | <b>-</b> 6.1 <sup>3</sup> | N/A                     |

| IIP3 (dBm)              | $-1 \pm 10^{1}$              | N/A                    | $+10.6^{2}$           | + 4                    | N/A                    | > + 14.5                        | $-2.5^3$                  | (-1.9)-(+8.8)           |

| Integration             | LNA + Mixer + IF<br>buf + LO | Mixer + IF<br>buf + LO | Mixer                 | Mixer + IF<br>buf + LO | Mixer + IF<br>buf + LO | T/R<br>SW + Mixer<br>+IF buf+LO | Mixer + IF<br>buf         | LNA + Mixer + IF<br>buf |

| Power (mW)              | $RX = 14.8/6.5^1$            | 7.48                   | $6.64^2$              | 10.4                   | 10.5                   | 210                             | 10.3                      | 7.1                     |

| Area (mm <sup>2</sup> ) | 0.6                          | 0.25                   | N/A                   | 0.44                   | 0.6                    | N/A                             | 0.4                       | 0.88                    |

<sup>&</sup>lt;sup>1</sup>Nominal mode result/Bypass mode result

Author Contributions SN: Mixer Design, Top-level arrangements, Tape-out activities, IC measurements kaisa ryynanen: LNA design, Transformer design, Tape-out activities MZ: LO design, Tape-out activities AK: IF amp design, Tape-out activities KS: Senior designer for microwave support, System design, Top-level arrangements, Tape-out activities MK: Senior designer for digital support (SPI, IO ring), System design, Top-level arrangements, Tape-out activities vishnu unnikrishnan: System design, Top-level arrangements. LA: System design (communication aspects) MV: System design (communication aspects) JR: Main supervisor of the project

Funding Open Access funding provided by Aalto University.

#### **Declarations**

Conflict of interest The authors declare no competing interests.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

#### References

- 3GPP. (2019). User Equipment (UE) radio transmission and reception; Part 3: Range 1 and Range 2 Interworking operation with other radios (Release 16). 3GPP TS 38.101-3.

- Lee, J., Han, S., Lee, J., Kang, B., Bae, J., Jang, J., et al. (2019).

A Sub-6-GHz 5G new radio RF Transceiver Supporting EN-DC With 3.15-Gb/s DL and 1.27-Gb/s UL in 14-nm FinFET CMOS. *IEEE Journal of Solid-State Circuits*, 54(12), 3541–3552. https://doi.org/10.1109/JSSC.2019.2938132

- Zahra, M., Kempi, I., Haarla, J., Antonov, Y., Khonsari, Z., Millunpalo, T., et al. (2020). A 2-5.5 GHz beamsteering receiver IC with 4-element vivaldi antenna array. *IEEE Transactions on Microwave Theory and Techniques*, 68(9), 3852–3860. https://doi.org/10.1109/TMTT.2020.2986754

- Lee, J., Kang, B., Joo, S., Lee, S., Lee, J., Kang, S., Jo, I., Ahn, S., Lee, J., Bae, J. & Ko, W., (2021). A low-power and low-cost 14nm FinFET RFIC supporting legacy cellular and 5G FR1. In Proceeding IEEE international solid-state circuits conference; p. 90–92.

- Kodak, U., & Rebeiz, GM. (2016). A 42mW 26-28 GHz phasedarray receive channel with 12 dB gain, 4 dB NF and 0 dBm IIP3 in 45nm CMOS SOI. In Proceeding IEEE radio frequency integrated circuits symposium (RFIC); p. 348–351.

- Yeh, Y. S., Walker, B., Balboni, E., & Floyd, B. (2017). A 28-GHz phased-array receiver front end with dual-vector distributed beamforming. *IEEE Journal of Solid-State Circuits*, 52(5), 1230–1244. https://doi.org/10.1109/JSSC.2016.2635664

- Garg, R., & Natarajan, A. S. (2017). A 28-GHz low-power phased-array receiver front-end with 360° rtps phase shift range. IEEE Transactions on Microwave Theory and Techniques,

<sup>&</sup>lt;sup>2</sup>Simulation result

<sup>&</sup>lt;sup>3</sup>Measured at 28 GHz RF frequency

- 65(11), 4703–4714. https://doi.org/10.1109/TMTT.2017.27074

- 8. Ding, Y., Vehring, S., Maurath, D., Gerfers, F., & Boeck, G. (2017). IEEE transactions on microwave theory and techniques. In *Proc. Asia-Pacific Microw. Conf.*, p. 1226–1229.

- Kim, H. T., Park, B. S., Song, S. S., Moon, T. S., Kim, S. H., Kim, J. M., et al. (2018). A 28-GHz CMOS direct conversion transceiver with packaged 2 × 4 antenna array for 5G cellular system. *IEEE Journal of Solid-State Circuits*, 53(5), 1245–1259. https:// doi.org/10.1109/JSSC.2018.2817606

- Mondal, S., Singh, R., Hussein, A. I., & Paramesh, J. (2018).

A 25–30 GHz fully-connected hybrid beamforming receiver for MIMO communication. *IEEE Journal of Solid-State Circuits*, 53(5), 1275–1287. https://doi.org/10.1109/JSSC.2018.2789402

- Kim, S., Kim, B., Lee, Y., Kim, S., & Shin, H. (2019). A 28GHz Direct Conversion Receiver in 65nm CMOS for 5G mmWave Radio. In *Proceeding 2019 international Soc design conference* p. 29–30.

- Pang, J., Wu, R., Wang, Y., Dome, M., Kato, H., Huang, H., et al. (2019). A 28-GHz CMOS phased-array transceiver based on LO phase-shifting architecture with gain invariant phase tuning for 5G new radio. *IEEE Journal of Solid-State Circuits*, 54(5), 1228–1242. https://doi.org/10.1109/JSSC.2019.2899734

- Shakib, S., Elkholy, M., Dunworth, J., Aparin, V., & Entesari, K. (2019). A wideband 28-GHz transmit-receive front-end for 5G handset phased arrays in 40-nm CMOS. *IEEE Transactions on Microwave Theory and Techniques*, 67(7), 2946–2963. https://doi.org/10.1109/TMTT.2019.2913645

- Shimura, T., Ohshima, T., & Ohashi, Y. (2019). A 28-GHz Phased-array Receiver with an On-chip BIST Function by using a Shielded Symmetrical Signal Distributor. In 2019 49th European Microwave Conference (EuMC), p. 618–621.

- Krishnamurthy, S., & Niknejad, AM. (2020). 10-35GHz passive mixer-first receiver achieving +14dBm in-band IIP3 for digital beam-forming arrays. In 2020 IEEE radio frequency integrated circuits symposium (RFIC) p. 275–278.

- Singh, R., Mondal, S., & Paramesh, J. (2020). A millimeter-wave receiver using a wideband low-noise amplifier with one-port coupled resonator loads. *IEEE Transactions on Microwave Theory* and Techniques, 68(9), 3794–3803. https://doi.org/10.1109/ TMTT.2020.2985676

- Barneto, C. B., Riihonen, T., Turunen, M., Anttila, L., Fleischer, M., Stadius, K., et al. (2019). Full-duplex OFDM radar with LTE and 5G NR waveforms: challenges, solutions, and measurements. *IEEE Transactions on Microwave Theory and Techniques*, 67(10), 4042–4054. https://doi.org/10.1109/TMTT.2019.2930510

- Barneto, C. B., Liyanaarachchi, S. D., Heino, M., Riihonen, T., & Valkama, M. (2021). Full duplex radio/radar technology: The enabler for advanced joint communication and sensing. *IEEE Wireless Communications*, 28(1), 82–88. https://doi.org/10.1109/ MWC.001.2000220

- Wu, L., Leung, H. F., Li, A., & Luong, H. C. (2017). A 4-element 60-GHz CMOS phased-array receiver with beamforming calibration. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 64(3), 642–652. https://doi.org/10.1109/TCSI.2016.26122

- Jan, CH., Agostinelli, M., Deshpande, H., El-Tanani, MA., Hafez, W., Jalan, U., et al. (2010). RF CMOS technology scaling in Highk/metal gate era for RF SoC (system-on-chip) applications. In 2010 international electron devices meeting, p. 27.2.1–27.2.4.

- Goel, A., Analui, B., & Hashemi, H. (2012). A 130-nm CMOS 100-Hz-6-GHz reconfigurable vector signal analyzer and software-defined receiver. *IEEE Transactions on Microwave Theory* and Techniques, 60(5), 1375–1389. https://doi.org/10.1109/ TMTT.2012.2190091

- Zhuo, W., Embabi, S., de Gyvez, JP., & Sanchez-Sinencio, E. (2000). Using capacitive cross-coupling technique in RF low noise amplifiers and down-conversion mixer design. In *Proceedings of the 26th European solid-state circuits conference*, p. 77–80.

- Zhuo, W., Li, X., Shekhar, S., Embabi, S. H. K., Pineda de Gyvez, J., Allstot, D. J., et al. (2005). A capacitor cross-coupled commongate low-noise amplifier. *IEEE Transactions on Circuits and Sys*tems II: Express Briefs, 52(12), 875–879.

- Shekhar, S., Walling, J. S., & Allstot, D. J. (2006). Bandwidth extension techniques for CMOS amplifiers. *IEEE Journal of Solid-State Circuits*, 41(11), 2424–2439. https://doi.org/10.1109/ JSSC.2006.883336

- Li, X. J., & Zhang, Y. P. (2010). Flipping the CMOS switch. *IEEE Microwave Magazine*, 11(1), 86–96. https://doi.org/10.1109/MMM.2009.935203

- Balasubramaniyan, A., & Bellaouar, A. (2018). RF/mmWave Front-End Module Switch in 22nm FDSOI Process. In 2018 IEEE SOI-3D-subthreshold microelectronics technology unified conference, p. 1–2.

- 27. Lin, C., Wu, P., Chang, H., & Wang, H. (2006). A 9–50-GHz Gilbert-cell down-conversion mixer in 0.13-m CMOS technology. *IEEE Microwave and Wireless Components Letters*, 16(5), 293–295. https://doi.org/10.1109/LMWC.2006.873492

- Kim, J., & Silva-Martinez, J. (2013). Low-power, low-cost CMOS direct-conversion receiver front-end for multistandard applications. *IEEE Journal of Solid-State Circuits*, 48(9), 2090–2103. https://doi.org/10.1109/JSSC.2013.2265781

- 29. Andrews, C., & Molnar, A. C. (2010). A passive mixer-first receiver with digitally controlled and widely tunable RF interface. *IEEE Journal of Solid-State Circuits*, 45(12), 2696–2708. https://doi.org/10.1109/JSSC.2010.2077151

- Mirzaei, A., & Darabi, H. (2011). Analysis of imperfections on performance of 4-phase passive-mixer-based high-Q bandpass filters in SAW-less Receivers. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 58(5), 879–892. https://doi.org/10. 1109/TCSI.2010.2089555

- Dai, Y., Wen, J., & Jin, N. (2022). A 20–55 GHz broadband low-power down-conversion mixer using 65-nm CMOS technology. In 2022 international conference on microwave and millimeter wave technology (ICMMT), IEEE. p. 1–3.

- Altuner, E., Özoğuz, I. S., & Yelten, M. B. (2022). High-linearity Gilbert-cell mixer design for cryogenic applications. *Analog Integrated Circuits and Signal Processing*, 113(2), 249–256.

- Li, M. H., Chen, C. N., Wang, Y., & Wang, H. A. (2021). 30-to-38 GHz active and passive combined down-conversion variable gain mixer with low OP 1dB variation in 65-nm CMOS. In 16th European microwave integrated circuits conference (EuMIC). IEEE, 2022, 55–58.

- Pan, J., He, J., Peng, Y., Wang, H., Chang, S., Huang, Q. & Li, J. (2021). A K-band active up/down bidirectional mixer in 130-nm CMOS. In 2021 IEEE MTT-S international microwave symposium (IMS), (pp. 294-296). IEEE

- Paidimarri, A., Yoshiyama, M., Plouchart, J. O., Valdes-Garcia, A., Lee, W., Okuyama, Y., et al. (2021). A High-Linearity, 24-30 GHz RF, Beamforming and Frequency-Conversion IC for Scalable 5G Phased Arrays. In 2021 IEEE radio frequency integrated circuits symposium (RFIC) p. 103–106.

- Bae, B., & Han, J. (2021). 24–40 GHz gain-boosted wideband CMOS down-conversion mixer employing body-effect control for 5G NR applications. *IEEE Transactions on Circuits and Systems* II: Express Briefs, 69(3), 1034–1038.

- Li, C. . H. ., Ko, C. . L. ., Kuo, M. . C. ., & Chang, D. . C. . (2017).

A 7.1-mW K/K<sub>a</sub>-band mixer with configurable bondwire resonators in 65-nm CMOS. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 25(9), 2635–2648. https://doi.org/10.1109/TVLSI.2017.2703807

**Publisher's Note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Saeed Naghavi received his B.Sc. and M.Sc. degrees in electrical engineering in 2011 and 2014, respectively. From 2015 to 2019, he contributed to various research projects in the field of front-end circuits for biomedical applications. Since 2020, he has been pursuing a D.Sc. degree at the Department of Electronics and Nano-Engineering, Aalto University, Espoo, Finland. His current research focuses on RF and microwave integrated circuits for wireless transceivers.

Kaisa Ryynänen Kaisa Ryynänen received the B.Sc. degree in electrical engineering and M.Sc. degree in microwave engineering from Aalto University, Espoo, Finland in 2020 and 2021, respectively. She is currently pursuing the D.Sc. (Tech.) degree at Aalto University school of Electrical Engineering. Her current research interests are millimeterwave receiver front-ends for communications and sensing.

Mahwish Zahra Mahwish Zahra received M.Sc. (Tech.) degree in electrical engineering from Tampere University of Technology, Tampere, Finland, in 2016 and D.Sc. (Tech.) degree from Aalto University, Espoo, Finland in 2022. She is currently an R&D engineer at Nordic Semiconductor, Turku, Finland. Her current research interests are analog and mixed-signal RF circuits, and receiver front-end design.

Aleksi Korsman received the M.Sc.(Tech) degree at Aalto University School of Electrical Engineering in 2022. He is currently pursuing the D.Sc. degree in the same location. His research interests include utilization and development of microprocessors for digital signal processing and communication applications.

Kari Stadius (Member, IEEE) received the M.Sc., Lic. Tech., and Doctor of Science degrees in electrical engineering from the Helsinki University of Technology, Helsinki, Finland, in 1994. 1997, and 2010, respectively. He is currently working as a staff scientist at the Department of Electronics and Nanoengineering, Aalto University School of Electrical Engineering. His research interests include RF and microwave circuits for communications, and analog and mixedmode circuit design. He has

authored or coauthored over a hundred refereed journal and conference papers, and he holds several patents.

Marko Kosunen Marko Kosunen (Member, IEEE) received his M.Sc., L.Sc. and D.Sc. (with honors) degrees from Helsinki University of Technology, Espoo, Finland, in 1998, 2001 and 2006, respectively. He is currently a Senior Researcher at Aalto University, Department of Electronics and Nanoengineering. Academic years 2017-2019 he visited Berkeley Wireless Research Center, UC Berkeley, on Marie Sklodowska-Curie grant from European Union. He has authored and co-authored

more than 90 journal and conference papers and holds several patents. His current research interests include programmatic circuit design methodologies, digital intensive and time-based transceiver circuits, and medical sensor electronics.

Vishnu Unnikrishnan (Member, IEEE) received the B.Tech. degree in electronics and communication engineering from Kannur University, India, in 2004, and the M.Sc. degree in electrical engineering as well as the Ph.D. degree in integrated circuits and systems both from Linköping University, Sweden, in 2012 and 2016 respectively. He is an Assistant Professor at the department of Electrical Engineering, Tampere University, Finland, since September 2021. From 2017 to 2021, he was a Postdoctoral Researcher at the dept. of

Electronics and Nanoengineering, Aalto University, Finland. From 2004 to 2009, he was with Bosch Engineering and Business Solutions, India. His research interests include energy-efficient integrated circuits and systems, digital-intensive radio/wireline transceiver architectures, digital implementation/enhancement of analog/mixed-signal functions in integrated circuits, and time-domain signal processing.

Lauri Anttila (Member, IEEE) received the M.Sc. degree in 2004 and the D.Sc. degree (with distinction) in 2011 from Tampere University of Technology (TUT), Finland, both in electrical engineering. Since 2016, he has been a University Researcher at the Department of Electrical Engineering, Tampere University (formerly TUT). In 2016-2017, he was a Visiting Research Fellow at the Department of Electronics and Nanoengineering, Aalto University, Finland. He has co-authored 100+ refer-

eed articles, as well as three book chapters. His research interests are in radio communications and signal processing, with a focus on the radio implementation challenges in systems such as 5G, full-duplex radio, and large-scale antenna systems.

Mikko Valkama (Fellow, IEEE) received the M.Sc. (Tech.) and D.Sc. (Tech.) Degrees (both with honors) in electrical engineering (EE) from Tampere University of Technology (TUT), Finland, in 2000 and 2001, respectively. In 2002, he received the Best Doctoral Thesis-award by the Finnish Academy of Science and Letters for his dissertation entitled "Advanced I/Q signal processing for wideband receivers: Models and algorithms". In 2003, he was working as a visiting post-doc research fellow with the Communications Systems and Signal Processing Institute at SDSU, San Diego, CA. Currently, he is a Full Professor and Department Head of Electrical Engineering at the newly formed Tampere University (TAU), Finland. His general research interests include radio communications, radio localization, and radio-based sensing, with particular emphasis on 5G and 6G mobile radio networks.

Jussi Ryynänen (Senior Member, IEEE) was born in Ilmajoki, Finland, in 1973. He received the M.Sc. and D.Sc. degrees in electrical engineering from the Helsinki University of Technology, Espoo, Finland, in 1998 and 2004, respectively. He is a full professor and the Dean of the School of Electrical Engineering, Aalto University, Espoo, Finland. He has authored or coauthored more than 200 refereed journal and conference papers in analog and RF circuit design. He holds seven patents on RF cir-

cuits. His research interests are integrated transceiver circuits for wireless applications. Prof. Ryynänen has served as a TPC Member for the European Solid-State Circuits Conference (ESSCIRC) and the IEEE International Solid-State Circuits Conference (ISSCC), and as a Guest Editor for the IEEE Journal of Solid-State Circuits.