# CrossMark

## ORIGINAL ARTICLE

# Stateless model checking for TSO and PSO

Parosh Aziz Abdulla $^1$  · Stavros Aronis $^1$  · Mohamed Faouzi Atig $^1$  · Bengt Jonsson $^1$  · Carl Leonardsson $^1$  · Konstantinos Sagonas $^1$

Received: 7 October 2015 / Accepted: 30 June 2016 / Published online: 7 July 2016 © Springer-Verlag Berlin Heidelberg 2016

**Abstract** We present a technique for efficient stateless model checking of programs that execute under the relaxed memory models TSO and PSO. The basis for our technique is a novel representation of executions under TSO and PSO, called *chronological traces*. Chronological traces induce a partial order relation on relaxed memory executions, capturing dependencies that are needed to represent the interaction via shared variables. They are optimal in the sense that they only distinguish computations that are inequivalent under the widely-used representation by Shasha and Snir. This allows an optimal dynamic partial order reduction algorithm to explore a minimal number of executions while still guaranteeing full coverage. We apply our techniques to check, under the TSO and PSO memory models, LLVM assembly produced for C/pthreads programs. Our experiments show that our technique reduces the verification effort for relaxed memory models to be almost that for the standard model of sequential consistency. This article is an extended version of Abdulla et al. (Tools and

This research was in part funded by the Uppsala Programming for Multicore Architectures Research Center (UPMARC). The research time of Stavros Aronis and Konstantinos Sagonas was supported in part by the EU FP7 STREP project RELEASE (287510).

□ Carl Leonardsson

□ carl.leonardsson@it.uu.se

□ carl.leonardsson@it.uu.se

□ carl.leonardsson@it.uu.se

□ carl.leonardsson@it.uu.se

□ carl.leonardsson@it.uu.se

□ carl.leonardsson@it.uu.se

Parosh Aziz Abdulla parosh@it.uu.se

Stavros Aronis stavros.aronis@it.uu.se

Mohamed Faouzi Atig mohamed\_faouzi.atig@it.uu.se

Bengt Jonsson bengt.jonsson@it.uu.se

Konstantinos Sagonas konstantinos.sagonas@it.uu.se

Department of Information Technology, Uppsala University, Box 337, 751 05 Uppsala, Sweden

algorithms for the construction and analysis of systems, Springer, New York, pp 353–367, 2015), appearing in TACAS 2015.

## 1 Introduction

Verification and testing of concurrent programs is difficult, since one must consider all the different ways in which instructions of different threads can be interleaved. To make matters worse, most architectures implement *relaxed memory models*, such as TSO and PSO [4,36], which make threads interact in even more and subtler ways than by standard interleaving. For example, a processor may reorder loads and stores by the same thread if they target different addresses, or it may buffer stores in a local queue.

A successful technique for finding concurrency bugs (i.e., defects that arise only under some thread schedulings), and for verifying their absence, is *stateless model checking* (SMC) [18], also known as *systematic concurrency testing* [24,39]. Starting from a test, i.e., a way to run a program and obtain some expected result, which is terminating and threadwisely deterministic (e.g. no data-nondeterminism), SMC systematically explores the set of all thread schedulings that are possible during runs of this test. A special runtime scheduler drives the SMC exploration by making decisions on scheduling whenever such decisions may affect the interaction between threads, so that the exploration covers all possible executions and detects any unexpected test results, program crashes, or assertion violations. The technique is completely automatic, has no false positives, does not suffer from memory explosion, and can easily reproduce the concurrency bugs it detects. SMC has been successfully implemented in tools such as VeriSoft [19], CHESS [28], and Concuerror [12].

There are two main problems for using SMC in programs that run under relaxed memory models (RMM). The first problem is that already under the standard model of *sequential consistency* (SC) the number of possible thread schedulings grows exponentially with the length of program execution. This problem has been addressed by *partial order reduction* (POR) techniques that achieve coverage of *all* thread schedulings, by exploring only a representative subset [13,17,30,38]. POR has been adapted to SMC in the form of *Dynamic Partial Order Reduction* (DPOR) [16], which has been further developed in recent years [1,22,24,32,33,37]. DPOR is based on augmenting each execution by a *happens-before relation*, which is a partial order that captures dependencies between operations of the threads. Two executions can be regarded as equivalent if they induce the same happens-before relation, and it is therefore sufficient to explore one execution in each equivalence class (called a *Mazurkiewicz trace* [27]). DPOR algorithms guarantee to explore at least one execution in each equivalence class, thus attaining full coverage with reduced cost. A recent optimal algorithm [1] guarantees to explore *exactly* one execution per equivalence class.

The second problem is that in order to extend SMC to handle relaxed memory models, the operational semantics of programs must be extended to represent the effects of RMM. The natural approach is to augment the program state with additional structures, e.g., store buffers in the case of TSO, that model the effects of RMM [3,5,29]. This causes blow-ups in the number of possible executions, in addition to those possible under SC. However, most of these additional executions are equivalent to some SC execution. To efficiently apply SMC to handle RMM, we must therefore extend DPOR to avoid redundant exploration of equivalent executions. The natural definition of "equivalent" under RMM can be derived from the abstract representation of executions due to Shasha and Snir [35], here called *Shasha–Snir traces*, which is often used in model checking and runtime verification [7,8,10,11,21,23].

Shasha—Snir traces consist of an ordering relation between dependent operations, which generalizes the standard happens-before relation on SC executions; indeed, under SC, the equivalence relation induced by Shasha—Snir traces coincides with Mazurkiewicz traces. It would thus be natural to base DPOR for RMM on the happens-before relation induced by Shasha—Snir traces. However, this relation is in general cyclic (due to reorderings possible under RMM) and can therefore not be used as a basis for DPOR (since it is not a partial order). To develop an efficient technique for SMC under RMM we therefore need to find a different representation of executions under RMM. The representation should define an acyclic happens-before relation. Also, the induced trace equivalence should coincide with the equivalence induced by Shasha—Snir traces.

Contribution In this paper, we show how to apply SMC to TSO and PSO in a way that achieves maximal possible reduction using DPOR, in the sense that redundant exploration of equivalent executions is avoided. A cornerstone in our contribution is a novel representation of executions under RMM, called chronological traces, which define a happens-before relation on the events in a carefully designed representation of program executions. Chronological traces are a succinct canonical representation of executions, in the sense that there is a one-to-one correspondence between chronological traces and Shasha-Snir traces. Furthermore, the happens-before relation induced by chronological traces is a partial order, and can therefore be used as a basis for DPOR. In particular, the Optimal-DPOR algorithm of [1] will explore exactly one execution per Shasha-Snir trace. In particular, for so-called *robust* programs that are not affected by RMM (these include data-race-free programs), Optimal-DPOR will explore as many executions under RMM as under SC: this follows from the one-to-one correspondence between chronological traces and Mazurkiewicz traces under SC. Furthermore, robustness can itself be considered a correctness criterion (as in e.g. [7,8,10,11]), which can also be automatically checked with our method (by checking whether the number of equivalence classes is increased when going from SC to RMM).

We show the power of our technique by using it to implement an efficient stateless model checker, which for C programs with pthreads explores all executions of a test-case or a program, up to some bounded length. During exploration of an execution, our implementation generates the corresponding chronological trace. Our implementation employs the source-DPOR algorithm [1], which is simpler than Optimal-DPOR, but about equally effective. Our experimental results for analyses under SC, TSO and PSO of a number of intensely racy benchmarks and programs written in C/pthreads, show that (i) the effort for verification under TSO and PSO is not much larger than the effort for verification under SC, and (ii) our implementation compares favourably against CBMC [6] and goto-instrument [5], on a number of terminating and data-deterministic benchmarks.

# 2 Overview of main concepts

This section informally motivates and explains the main concepts of the paper. To focus the presentation, we consider mainly the TSO model. TSO is relevant because it is implemented in the widely used ×86 as well as SPARC architectures. We first introduce TSO and its semantics. Thereafter we introduce Shasha–Snir traces, which abstractly represent the orderings between dependent events in an execution. Since Shasha–Snir traces may contain cycles, we introduce an extended representation of executions, for which a natural happens-before relation is acyclic. We then describe how this happens-before relation introduces

**Fig. 1** A program implementing the classic idiom of Dekker's mutual exclusion algorithm [15]

**Fig. 2** An execution of the program in Fig. 1. Notice that \$r = \$s = 0 at the end

```

p: store: \mathbf{x} := 1 // Enqueue store p: load: \$r := \mathbf{y} // Load value 0 q: store: \mathbf{y} := 1 // Enqueue store q: update // \mathbf{y} = 1 in memory q: load: \$s := \mathbf{x} // Load value 0 p: update // \mathbf{x} = 1 in memory

```

undesirable distinctions between executions, and how our new representation of chronological traces removes these distinctions. Finally, we illustrate how a DPOR algorithm exploits the happens-before relation induced by chronological traces to explore only a minimal number of executions, while still guaranteeing full coverage.

TSO: an Introduction TSO relaxes the ordering between stores and subsequent loads to different memory locations. This can be modelled operationally by equipping each thread with a store buffer [34], which is a FIFO queue that contains pending store operations. When a thread executes a store instruction, the store does not immediately affect memory. Instead it is delayed and enqueued in the store buffer. Nondeterministically, at some later point an update event occurs, dequeueing the oldest store from the store buffer and updating the memory correspondingly. Load instructions take effect immediately, without being delayed. Usually a load reads a value from memory. However, if the store buffer of the same thread contains a store to the same memory location, the value is instead taken from the most recent such store in the store buffer.

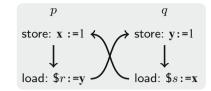

To see why this buffering semantics may cause unexpected program behaviors, consider the small program in Fig. 1. It consists of two threads p and q. The thread p first stores 1 to the memory location  $\mathbf{x}$ , and then loads the value at memory location  $\mathbf{y}$  into its register \$r. The thread q is similar, but with the roles of  $\mathbf{x}$  and  $\mathbf{y}$  reversed. All memory locations and registers are assumed to have initial values 0. It is easy to see that under the SC semantics, it is impossible for the program to terminate in a state where both registers \$r and \$s hold the value 0. However, under the buffering semantics of TSO, such a final state is possible. Fig. 2 shows one such program execution. We see that the store to  $\mathbf{x}$  happens at the beginning of the execution, but does not take effect with respect to memory until the very end of the execution. Thus the store to  $\mathbf{x}$  and the load to  $\mathbf{y}$  appear to take effect in an order opposite to how they occur in the program code. This allows the execution to terminate with \$r = \$s = 0.

Shasha–Snir traces for TSO Partial order reduction is based on the idea of capturing the possible orderings between dependent operations of different threads by means of a happens-before relation. When threads interact via shared variables, two instructions are considered dependent if they access the same global variable, and at least one is a write. For relaxed memory models, Shasha and Snir [35] introduced an abstract representation of executions, here referred to as Shasha–Snir traces, which captures such dependencies in a natural way. Shasha–Snir traces induce equivalence classes of executions. Under sequential consistency, those classes coincide with the Mazurkiewicz traces. Under a relaxed memory model, there

**Fig. 3** The Shasha–Snir trace corresponding to the execution in Fig. 2

**Fig. 4** A trace for the execution in Fig. 2 where updates are separated from stores

are also additional Shasha-Snir traces corresponding to the non-sequentially consistent executions.

A Shasha–Snir trace is a directed graph, where edges capture observed event orderings. The nodes in a Shasha–Snir trace are the executed instructions. For each thread, there are edges between each pair of subsequent instructions, creating a total order for each thread. For two instructions i and j in different threads, there is an edge  $i \rightarrow j$  in a trace when i causally precedes j. This happens when j reads a value that was written by i, when i reads a memory location that is subsequently updated by j, or when i and j are subsequent writes to the same memory location. In Fig. 3 we show the Shasha–Snir trace for the execution in Fig. 2.

Making the happens-before relation acyclic Shasha–Snir traces naturally represent the dependencies between operations in an execution, and are therefore a natural basis for applying DPOR. However, a major problem is that the happens-before relation induced by the edges is in general cyclic, and thus not a partial order. This can be seen already in the graph in Fig. 3. This problem can be addressed by adding nodes that represent explicit update events. That would be natural since such events occur in the representation of the execution in Fig. 2. When we consider the edges of the Shasha–Snir trace, we observe that although there is a conflict between p: load: \$r := y and q: store: y := 1, swapping their order in the execution in Fig. 2 has no observable effect; the load still gets the same value from memory. Therefore, we should only be concerned with the order of the load relative to the update event q: update.

These observations suggest to define a representation of traces that separates stores from updates. In Fig. 4 we have redrawn the trace from Fig. 3. Updates are separated from stores, and we order updates, rather than stores, with operations of other threads. Thus, there are edges between updates to and loads from the same memory location, and between two updates to the same memory location. In Fig. 4, there is an edge from each store to the corresponding update, reflecting the principle that the update cannot occur before the store. There are edges between loads and updates of the same memory location, reflecting that swapping their order will affect the observed values. However, notice that for this program there are no edges between the updates and loads of the same thread, since they access different memory locations.

Chronological traces for TSO Although the new representation is a valid partial order, it will in many cases distinguish executions that are semantically equivalent according to the

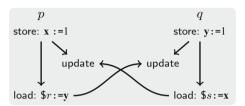

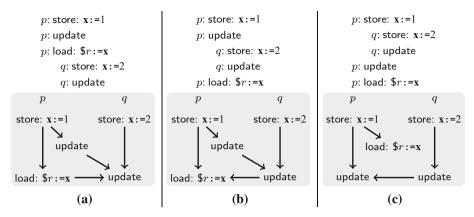

Fig. 6 Three redundant happens-before relations for Fig. 5

Shasha—Snir traces. The reason for this is the mechanism of TSO buffer forwarding: When a thread executes a load to a memory location  $\mathbf{x}$ , it will first check its store buffer. If the buffer contains a store to  $\mathbf{x}$ , then the load returns the value of the newest such store buffer entry instead of loading the value from memory. This causes difficulties for a happens-before relation that orders any update with any load of the same memory location.

For example, consider the program shown in Fig. 5. Any execution of this program will have two updates and one load to  $\mathbf{x}$ . Those accesses can be permuted in six different ways. Figure 6a–c shows three of the corresponding happens-before relations. In each of the three cases, the load reads the value 1, written to  $\mathbf{x}$  by p. In Fig. 6a, b the load is satisfied by buffer forwarding, and in Fig. 6c by a read from memory. These three relations all correspond to the same Shasha–Snir trace, shown in Fig. 7a, and they all have the same observable behavior, since the value of the load is obtained from the same store. Hence, we should find a representation of executions that does not distinguish between these three cases.

We can now describe *chronological traces*, our representation which solves the above problems, by omitting some of the edges, leaving some nodes unrelated. More precisely, edges between loads and updates should be omitted in the following cases.

- 1. A load is never directly related to an update originating in the same thread. This captures the intuition that swapping the order of such a load and update has no effect other than changing a load from memory into a load of the same value from buffer, as seen when comparing Fig. 6b, c.

- 2. A load ld from a memory location  $\mathbf{x}$  by a thread p is never directly related to an update by an another thread q, if the update by q precedes some update to  $\mathbf{x}$  originating in a store by p that precedes ld. This is because the value written by the update of q is effectively hidden to the load ld by the update to  $\mathbf{x}$  by p. When we compare Fig. 6a, b, we see that the order between the update by q and the load is irrelevant, since the update by q is hidden by the update by p (note that the update by p originates in a store that precedes the load).

When we apply these rules to the example of Fig. 5, all of the three representations in Fig. 6a–c merge into a single representation shown in Fig. 7b. In total, we reduce the number of distinguished cases for the program from six to three. This is indeed the minimal number of cases that must be distinguished by any representation, since the different cases result in

Fig. 7 Traces that capture all three Fig. 6a-c. a A Shasha-Snir trace corresponding to all three traces of Fig. 6. b The three traces can be merged into this single trace

different values being loaded by the load instruction or different values in memory at the end of the execution. We show in Theorem 1 of Sect. 3 that our proposed representation is in general optimal.

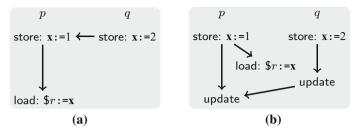

Chronological traces for PSO The TSO and PSO memory models are very similar. The difference is that PSO does not enforce program order between stores by the same thread to different memory locations. To capture this, chronological traces are constructed differently under TSO and PSO. In particular, under TSO there will always be edges between all updates of the same thread, but under PSO we omit those edges when the updates access different memory locations. In Sect. 5 we describe in more detail how to adapt the chronological traces described above to the PSO memory model.

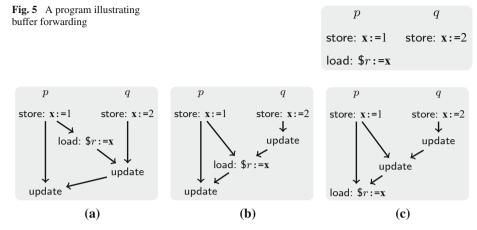

DPOR based on chronological traces Here, we illustrate how stateless model checking performs DPOR based on chronological traces, in order to explore one execution per chronological trace. As example, we use the small program of Fig. 5. This example shows only the intuition of the process, and is intentionally vague. A detailed description of the algorithm is given in Sect. 4.

The algorithm initially explores an arbitrary execution of the program, and simultaneously generates the corresponding chronological trace. In our example, this execution can be the one shown in Fig. 8a, along with its chronological trace. The algorithm then finds those edges of the chronological trace that can be reversed by changing the thread scheduling of the execution. In Fig. 8a, the reversible edges are the ones from p: update to q: update, and from p: load:  $rac{1}{2} = rac{1}{2} = rac{1}{2$

In the example, reversing the edge from p: load: r := x to q: update will generate the execution and chronological trace in Fig. 8b. Notice that the new execution is observably different from the previous one: the load reads the value 2 instead of 1.

The chronological traces in both Fig. 8a, b display a reversible edge from p: update to q: update. The algorithm therefore initiates an execution where q: update is performed before p: update. The algorithm will generate the execution and chronological trace in Fig. 8c.

Notice that the only reversible edge in Fig. 8c is the one from q: update to p: update. However, traces where p: update is executed before q: update, have already been explored in Fig. 8a, b. Since there are no other edges that can be reversed, SMC terminates, having examined precisely the three chronological traces that exist for the program of Fig. 5.

Fig. 8 How SMC with DPOR explores the program of Fig. 5

#### 3 Formalization

In this section we summarize our formalization of the concepts of Sect. 2. We introduce our representation of program executions, define chronological traces, formalize Shasha–Snir traces for TSO, and prove a one-to-one correspondence between chronological traces and Shasha–Snir traces.

Preliminaries For a function f, we use the notation  $f[x \leftarrow v]$  to denote the function f' such that f'(x) = v and f'(y) = f(y) whenever  $y \neq x$ . We use  $w \cdot w'$  to denote the concatenation of the words w and w'.

*Parallel programs* We consider parallel programs consisting of a number of threads that run in parallel, each executing a deterministic code, written in an assembly-like programming language. The language includes instructions store:  $\mathbf{x} := \$r$ , load:  $\$r := \mathbf{x}$ , and fence. Other instructions do not access memory, and their precise syntax and semantics are ignored for brevity. Here, and in the remainder of this text,  $\mathbf{x}$ ,  $\mathbf{y}$ ,  $\mathbf{z}$  are used to name memory locations, u, v, w are used to name values, and \$r, \$s, \$t are used to name processor registers. We use the short forms  $\$t(\mathbf{x})$  and  $\mathtt{Id}(\mathbf{x})$  to denote some store and load of  $\mathbf{x}$  respectively, where the value is not interesting. We use TID to denote the set of all thread identifiers, and MemLoc to denote the set of all memory locations.

Formal TSO semantics We formalize the TSO model by an operational semantics. Define a configuration as a pair  $(\mathbb{L}, \mathbb{M})$ , where  $\mathbb{M}$  maps memory locations to values, and  $\mathbb{L}$  maps each thread p to a local configuration of the form  $\mathbb{L}(p) = (\mathbb{R}, \mathbb{B})$ . Here  $\mathbb{R}$  is the state of local registers (their valuation denoted  $\mathbb{R}(\$r)$ ) and program counter of p, and  $\mathbb{B}$  is the contents of the store buffer of p. This content is a word over pairs  $(\mathbf{x}, v)$  of memory locations and values. We let the notation  $\mathbb{B}(\mathbf{x})$  denote the value v such that  $(\mathbf{x}, v)$  is the rightmost (i.e., most recently inserted) pair in  $\mathbb{B}$  of form  $(\mathbf{x}, \underline{\ })$ . If there is no such pair in  $\mathbb{B}$ , then  $\mathbb{B}(\mathbf{x}) = \bot$ .

In order to accommodate memory updates in our operational semantics we will introduce the notion of *auxiliary threads*. For each thread  $p \in \mathsf{TID}$ , we assume that there is an auxiliary thread  $\mathsf{upd}(p)$ . The auxiliary thread  $\mathsf{upd}(p)$  will nondeterministically perform memory updates from the store buffer of p, when the buffer is non-empty. We use

$\mathsf{AuxTID} = \{\mathsf{upd}(p) | p \in \mathsf{TID}\}\$  to denote the set of auxiliary thread identifiers. We will use p and q to refer to real or auxiliary threads in  $\mathsf{TID} \cup \mathsf{AuxTID}$  as convenient.

For configurations  $c = (\mathbb{L}, \mathbb{M})$  and  $c' = (\mathbb{L}', \mathbb{M}')$ , we write  $c \xrightarrow{p} c'$  to denote that from configuration c, thread p can execute its next instruction, thereby changing the configuration into c'. We define the transition relation  $c \xrightarrow{p} c'$  depending on what the next instruction op of p is in c. In the following we assume  $c = (\mathbb{L}, \mathbb{M})$  and  $c' = (\mathbb{L}', \mathbb{M}')$  and  $\mathbb{L}(p) = (\mathbb{R}, \mathbb{B})$ . Let  $\mathbb{R}_{pc}$  be obtained from  $\mathbb{R}$  by advancing the program counter after p executes its next instruction. Depending on this next instruction op, we have the following cases.

Store If op has the form store:  $\mathbf{x} := \$r$ , then  $c \xrightarrow{p} c'$  iff  $\mathbb{L}' = \mathbb{L}[p \longleftrightarrow (\mathbb{R}_{pc}, \mathbb{B} \cdot (\mathbf{x}, v))]$  where  $v = \mathbb{R}(\$r)$  and  $\mathbb{M}' = \mathbb{M}$  and. Intuitively, under TSO, instead of updating the memory with the new value v, we insert the entry  $(\mathbf{x}, v)$  at the end of the store buffer of the thread.

Load If op has the form load:  $r:=\mathbf{x}$ , then  $c \xrightarrow{p} c'$  iff  $\mathbb{M}' = \mathbb{M}$  and either

- 1. (From memory)  $\mathbb{B}(\mathbf{x}) = \bot$  and  $\mathbb{L}' = \mathbb{L}[p \longleftrightarrow (\mathbb{R}_{pc}[\$r \longleftrightarrow \mathbb{M}(\mathbf{x})], \mathbb{B})], \text{ or }$

- 2. (Buffer forwarding)  $\mathbb{B}(\mathbf{x}) \neq \bot$  and  $\mathbb{L}' = \mathbb{L}[p \leftrightarrow (\mathbb{R}_{pc}[\$r \leftrightarrow \mathbb{B}(\mathbf{x})], \mathbb{B})].$

Intuitively, in the first case there is no entry for  $\mathbf{x}$  in the thread's own store buffer, so the value is read from memory. In the second case, we read the value of  $\mathbf{x}$  from its *latest* entry in the store buffer of the thread.

*Fence* If op has the form fence, then  $c \stackrel{p}{\to} c'$  iff  $\mathbb{B} = \varepsilon$  and  $\mathbb{L}' = \mathbb{L}[p \longleftrightarrow (\mathbb{R}_{pc}, \mathbb{B})]$  and  $\mathbb{M}' = \mathbb{M}$ . A fence can only be executed when the store buffer of the thread is empty.

*Update* In addition to instructions which are executed by the threads, at any point when a store buffer is non-empty, an *update* event may nondeterministically occur. The memory is then updated according to the oldest (leftmost) letter in the store buffer, and that letter is removed from the buffer. To formalize this, we will assume that the auxiliary thread  $\operatorname{upd}(p)$  executes a pseudo-instruction  $\operatorname{u}(\mathbf{x})$ . We say that  $c \xrightarrow{\operatorname{upd}(p)} c'$  iff  $\mathbb{B} = (\mathbf{x}, v) \cdot \mathbb{B}'$  for some  $\mathbf{x}, v$ ,  $\mathbb{B}'$  and  $\mathbb{M}' = \mathbb{M}[\mathbf{x} \hookleftarrow v]$  and  $\mathbb{L}' = \mathbb{L}[p \hookleftarrow (\mathbb{R}, \mathbb{B}')]$ .

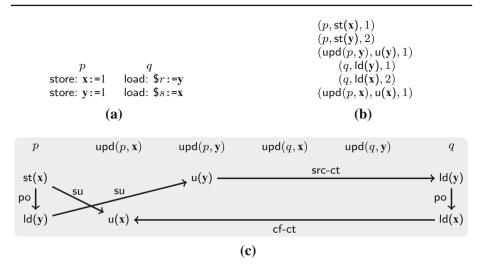

Program executions Based on the operational semantics defined above, a program execution can be defined as a sequence  $c_0 \xrightarrow{p_0} c_1 \xrightarrow{p_1} \cdots \xrightarrow{p_{n-1}} c_n$  of configurations related by transitions labelled by actual or auxiliary thread IDs. Since each transition of each program thread (including the auxiliary threads of form  $\operatorname{upd}(q)$ ) is deterministic, a program run is uniquely determined by its sequence of thread IDs. Formally, we will therefore define each execution as a word of events. Each event is a triple (p, i, j) which represents one transition in the run. Here the thread  $p \in \mathsf{TID} \cup \mathsf{AuxTID}$  is a regular or auxiliary thread, executing an instruction i (which may be an update  $\mathsf{u}(\mathsf{x})$ ). The natural number j is used to disambiguate events. We let j be such that (p, i, j) is the j:th event of p in the execution (counting from 1). For an event e = (p, i, j), we define  $\mathsf{tid}(e) = p$ . We will use Event to denote the set of all possible events. Figure 9 shows three sample executions.

For an execution  $\tau$  and two events e,e' in  $\tau$ , we say that  $e<_{\tau}e'$  iff e strictly precedes e' in  $\tau$ . We define two dummy events  $e^0=(\bot,\bot,0)$  and  $e^\infty=(\bot,\bot,\infty)$ , and we extend  $<_{\tau}$  such that for every event  $e\notin\{e^0,e^\infty\}$  we have  $e^0<_{\tau}e<_{\tau}e^\infty$ .

For an execution  $\tau$  and an event  $e = (p, \operatorname{st}(\mathbf{x}), j)$  in  $\tau$ , we define  $\operatorname{upd}_{\operatorname{st}}(e)$  to be the update event in  $\tau$  corresponding to the store event e. Formally, let k be the number of events  $e_w = (p', \operatorname{st}(\mathbf{y}), j')$  for any memory location  $\mathbf{y}$  in  $\tau$  such that p' = p and  $j' \leq j$ . Then

$$e_s\colon (p,\operatorname{st}(\mathbf{x}),1) \\ (q,\operatorname{st}(\mathbf{z}),1) \\ (p,\operatorname{st}(\mathbf{y}),2) \\ (p,\operatorname{st}(\mathbf{z}),1) \\ (e_l\colon (p,\operatorname{ld}(\mathbf{x}),2) \\ (u\operatorname{pd}(q),\operatorname{u}(\mathbf{z}),1) \\ (u\operatorname{pd}(q),\operatorname{u}(\mathbf{x}),1) \\ (u\operatorname{pd}(q),\operatorname{u}(\mathbf{z}),1) \\ (a) \operatorname{upd}_{\operatorname{st}}(e_s) = \operatorname{upd}_{\operatorname{ld}}(e_l) = e_u \\ \text{Here } e_u \text{ is the update corresponding to the store} \\ e_s. \text{ Since } e_s \text{ is the latest store to } \mathbf{x}, \text{ which} \\ \operatorname{precedes} e_l \text{ in program order, we have that} \\ \operatorname{upd}_{\operatorname{ld}}(e_l) = e_u. \\ (\mathbf{c}) \operatorname{upd}_{\operatorname{st}}(e_s) = e_u \operatorname{upd}_{\operatorname{ld}}(e_l) = e^0 \\ \operatorname{Here} e_s \operatorname{corresponds to} e_u \operatorname{as in Figure 9(a)}. \text{ The load} \\ e_l \text{ is not preceded by any store to the same memory location. Therefore, we define  $\operatorname{upd}_{\operatorname{ld}}(e_l) = e^0.$$$

Fig. 9 Illustration of the definitions of upd<sub>st</sub> and upd<sub>ld</sub>

$\operatorname{upd}_{\operatorname{st}}(e) = (\operatorname{upd}(p), \operatorname{u}(\mathbf{x}), k)$  if there is such an event in  $\tau$ . Otherwise  $\operatorname{upd}_{\operatorname{st}}(e) = e^{\infty}$ , denoting that the update is still pending at the end of  $\tau$ . Figure 9a illustrates the typical case, where the store  $e_s$  is eventually followed by its corresponding update  $\operatorname{upd}_{\operatorname{st}}(e_s) = e_u$ . Figure 9b shows the case when the update corresponding to the store  $e_s$  is still pending at the end of the execution, and therefore  $\operatorname{upd}_{\operatorname{st}}(e_s) = e^{\infty}$ .

For an execution  $\tau$  and an event  $e = (p, \mathsf{Id}(\mathbf{x}), j)$  in  $\tau$ , we define  $\mathsf{upd}_{\mathsf{Id}}(e)$  to be the update event of the latest store to  $\mathbf{x}$ , which precedes e in the same thread. The intuition is that  $\mathsf{upd}_{\mathsf{Id}}(e)$  is the update from which e would get its value in the case of buffer forwarding. Formally, if there is an event  $e_w = (p, \mathsf{st}(\mathbf{x}), k)$  in  $\tau$  such that k < j and there is no event  $(p, \mathsf{st}(\mathbf{x}), l)$  in  $\tau$  with k < l < j, then  $\mathsf{upd}_{\mathsf{Id}}(e) = \mathsf{upd}_{\mathsf{st}}(e_w)$ . Otherwise  $\mathsf{upd}_{\mathsf{Id}}(e) = e^0$ . Figure 9a, b shows the typical case, where  $\mathsf{upd}_{\mathsf{Id}}(e_l)$  is taken to be the update corresponding to the latest preceding store by the same thread to the same memory location. Figure 9c shows the case when there is no such preceding store, and  $\mathsf{upd}_{\mathsf{Id}}(e_l)$  is taken to be the dummy event  $e^0$ . (Notice that the store  $e_s$  is to a different memory location.)

Chronological traces We can now introduce the main conceptual contribution of the paper, viz. chronological traces. For an execution  $\tau$  we define its chronological trace  $\mathcal{T}_C(\tau)$  as a directed graph  $\langle V, E \rangle$ . The vertices V are all the events in  $\tau$ ; both events representing instructions and events representing updates. The set of edges E is the union of six relations:  $E = \rightarrow_{\tau}^{po} \cup \rightarrow_{\tau}^{su} \cup \rightarrow_{\tau}^{uu} \cup \rightarrow_{\tau}^{src-ct} \cup \rightarrow_{\tau}^{cf-ct} \cup \rightarrow_{\tau}^{uf}$ .

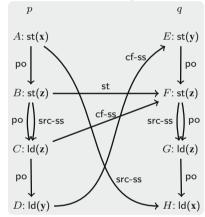

We will illustrate the definition on an execution of the program in Fig. 10a, which contains an idiom that occurs in the mutual exclusion algorithm of Peterson [31]. It is mostly the same as that from Dekker's mutual exclusion algorithm. But it has two additional accesses in each thread to a separate memory location **z**. These provide an opportunity to display buffer forwarding. Figure 10c shows an example of an execution and Fig. 10b shows its corresponding chronological trace.

We define the edge relations of chronological traces as follows, for two arbitrary events  $e = (p, i, j) \in V$  and  $e' = (p', i', j') \in V$ :

```

\begin{array}{cccc} p & q \\ A : & \text{store: } \mathbf{x} := 1 & E : & \text{store: } \mathbf{y} := 1 \\ B : & \text{store: } \mathbf{z} := 1 & F : & \text{store: } \mathbf{z} := 0 \\ C : & \text{load: } \$r := \mathbf{z} & G : & \text{load: } \$r := \mathbf{z} \\ D : & \text{load: } \$s := \mathbf{y} & H : & \text{load: } \$s := \mathbf{x} \end{array}

```

(a) A small program illustrating the idiom of Peterson's mutual exclusion algorithm.

(b) The chronological trace  $\mathcal{T}_C(\tau)$  corresponding to the execution in Figure 10(c). Notice that there is no edge between the load G from  $\mathbf{z}$  and either of the updates to  $\mathbf{z}$ .

(d) The Shasha-Snir trace  $\mathcal{T}(\tau)$  corresponding to the execution in Figure 10(c).

Fig. 10 Traces illustrated by the idiom of Peterson's mutual exclusion algorithm

Program order  $e \to_{\tau}^{po} e'$  iff p = p' and j' = j + 1. For example, we see in Fig. 10b that there is a program order edge from the store instruction A (i.e., the event (p, st(x), 1)) to the store instruction B (i.e., the event (p, st(z), 2)) which immediately follows it in the program of thread p. Similarly, the updates of each thread are program ordered. E.g.,  $A' \to_{\tau}^{po} B'$ .

Store to update  $e \to_{\tau}^{SU} e'$  iff i = St(x) for some x and  $upd_{St}(e) = e'$ . I.e., e' is the update corresponding to the store e. This is illustrated in Fig. 10b where there is an SU-edge from each store, to its corresponding update. E.g.,  $A \to_{\tau}^{SU} A'$ .

Update to update  $e \to_{\tau}^{\mathsf{uu}} e'$  iff  $i = \mathsf{u}(\mathbf{x})$  and  $i' = \mathsf{u}(\mathbf{x})$  for some  $\mathbf{x}$  and  $e <_{\tau} e'$  and there is no event  $e'' = (p'', \mathsf{u}(\mathbf{x}), j'')$  such that  $e <_{\tau} e'' <_{\tau} e'$ . I.e.,  $\to_{\tau}^{\mathsf{uu}}$  chronologically orders all updates for each memory location. In Fig. 10b we see that the two updates B' and F' to  $\mathbf{z}$

are uu-ordered with each other in the same order as they appear in the execution in Fig. 10c. However, they are not uu-ordered with the updates A' and E' to  $\mathbf{x}$  and  $\mathbf{y}$ .

Source  $e \to_{\tau}^{src-ct} e'$  iff for some  $\mathbf{x}$  it holds that  $i = \mathbf{u}(\mathbf{x})$  and  $i' = \mathsf{Id}(\mathbf{x})$  and  $\mathsf{upd}_{\mathsf{Id}}(e') <_{\tau} e <_{\tau} e'$  and there is no update  $e'' = (p'', \mathbf{u}(\mathbf{x}), j'')$  to  $\mathbf{x}$  such that  $e <_{\tau} e'' <_{\tau} e'$ . I.e., if the source of the value read by e' is an update e from a different process, then  $e \to_{\tau}^{src-ct} e'$ . Otherwise, there is no incoming  $\to_{\tau}^{src-ct}$  edge to e'. Since the definition forces the strict order  $\mathsf{upd}_{\mathsf{Id}}(e') <_{\tau} e <_{\tau} e'$ , it excludes the possibility of the update e originating in the same thread as the load e' (as no update from e' can come after  $\mathsf{upd}_{\mathsf{Id}}(e')$  but before e'). Therefore a load is never src-ct-related to an update from the same thread. In Fig. 10b we see that the load e' takes its value from the update e'. Therefore the events are src-ct-related. But the loads e' and e' to e' both read the value written by their own thread, and therefore have no src-ct-relation. The "ct" in the name of the relation stands for "chronological trace", and serves to distinguish the relation e' for chronological traces from the similar, but different relation e' for Shasha–Snir traces (introduced below).

Conflict  $e op_{\tau}^{\text{cf-ct}} e'$  iff  $i = \text{Id}(\mathbf{x})$  and  $i' = \text{U}(\mathbf{x})$  for some  $\mathbf{x}$  and e' is the first (w.r.t.  $<_{\tau}$ ) event  $e_u$  of the form  $(\_, \text{U}(\mathbf{x}), \_)$  such that both  $e <_{\tau} e_u$  and  $\text{Upd}_{\text{Id}}(e) <_{\tau} e_u$ . The intuition here is that  $e \to_{\tau}^{\text{cf-ct}} e'$  when e' is the first update which succeeds e in the coherence order of  $\mathbf{x}$ . Equivalently, e' is the update that overwrites the value that was read by e. In Fig. 10b, the load e0 to e1 by e2 preads the initial value of e3, which is then overwritten by the update e4 by by e5. Therefore we have e6 by buffer forwarding. That value is later overwritten in memory by the update e7. Therefore we have e7 by cf-ct e7.

Update to fence  $e ou_{\tau}^{\mathsf{uf}} e'$  iff  $i = \mathsf{u}(\mathbf{x})$  for some  $\mathbf{x}$ , and  $i' = \mathsf{fence}$  and  $p = \mathsf{upd}(p')$  and  $e <_{\tau} e'$  and there is no event  $e'' = (p, \mathsf{u}(\mathbf{y}), j'')$  for any  $\mathbf{y}$  such that  $e <_{\tau} e'' <_{\tau} e'$ . The intuition here is that the fence cannot be executed until all pending updates of the same thread have been flushed from the buffer. Hence the updates are ordered before the fence.

Shasha–Snir traces We will now formalize Shasha–Snir traces, and prove that chronological traces are equivalent to Shasha–Snir traces, in the sense that they induce the same equivalence relation on executions. We first recall the definition of Shasha–Snir traces. We follow the formalization by Bouajjani et al. [8].

First, we introduce the notion of a *completed* execution. We say that an execution  $\tau$  is completed when all stores have reached memory, i.e., when for every event  $e=(p,\operatorname{st}(\mathbf{x}),j)$  in  $\tau$  we have  $\operatorname{upd}_{\operatorname{st}}(e)\neq e^\infty$ . In the context of Shasha–Snir traces, we will restrict ourselves to completed executions.

For a completed execution  $\tau$ , we define the Shasha–Snir trace of  $\tau$  as the graph  $\mathcal{T}(\tau) = \langle V, E \rangle$  where V is the set of all non-update events (p, i, j) in  $\tau$  where  $i \neq \mathbf{u}(\mathbf{x})$  for all  $\mathbf{x}$ . The edges E is the union of four relations  $E = \rightarrow_{\tau}^{\mathsf{po}} \cup \rightarrow_{\tau}^{\mathsf{st}} \cup \rightarrow_{\tau}^{\mathsf{cf-ss}} \cup \rightarrow_{\tau}^{\mathsf{cf-ss}}$ .

For two arbitrary events  $e=(p,i,j)\in V$  and  $e'=(p',i',j')\in V$ , we define the relations as follows:

Program order  $e \to_{\tau}^{po} e'$  iff p = p' and j' = j + 1. This is the same program order as for chronological traces.

Store order  $e \to_{\tau}^{\mathsf{St}} e'$  iff  $i = \mathsf{St}(\mathbf{x})$  and  $i' = \mathsf{St}(\mathbf{x})$  for some  $\mathbf{x}$  and the corresponding updates are ordered in  $\tau$  s.t.  $\mathsf{upd}_{\mathsf{St}}(e) <_{\tau} \mathsf{upd}_{\mathsf{St}}(e')$  and there is no other update event  $e'' = (p'', \mathsf{u}(\mathbf{x}), j'')$

such that  $\operatorname{upd}_{\operatorname{st}}(e) <_{\tau} e'' <_{\tau} \operatorname{upd}_{\operatorname{st}}(e')$ . I.e., for each memory location  $\mathbf{x}$ , the transitive closure  $\to_{\tau}^{\operatorname{st}^*}$  is a total order on all stores to  $\mathbf{x}$  based on the order in which they reach memory.

Source  $e \to_{\tau}^{\mathsf{src\text{-}ss}} e'$  iff  $i' = \mathsf{Id}(\mathbf{x})$  and e is the maximal store event  $e'' = (p'', \mathsf{st}(\mathbf{x}), j'')$  with respect to  $\to_{\tau}^{\mathsf{st}^*}$  such that either  $\mathsf{upd}_{\mathsf{st}}(e'') <_{\tau} e'$  or  $e'' \to_{\tau}^{\mathsf{po}^*} e'$ . I.e.,  $e \to_{\tau}^{\mathsf{src\text{-}ss}} e'$  when e' is a load which reads its value from e, via memory or by buffer forwarding.

Conflict  $e \to_{\tau}^{cf-ss} e'$  iff i = Id(x) and i' = st(x) and if there is an event e'' such that  $e'' \to_{\tau}^{src-ss} e$  then  $e'' \to_{\tau}^{st} e'$ , otherwise e' has no predecessor in  $\to_{\tau}^{st}$ . I.e., e' is the store which overwrites the value that was read by e.

The definition of Shasha–Snir traces is illustrated in Fig. 10d. We are now ready to state the equivalence theorem.

**Theorem 1** (Equivalence of Shasha–Snir traces and chronological traces) For a given program  $\mathcal{P}$  with two completed executions  $\tau$ ,  $\tau'$ , it holds that  $\mathcal{T}(\tau) = \mathcal{T}(\tau')$  iff  $\mathcal{T}_C(\tau) = \mathcal{T}_C(\tau')$ .

We decompose the theorem into the following two lemmas, which are proven separately.

**Lemma 1** (Equivalence of Shasha–Snir traces and chronological traces  $\Rightarrow$  direction) For a given program  $\mathcal{P}$  with two completed executions  $\tau$ ,  $\tau'$ , it holds that if  $\mathcal{T}(\tau) = \mathcal{T}(\tau')$  then  $\mathcal{T}_C(\tau) = \mathcal{T}_C(\tau')$ .

**Lemma 2** (Equivalence of Shasha–Snir traces and chronological traces  $\Leftarrow$  direction) For a given program  $\mathcal{P}$  with two completed executions  $\tau$ ,  $\tau'$ , it holds that if  $\mathcal{T}_C(\tau) = \mathcal{T}_C(\tau')$  then  $\mathcal{T}(\tau) = \mathcal{T}(\tau')$ .

*Proof of Lemma 1* Let two completed executions  $\tau$  and  $\tau'$  be given. Let

$$\mathcal{T}(\tau) = \langle V_{SS}, \rightarrow_{\tau}^{\mathsf{po}} \cup \rightarrow_{\tau}^{\mathsf{st}} \cup \rightarrow_{\tau}^{\mathsf{src\text{-ss}}} \cup \rightarrow_{\tau}^{\mathsf{cf\text{-ss}}} \rangle \text{ and}$$

$$\mathcal{T}(\tau') = \langle V_{SS}', \rightarrow_{\tau'}^{\mathsf{po}} \cup \rightarrow_{\tau'}^{\mathsf{st}} \cup \rightarrow_{\tau'}^{\mathsf{src\text{-ss}}} \cup \rightarrow_{\tau'}^{\mathsf{cf\text{-ss}}} \rangle \text{ and } \mathcal{T}_{C}(\tau)$$

$$= \langle V_{C}, \rightarrow_{\tau}^{\mathsf{po}} \cup \rightarrow_{\tau}^{\mathsf{su}} \cup \rightarrow_{\tau}^{\mathsf{uu}} \cup \rightarrow_{\tau}^{\mathsf{src\text{-ct}}} \cup \rightarrow_{\tau}^{\mathsf{cf\text{-ct}}} \cup \rightarrow_{\tau}^{\mathsf{uf}} \rangle \text{ and}$$

$$\mathcal{T}_{C}(\tau') = \langle V_{C}', \rightarrow_{\tau'}^{\mathsf{po}} \cup \rightarrow_{\tau'}^{\mathsf{su}} \cup \rightarrow_{\tau'}^{\mathsf{uu}} \cup \rightarrow_{\tau'}^{\mathsf{src\text{-ct}}} \cup \rightarrow_{\tau'}^{\mathsf{cf\text{-ct}}} \cup \rightarrow_{\tau'}^{\mathsf{uf}} \rangle.$$

Furthermore, assume that  $T(\tau) = T(\tau')$ .

First, we determine that the events are the same in both chronological traces:  $V_C = V_C'$ . From  $V_{SS} = V_{SS}'$  we have that the non-update events in  $\tau$  are the same as the ones in  $\tau'$ . Since  $\tau$  and  $\tau'$  contain the same stores for each thread in the same per-thread order, it follows from the completedness of  $\tau$  and  $\tau'$ , and from the TSO semantics that  $\tau$  and  $\tau'$  also have the same update events. Hence  $V_C = V_C'$ .

We see that the definitions of program order and store to update order in chronological traces are entirely determined by which events exist in the execution for each thread. Since both executions have the same events, we conclude that  $\rightarrow_{\tau}^{po} = \rightarrow_{\tau'}^{po}$  and  $\rightarrow_{\tau}^{su} = \rightarrow_{\tau'}^{su}$ . The equality  $\rightarrow_{\tau}^{uf} = \rightarrow_{\tau'}^{uf}$  of update to fence order follows similarly.

Let us consider the definitions of update to update order for chronological traces and store order for Shasha–Snir traces. We see that there is a one-to-one mapping between relations  $e \to_{\tau}^{\mathsf{st}} e'$  for stores in Shasha–Snir traces to relations  $\mathsf{upd}_{\mathsf{st}}(e) \to_{\tau}^{\mathsf{uu}} \mathsf{upd}_{\mathsf{st}}(e')$  in chronological traces. Since the store orders are the same for  $\tau$  and  $\tau'$ , we thus conclude that the update to update orders are also the same:  $\to_{\tau}^{\mathsf{uu}} = \to_{\tau'}^{\mathsf{uu}}$ .

We now turn our attention to proving that  $\rightarrow_{\tau}^{\text{src-ct}} = \rightarrow_{\tau'}^{\text{src-ct}}$ . We will first prove that  $\rightarrow_{\tau}^{\text{src-ct}} \subseteq \rightarrow_{\tau'}^{\text{src-ct}}$ . From symmetry it then follows that  $\rightarrow_{\tau'}^{\text{src-ct}} \subseteq \rightarrow_{\tau}^{\text{src-ct}}$ , and hence that  $\rightarrow_{\tau}^{\text{src-ct}} = \rightarrow_{\tau}^{\text{src-ct}}$ . Let us assume that the relation  $e \rightarrow_{\tau}^{\text{src-ct}} e'$  exists in  $\rightarrow_{\tau}^{\text{src-ct}}$  for some events  $e = (p, \mathbf{u}(\mathbf{x}), j)$  and  $e' = (p', \mathbf{ld}(\mathbf{x}), j')$ . We will prove that the same relation  $e \to_{\tau'}^{\text{src-ct}} e'$  exists in  $\to_{\tau'}^{\text{src-ct}}$ . From the definition of  $\to_{\tau}^{\text{src-ct}}$  we have that  $upd_{ld}(e') <_{\tau} e' <_{\tau} e'$  and there is no update  $e'' = p'', u(\mathbf{x}), i''$ ) to the same memory location such that  $e <_{\tau} e'' <_{\tau} e'$ . Since e' is preceded in  $\tau$  by at least one update to x, there must be a store event  $e_w$  such that  $e_w \to_{\tau}^{\text{src-ss}} e'$  in  $\tau$ . From the definition of  $\to_{\tau}^{\text{src-ss}}$ we have that  $e_w$  is the maximal event (p'', st(x), j'') with respect to  $\rightarrow_{\tau}^{st*}$  such that either  $\operatorname{upd}_{\operatorname{st}}(e_w) <_{\tau} e' \text{ or } e_w \to_{\tau}^{\operatorname{po*}} e'. \text{ If } e_w \to_{\tau}^{\operatorname{po*}} e', \text{ then } \operatorname{upd}_{\operatorname{st}}(e_w) = \operatorname{upd}_{\operatorname{ld}}(e'). \text{ But then the}$ maximality of  $e_w$  contradicts  $upd_{ld}(e') <_{\tau} e <_{\tau} e'$ . Hence we have  $upd_{st}(e_w) <_{\tau} e'$ . Maximality of  $e_w$  now gives that  $\operatorname{upd}_{\operatorname{st}}(e_w) = e$ . Since  $\to_{\tau}^{\operatorname{src-ss}} = \to_{\tau'}^{\operatorname{src-ss}}$  we have that in  $\tau'$  also  $e_w \to_{\tau'}^{\text{src-ss}} e'$ . From the definition of  $\to_{\tau'}^{\text{src-ss}}$  and  $\neg (e_w \to_{\tau'}^{\text{po}*} e')$  we know that  $\mathsf{upd}_{\mathsf{st}}(e_w)$ is the store-order-maximal update to x that precedes e' in  $\tau'$ . Since the store order is the same for  $\tau$  and  $\tau'$  we have  $upd_{ld}(e') <_{\tau'} e$ . But then  $e = upd_{st}(e_w)$  satisfies the criteria for  $e \rightarrow_{\tau'}^{\text{src-ct}} e'$ .

Finally, we will show that  $\rightarrow_{\tau}^{\text{cf-ct}} = \rightarrow_{\tau'}^{\text{cf-ct}}$ . Similarly to the proof for  $\rightarrow_{\tau}^{\text{src-ct}} = \rightarrow_{\tau'}^{\text{src-ct}}$ , it suffices here to show that  $\rightarrow_{\tau}^{\text{cf-ct}} \subseteq \rightarrow_{\tau'}^{\text{cf-ct}}$ . Assume therefore that  $e_r \rightarrow_{\tau}^{\text{cf-ct}} e_u$  for some events  $e_r = (p, \mathsf{ld}(\mathbf{x}), j), e_u = (p', \mathsf{u}(\mathbf{x}), j')$ . We will show that  $e_r \rightarrow_{\tau'}^{\text{cf-ct}} e_u$ . The definition of  $\rightarrow_{\tau}^{\text{cf-ct}}$  gives that  $e_u$  is the first (w.r.t.  $<_{\tau}$ ) event e of the form (\_, u(x),\_) such that both  $e_r <_{\tau} e$  and upd $_{\mathsf{ld}}(e_r) <_{\tau} e$ . Let  $e_w$  be the store event such that upd $_{\mathsf{st}}(e_w) = e_u$ . We will split the proof in cases depending on whether or not there exists a source event for  $e_r$  in the Shasha–Snir traces.

Assume therefore first (i) that there is no event  $e_{src}$  such that  $e_{src} \to_{\tau}^{src-ss} e_r$ . Then there is no update to  $\mathbf{x}$  that precedes  $e_r$  in  $<_{\tau}$ . Furthermore  $\mathsf{upd}_{\mathsf{ld}}(e_r) = e^0$ . This tells us that  $e_w$  has no predecessor in  $\to_{\tau}^{st}$ . Since  $\to_{\tau}^{st} = \to_{\tau}^{st}$ , we also have that  $e_w$  has no predecessor in  $\to_{\tau'}^{st}$ . Furthermore, since  $e_r$  has no source event in  $\tau'$ , it must be the case that  $e_r <_{\tau'} e_u$ . But then,  $e_u$  is the first update event in  $\tau'$  which is after both  $e_r$  and  $\mathsf{upd}_{\mathsf{ld}}(e_r)$ . And so we have  $e_r \to_{\tau'}^{\mathsf{cf-ct}} e_u$ .

Next assume (ii) that there is an event  $e_{src}$  with  $e_{src} \to_{\tau}^{\mathsf{src-ss}} e_r$  and that  $\mathsf{tid}(e_{src}) = \mathsf{tid}(e_r)$ . Then it must be the case that  $\mathsf{upd}_{\mathsf{st}}(e_{src}) = \mathsf{upd}_{\mathsf{ld}}(e_r)$ . Since  $\to_{\tau}^{\mathsf{src-ss}} = \to_{\tau'}^{\mathsf{src-ss}}$ , we have that  $e_{src} \to_{\tau'}^{\mathsf{src-ss}} e_r$ . There can be no update event e to the same memory location  $\mathbf{x}$  such that  $\mathsf{upd}_{\mathsf{ld}}(e_r) <_{\tau} e <_{\tau} e_r$ . If there were such an e, then  $e_{src}$  wouldn't be the source of  $e_r$ . The same argument goes in  $\tau'$ . This tells us that  $e_u$  is the immediate store order successor of  $\mathsf{upd}_{\mathsf{ld}}(e_r)$ , i.e.,  $\mathsf{upd}_{\mathsf{ld}}(e_r) \to_{\tau}^{\mathsf{uu}} e_u$  and  $e_{src} \to_{\tau}^{\mathsf{st}} e_w$ . Since  $\to_{\tau}^{\mathsf{uu}} = \to_{\tau'}^{\mathsf{uu}}$ , we have  $\mathsf{upd}_{\mathsf{ld}}(e_r) \to_{\tau'}^{\mathsf{uu}} e_u$ . Hence  $e_u$  is the first update event which succeeds both  $e_r$  and  $\mathsf{upd}_{\mathsf{ld}}(e_r)$  in  $<_{\tau'}$ . Thus  $e_r \to_{\tau'}^{\mathsf{cf-ct}} e_u$ .

Lastly, we assume (iii) that there is an event  $e_{src}$  such that  $e_{src} \to_{\tau}^{\text{Src-ss}} e_r$  and that  $\operatorname{tid}(e_{src}) \neq \operatorname{tid}(e_r)$ . Then it is the case in  $\tau$  that  $\operatorname{upd}_{\operatorname{ld}}(e_r) <_{\tau} \operatorname{upd}_{\operatorname{st}}(e_{src}) <_{\tau} e_r$ . And there is no update event e to  $\mathbf{x}$  such that  $\operatorname{upd}_{\operatorname{st}}(e_{src}) <_{\tau} e <_{\tau} e_r$ . The same holds in  $\tau'$ . Since  $e_u$  is the first update to  $\mathbf{x}$  after  $e_r$  in  $\tau$ , this means that we have  $\operatorname{upd}_{\operatorname{st}}(e_{src}) \to_{\tau}^{\operatorname{uu}} e_u$ . We have  $\to_{\tau}^{\operatorname{uu}} = \to_{\tau'}^{\operatorname{uu}}$ , so  $\operatorname{upd}_{\operatorname{st}}(e_{src}) \to_{\tau'}^{\operatorname{uu}} e_u$ . Now it must be the case that  $e_r <_{\tau'} e_u$ . Otherwise,  $e_{src}$  wouldn't be the source of  $e_r$  in  $\tau'$ , and we know  $e_{src} \to_{\tau'}^{\operatorname{src-ss}} e_r$ . Hence  $e_u$  is an update event that succeeds both  $e_r$  and  $\operatorname{upd}_{\operatorname{ld}}(e_r)$  in  $<_{\tau'}$ . It remains to show that it is the first such update. Suppose  $e \neq e_u$  is an update event to  $\mathbf{x}$  such that  $e_r <_{\tau} e <_{\tau} e_u$ . Then it would be the case that  $\operatorname{upd}_{\operatorname{st}}(e_{src}) <_{\tau'} e <_{\tau'} e_u$ . But this would contradict  $\operatorname{upd}_{\operatorname{st}}(e_{src}) \to_{\tau'}^{\operatorname{uu}} e_u$ . Thus we have  $e_r \to_{\tau'}^{\operatorname{cf-ct}} e_u$ .

This concludes the proof of  $\mathcal{T}_C(\tau) = \mathcal{T}_C(\tau')$ .

*Proof of Lemma* 2 Let two completed executions  $\tau$  and  $\tau'$  be given. Let

$$\mathcal{T}(\tau) = \langle V_{SS}, \rightarrow_{\tau}^{\mathsf{po}} \cup \rightarrow_{\tau}^{\mathsf{st}} \cup \rightarrow_{\tau}^{\mathsf{src-ss}} \cup \rightarrow_{\tau}^{\mathsf{cf-ss}} \rangle \text{ and}$$

$$\mathcal{T}(\tau') = \langle V_{SS}', \rightarrow_{\tau'}^{\mathsf{po}} \cup \rightarrow_{\tau'}^{\mathsf{st}} \cup \rightarrow_{\tau'}^{\mathsf{src-ss}} \cup \rightarrow_{\tau'}^{\mathsf{cf-ss}} \rangle \text{ and}$$

$$\mathcal{T}_{C}(\tau) = \langle V_{C}, \rightarrow_{\tau}^{\mathsf{po}} \cup \rightarrow_{\tau}^{\mathsf{su}} \cup \rightarrow_{\tau}^{\mathsf{uu}} \cup \rightarrow_{\tau}^{\mathsf{src-ct}} \cup \rightarrow_{\tau}^{\mathsf{cf-ct}} \cup \rightarrow_{\tau}^{\mathsf{uf}} \rangle \text{ and}$$

$$\mathcal{T}_{C}(\tau') = \langle V_{C}', \rightarrow_{\tau'}^{\mathsf{po}} \cup \rightarrow_{\tau'}^{\mathsf{su}} \cup \rightarrow_{\tau'}^{\mathsf{uu}} \cup \rightarrow_{\tau'}^{\mathsf{src-ct}} \cup \rightarrow_{\tau'}^{\mathsf{cf-ct}} \cup \rightarrow_{\tau'}^{\mathsf{uf}} \rangle.$$

Furthermore, assume that  $T_C(\tau) = T_C(\tau')$ .

We will prove that  $T(\tau) = T(\tau')$ . We know that  $V_{SS}$  (respectively  $V'_{SS}$ ) is precisely the non-updates of  $V_C$  (respectively  $V_C'$ ). Since  $V_C = V_C'$  we have  $V_{SS} = V_{SS}'$

For the relations  $\rightarrow_{\tau}^{\text{po}}$  and  $\rightarrow_{\tau}^{\text{st}}$ , a reasoning analogue to that in the  $\Rightarrow$  direction gives that  $\rightarrow_{\tau}^{\text{po}} = \rightarrow_{\tau'}^{\text{po}}$  and  $\rightarrow_{\tau}^{\text{st}} = \rightarrow_{\tau'}^{\text{st}}$ .

We will show that  $\rightarrow_{\tau}^{\text{src-ss}} \subseteq \rightarrow_{\tau'}^{\text{src-ss}}$ . Symmetry then gives  $\rightarrow_{\tau'}^{\text{src-ss}} \subseteq \rightarrow_{\tau'}^{\text{src-ss}}$ , and hence  $\rightarrow_{\tau}^{\text{src-ss}} = \rightarrow_{\tau'}^{\text{src-ss}}$ . Assume therefore that  $e_w \rightarrow_{\tau}^{\text{src-ss}} e_r$  holds for some events  $e_w = -\frac{\text{src-ss}}{\text{src-ss}} = \frac{\text{src-ss}}{\text{src-ss}} = \frac{\text{src-ss}}{\text{s$  $(p, \operatorname{st}(\mathbf{x}), j)$  and  $e_r = (p', \operatorname{ld}(\mathbf{x}), j')$ . Then by the definition of  $\rightarrow_{\tau}^{\operatorname{src-ss}}$  we have that  $e_w$  is the maximal event e = (p'', st(x), j'') with respect to  $\rightarrow_{\tau}^{st*}$  such that either  $upd_{st}(e) <_{\tau} e_r$  or  $e \rightarrow_{\tau}^{\mathsf{po}*} e_r$ . We will separate the proof by cases: either  $\mathsf{tid}(e_w) = \mathsf{tid}(e_r)$  or  $\mathsf{tid}(e_w) \neq \mathsf{tid}(e_r)$ .

Assume first (i) that  $tid(e_w) = tid(e_r)$ . Then it holds that  $e_w \rightarrow_{\tau}^{po*} e_r$ , since the events must be program ordered, and the other direction implies  $e_r <_{\tau} \mathsf{upd}_{\mathsf{st}}(e_w)$ . Program order is the same in  $\tau'$  as in  $\tau$ , so we also have  $e_w \rightarrow_{\tau'}^{po*} e_r$ . It remains to show that  $e_w$  is maximal in  $\tau'$ . First we conclude that there can be no store event e such that  $e_w \to_{\tau'}^{st} e$  and  $e \to_{\tau'}^{po*} e_r$ . This is because both the program order and the store order are the same in  $\tau'$  as in  $\tau$ , and hence such an event e would contradict the assumed maximality of  $e_w$  w.r.t.  $\tau$ . As a corollary we have  $upd_{ld}(e_r) = upd_{st}(e_w)$ . Next we need to conclude that there is no event e such that  $e_w \to_{\tau'}^{st} e$  and  $upd_{st}(e) <_{\tau'} e_r$ . We know that there is no such event in  $\tau$ : i.e., there is no event e such that  $e_w \to_{\tau}^{st} e$  and  $upd_{st}(e) <_{\tau} e_r$ . Hence by the definition of  $\to_{\tau}^{src-ct}$  there is no event  $e_{src}^C$  which is source related with  $e_r$  in the chronological trace:  $e_{src}^C \to_{\tau}^{\text{src-ct}} e_r$ . Since  $\rightarrow_{\tau}^{\text{src-ct}} = \xrightarrow{\text{src-ct}}^{\text{src-ct}}$ , the same holds in  $\tau'$ . Now if there were an event such as e in  $\tau'$ , then  $e_r$ would have a source according to  $\rightarrow_{\tau'}^{\text{src-ct}}$ . This is a contradiction, and so there can be no such e in  $\tau'$ . Hence,  $e_w$  is the maximal store event w.r.t.  $\rightarrow_{\tau'}^{st^*}$  which is either updated  $<_{\tau'}$ -before  $e_r$  or program order-before  $e_r$ . That concludes the proof for the case that  $tid(e_w) = tid(e_r)$ .

Next assume (ii) that  $tid(e_w) \neq tid(e_r)$ . Clearly  $e_w$  is not program ordered with  $e_r$ . Hence the definition of  $\rightarrow_{\tau}^{\text{Src-ss}}$  gives that  $\mathsf{upd}_{\mathsf{st}}(e_w) <_{\tau} e_r$ . The maximality of  $e_w$  gives that  $\operatorname{upd}_{\operatorname{Id}}(e_r) <_{\tau} \operatorname{upd}_{\operatorname{st}}(e_w)$ , and that there is no update event  $e = (p'', \operatorname{u}(\mathbf{x}), j'')$  such that  $\begin{array}{l} \mathsf{upd}_{\mathsf{st}}(e_w) <_\tau e <_\tau e_r. \text{ Then by the definition of} \to_\tau^{\mathsf{src-ct}} \text{ we have } \mathsf{upd}_{\mathsf{st}}(e_w) \to_\tau^{\mathsf{src-ct}} e_r. \text{ By} \\ \to_\tau^{\mathsf{src-ct}} = \to_{\tau'}^{\mathsf{src-ct}} \text{ we also have } \mathsf{upd}_{\mathsf{st}}(e_w) \to_{\tau'}^{\mathsf{src-ct}} e_r. \text{ By the definition of} \to_{\tau'}^{\mathsf{src-ct}} \text{ we now} \end{array}$ have that  $e_w$  is the greatest (w.r.t.  $<_{\tau'}$ ) store event with  $\mathsf{upd}_{\mathsf{st}}(e_w) <_{\tau'} e_r$ . We also have that  $\operatorname{upd}_{\operatorname{Id}}(e_r) <_{\tau'} \operatorname{upd}_{\operatorname{st}}(e_w)$ . Since there can be no event  $e = (\_, \operatorname{st}(\mathbf{x}), \_)$  such that  $e \to_{\tau'}^{\operatorname{po}*} e_r$ and  $\operatorname{upd}_{\operatorname{Id}}(e_r) <_{\tau'} \operatorname{upd}_{\operatorname{st}}(e)$ , we have that  $e_w$  is the maximal event  $e = (\_, \operatorname{st}(\mathbf{x}), \_)$  with respect to  $\to_{\tau}^{\operatorname{st}*}$  such that either  $\operatorname{upd}_{\operatorname{st}}(e) <_{\tau'} e_r$  or  $e \to_{\tau'}^{\operatorname{po}*} e_r$ . Hence  $e_w \to_{\tau'}^{\operatorname{src-ss}} e_r$ . This concludes the proof for  $\to_{\tau}^{\operatorname{src-ss}} = \to_{\tau'}^{\operatorname{src-ss}}$ .

Since  $\rightarrow_{\tau}^{\text{cf-ss}}$  (respectively  $\rightarrow_{\tau'}^{\text{cf-ss}}$ ) is entirely determined by  $\rightarrow_{\tau}^{\text{src-ss}}$  and  $\rightarrow_{\tau}^{\text{st}}$  (respectively  $\rightarrow_{\tau'}^{\text{src-ss}}$  and  $\rightarrow_{\tau}^{\text{st}}$ ), and we know that  $\rightarrow_{\tau}^{\text{src-ss}} = \rightarrow_{\tau'}^{\text{src-ss}}$  and  $\rightarrow_{\tau}^{\text{st}} = \rightarrow_{\tau'}^{\text{st}}$ , we immediately get that  $\rightarrow_{\tau}^{\text{Cf-ss}} = \rightarrow_{\tau'}^{\text{Cf-ss}}$ . This concludes the proof.

*Proof of Theorem 1* The theorem follows directly from Lemmas 1 and 2.

# 4 DPOR algorithm for TSO

A DPOR algorithm can exploit chronological traces to perform stateless model checking of programs that execute under TSO (and PSO), as illustrated at the end of Sect. 2. The explored executions follow the semantics of TSO in Sect. 3. For each execution, its happens-before relation is computed, which is the transitive closure of the edge relation  $\rightarrow_{\tau}^{ct} = \rightarrow_{\tau}^{po} \cup \rightarrow_{\tau}^{su} \cup \rightarrow_{\tau}^{rc} \cup \rightarrow_{\tau}^{cf-ct} \cup \rightarrow_{\tau}^{cf-ct} \cup \rightarrow_{\tau}^{cf}$  of the corresponding chronological trace. This happens-before relation can in principle be exploited by any DPOR algorithm to explore at least one execution per equivalence class induced by Shasha–Snir traces. In this section, we will show concretely how to compute the happens-before relation, and how to use it to instantiate a DPOR algorithm. To do so, we will first need to introduce some further concepts.

The happens-before relation  $\rightarrow_{\tau}^{ct}$  is computed on the fly, using vector clocks, while taking the particular structure of chronological traces into account. The main difference from computing happens-before relations for sequentially consistent executions (see, e.g., [32]) is that load events which get their value by store forwarding are not immediately synchronized with the vector clock of the memory location. Instead, the load is associated with the store buffer entry from which it got its value. The load is then synchronized with the memory location at the time when the store buffer entry is updated to memory.

Formally, we extend the TSO configurations described in Sect. 3 to keep track of the necessary information about relations between different events. Below we need vector clocks. A *vector clock* is a function  $C: (\mathsf{TID} \cup \mathsf{AuxTID}) \mapsto \mathbb{N}$ . The intuition is that C captures a set of observed events. For every thread p, the first C(p) events by p have been observed. We let  $\mathsf{VecClocks} = ((\mathsf{TID} \cup \mathsf{AuxTID}) \mapsto \mathbb{N})$  denote the set of vector clocks.

For two vector clocks v, v' we use the notation  $v \sqcup v'$  to denote the vector clock v'' such that v''(p) = max(v(p), v'(p)) for all p. For two vector clocks v, v' we say that  $v \leq v'$  when  $v(p) \leq v'(p)$  for all p. We say that v < v' if at least one of the inequalities is strict. For an event e and a set E of events we define  $E \oplus e = \{e' \in E | \text{tid}(e') \neq \text{tid}(e)\} \cup \{e\}$ , i.e.  $E \oplus e$  is E where e replaces the previous event  $e' \in E$  s.t. tid(e') = tid(e). We use the shorthand  $f[x_0, x_1, \cdots, x_n \hookleftarrow v]$  to denote  $f[x_0 \hookleftarrow v][x_1 \hookleftarrow v] \cdots [x_n \hookleftarrow v]$ , i.e., an assignment of the same value to multiple function arguments.

An *extended configuration* is a quintuple  $(\mathbb{L}, \mathbb{M}, \mathcal{C}, \mathcal{B}, \mathcal{M})$ , where  $(\mathbb{L}, \mathbb{M})$  is a TSO configuration as described in Sect. 3.

## $C: (\mathsf{TID} \cup \mathsf{AuxTID} \cup \mathsf{Event} \cup \{\bot\}) \mapsto \mathsf{VecClocks}$

maps each (real or auxiliary) thread identifier p to a vector clock representing which parts of the execution have been seen by p. Also,  $\mathcal C$  maps each event e to the value of  $\mathcal C(\mathsf{tid}(e))$  at the time immediately after executing e. We fix that  $\mathcal C(\bot) = (\lambda x.0)$  is a zeroed clock.

$\mathcal{B}: \mathsf{TID} \mapsto (\mathsf{MemLoc} \times \mathsf{Event} \times (\mathsf{Event} \cup \{\bot\}))^*$

maps each real (not auxiliary) thread ID p to a word of letters  $(\mathbf{x}, e_s, e_l)$ , each of which keeps an auxiliary state for the corresponding letter in the store buffer in  $\mathbb{L}(p)$ . Here  $\mathbf{x}$  is the accessed memory location,  $e_s$  is the store event that produced that letter, and  $e_l$  is the latest buffer forwarded load event for which the letter has been the source (if there is no such event then  $e_l = \bot$ ).

$\mathcal{M}: \text{MemLoc} \mapsto ((\text{Event} \cup \{\bot\}) \times 2^{\text{Event}})$

maps each memory location  $\mathbf{x}$  to a pair  $(e_u, E_l)$ , where  $e_u$  is the latest update event that accessed  $\mathbf{x}$  (or  $\perp$  if  $\mathbf{x}$  has never been updated), and where  $E_l$  is a set which for each thread p that has read  $\mathbf{x}$  contains the latest event of p that read the value of  $\mathbf{x}$ .

Initially all clocks in C are zeroed, all buffers in B are empty, and for all memory locations  $\mathbf{x}$  we have  $\mathcal{M}(\mathbf{x}) = (\bot, \emptyset)$ .

The idea here is that as we execute memory accesses, we update the vector clock of the executing thread to reflect which new events have been observed.

For example, when we execute an update  $e_x$  corresponding to a buffer entry  $(\mathbf{x}, e_s, e_l)$ , we look to the memory  $\mathcal{M}(\mathbf{x}) = (e_u, E_l)$ . We know that the update event is ordered after the previous update  $e_u$ , as well as the previous loads in  $E_l$  and the store event  $e_s$  which enabled the update  $e_x$ . We update the vector clock  $\mathcal{C}(\mathsf{tid}(e_x))$  of the auxiliary thread to include all these newly observed events.

The procedure for a load from memory is similar, except that we do not observe previous loads. More interesting are loads that are satisfied by buffer forwarding. When we execute a buffer forwarded load  $e_l$  to  $\mathbf{x}$ , we do not observe *any* new event, since the load was not able to reach and synchronize with the memory. Instead we save the load event with the buffer entry from which it read its value. When that entry is updated to memory, by the update event  $\mathsf{upd}_{\mathsf{ld}}(e_l)$ , we move  $e_l$  to the set of loads that have been observed by  $\mathcal{M}(\mathbf{x})$ . By this scheme the load event  $e_l$  becomes available for observation by precisely the update events which succeed  $\mathsf{upd}_{\mathsf{ld}}(e_l)$ . In the remainder of this section we will make this intuition formal.

## 4.1 Instantiating Source-DPOR for chronological traces

We are now ready to show an instantiation of the *Source-DPOR* algorithm of [1] using chronological traces. In Fig. 11, we give the main DPOR algorithm **TSO-Source-DPOR**, explained in this section. The algorithm makes a call to the auxiliary algorithm **TSO-post** in order to compute the next configuration according to the TSO semantics, compute the corresponding chronological trace, and identify events which race with each other. The algorithm **TSO-post** is given in Fig. 12, and explained in Sect. 4.2.

The DPOR algorithm takes three parameters: the current execution  $\tau$ , the current extended state (L, M,  $\mathcal{C}$ ,  $\mathcal{B}$ ,  $\mathcal{M}$ ) and a sleep set *Sleep* of threads which are currently blocked from being executed. The algorithm recursively explores executions which are continuations of  $\tau$ . On line 1 we pick a thread p that can be executed in the current state, and which is not in the sleep set. The next instruction of p will be the first continuation of  $\tau$  which is explored. As races are discovered between events during the exploration, new alternative continuations will be added to the set backtrack. Such alternatives will be explored in subsequent iterations through the loop on lines 3–30.

For each event e that is added to  $\tau$  in one iteration of the loop, three main steps are performed: On line 7, the configuration is updated to reflect the effect of executing e, as well as the new edges in the happens-before relation  $\rightarrow_{\tau}^{ct}$ . At the same time, we compute the set cnf of earlier events which race with e. On lines 8–16, we add new branches to backtrack, corresponding to the races that have been detected and collected in the set cnf. On lines 17–27 we update the sleep set in order to unblock those threads whose next instruction races with e.

The first step is handled by the auxiliary algorithm in Fig. 12. It is explained in Sect. 4.2 below.

In the next step, on lines 8–16, we add new branches to the set backtrack, corresponding to each of the races that have been collected in cnf. For each event  $e_c$  which is in a race with e, we want to add an alternative branch, where  $e_c$  is delayed, allowing the possibility for e to execute before  $e_c$ . Therefore, at line 9, we identify the position in  $\tau$  where  $e_c$  was executed, and the sub-executions  $\tau_0$  and  $\tau_1$  preceding and succeeding  $e_c$ . We then identify the set I of events in  $\tau_1$  which may be the first executed event after  $\tau_0$  in a hypothetical other execution where e executes before  $e_c$ . We make certain at lines 12–15 that at least one of the events in I is represented as an alternative branch to explore after  $\tau_0$ .

$\mathbf{global} \ \mathsf{backtrack} \ = \lambda \tau. \varnothing : \mathsf{Event}^* \mapsto 2^{\mathsf{TID} \cup \mathsf{AuxTID}}$

```

TSO-Source-DPOR(\tau,(\mathbb{L}, \mathbb{M}, \mathcal{C}, \mathcal{B}, \mathcal{M}),Sleep)

1: if(\exists p \in (\mathsf{TID} \cup \mathsf{AuxTID}) \setminus \mathit{Sleep}. \ p \ \mathsf{is} \ \mathsf{enabled})

2:

backtrack(\tau) := \{p\};

3:

while (\exists p \in backtrack(\tau) \setminus Sleep) {

4.

op := the next instruction of p in (\mathbb{L}, \mathbb{M});

5:

i := 1 + the number of events by p in \tau;

e := (p, op, i); // The new event

6.

7:

((\mathbb{L}', \mathbb{M}', \mathcal{C}', \mathcal{B}', \mathcal{M}'), cnf) := TSO-post((\mathbb{L}, \mathbb{M}, \mathcal{C}, \mathcal{B}, \mathcal{M}), e);

// Add branches to backtrack for each detected race in cnf

8:

for(e_c \in cnf)

9:

\tau_0 \cdot e_c \cdot \tau_1 := \tau; // Identify position of e_c in \tau

10.

\tau_1' := \tau_1 \cdot e with all events e' s.t. \mathcal{C}'(e_c) \leq \mathcal{C}'(e') removed;

// Set I to the set of initial events in \tau_1'

11.

I := \{e_i \in \tau_1' | \not\exists e_i' \in \tau_1' . C'(e_i') \leq C'(e_i)\};

12:

if(I \cap backtrack(\tau_0) = \varnothing) // No initial in the backtrack set

13:

e_i := pick an element in I;

backtrack(\tau_0) := backtrack(\tau_0) \cup \{tid(e_i)\};

14:

15:

}

16.

// Remove racing threads from the sleep set.

17.

Sleep' := Sleep;

if(\exists x. op accesses x){ // e is a memory access

18:

Sleep' := \emptyset;

19:

for(q \in Sleep) {

20.

21:

op' := the next instruction of q in (\mathbb{L}', \mathbb{M}');

22:

y := the memory location accessed by op';

\inf (\mathbf{y} \neq \mathbf{x} \text{ or (both op and op' are loads) or } (q = \mathsf{upd}(p)) or

(op' is a load and \mathcal{B}(q) contains a letter of the form (\mathbf{y}, -, -))

23:

24:

Sleep' := Sleep' \cup \{q\};

25:

26.

}

27:

TSO-Source-DPOR(\tau \cdot e, (\mathbb{L}', \mathbb{M}', \mathcal{C}', \mathcal{B}', \mathcal{M}'), Sleep');

28:

29:

Sleep := Sleep \cup \{p\};

30:

31: }

```

**Fig. 11** The source-DPOR algorithm of [1], adapted to TSO using chronological traces. The initial call is **TSO-Source-DPOR**  $(\varepsilon, (\mathbb{L}_0, \mathbb{M}_0, \lambda p.\lambda q.0, \lambda p.\varepsilon, \lambda \mathbf{x}(\perp, \emptyset)), \emptyset)$ , where  $(\mathbb{L}_0, \mathbb{M}_0)$  is an initial TSO configuration

When we explore a new branch, like the ones introduced above, we use a *sleep set* to ensure that events that are supposed to be delayed are delayed for sufficiently long. Thus when exploration of a new branch like the one above starts, the thread identifier of the previously racing event ( $e_c$ ) is inserted into the sleep set *Sleep* (on line 29) and the event may not be executed until the thread is removed from that set. A thread should be removed from the sleep set when the execution has proceeded such that executing its next event would have a different effect than previously explored. This happens as soon as an event is executed that would be in a race with the sleeping thread's next event. Therefore, on lines 17–27, we identify which of the sleeping threads race with e, and remove them from *Sleep*.

Example exploration Recall the program given in Fig. 5. In the example of Fig. 8 in the preliminaries, we gave a high-level explanation of how DPOR with chronological traces

## **TSO-post(**( $\mathbb{L}$ , $\mathbb{M}$ , $\mathcal{C}$ , $\mathcal{B}$ , $\mathcal{M}$ ),e)

```

1: (p, op, i) := e;

2: (\mathbb{R}, \mathbb{B}) := \mathbb{L}(p);

3: \mathbb{R}_{pc} := advance the program counter of p in \mathbb{R};

4: cnf := \varnothing; // Events racing with e

5: c_p := \mathcal{C}(p)[p \hookleftarrow i]; // Tick the clock for p

6: (\mathbb{L}', \mathbb{M}', \mathcal{C}', \mathcal{B}', \mathcal{M}') := (\mathbb{L}[p \longleftrightarrow (\mathbb{R}_{pc}, \mathbb{B})], \mathbb{M}, \mathcal{C}[e, p \longleftrightarrow c_p], \mathcal{B}, \mathcal{M});

// Case split based on instruction type

7: if(\exists x, r.op = store: x:= r) { // Store

\mathbb{L}' := \mathbb{L}'[p \hookleftarrow (\mathbb{R}_{pc}, \mathbb{B} \cdot (\mathbf{x}, \mathbb{R}(\$r)))]; // Add new store to buffer

\mathcal{B}' := \mathcal{B}[p \hookleftarrow \mathcal{B}(p) \cdot (\mathbf{x}, e, \bot)]; // Aux info for new buffer entry

9:

10: else\ if(\exists x.op = u(x)) \{ // Update \}

(\mathbf{x}, v) \cdot \mathbb{B}' := \mathbb{B};

\mathbb{L}' := \mathbb{L}[p \longleftrightarrow (\mathbb{R}_{\sf pc}, \mathbb{B}')]; // Remove store from buffer

12:

\mathbb{M}' := \mathbb{M}[\mathbf{x} \hookleftarrow v]; // \text{ Update memory}

(\mathbf{x}, e_s, e_r) \cdot \mathbf{b}_p := \mathcal{B}(p); // Get aux info for store

14:

\mathcal{B}' := \mathcal{B}[p \hookleftarrow b_p]; // Remove store from aux buffer

15:

(e_u, L) := \mathcal{M}(\mathbf{x});

16:

17:

if(e_r = \perp) {

\mathcal{M}' := \mathcal{M}[\mathbf{x} \hookleftarrow (e, L)];

18:

19:

\mathcal{M}' := \mathcal{M}[\mathbf{x} \hookleftarrow (e, \mathbf{L} \oplus e_r)];

20:

21:

\mathcal{C}' := \mathcal{C}[p, e \longleftrightarrow \mathsf{c}_p \sqcup \mathcal{C}(e_s) \sqcup \mathcal{C}(e_u) \sqcup \bigsqcup_{e_l \in \mathsf{L} \text{ s.t. upd}(\mathsf{tid}(e_l)) \neq p} \mathcal{C}(e_l)];

22:

\operatorname{cnf} := \left\{ e' \in \operatorname{L} \cup \{e_u\} \middle| \begin{array}{l} e' \neq \perp & \text{and} \ \mathcal{C}(e') \not \leq \operatorname{c}_p \sqcup \mathcal{C}(e_s) \ \text{and} \\ \operatorname{tid}(e') \neq p \ \text{and} \ \operatorname{upd}(\operatorname{tid}(e')) \neq p \end{array} \right.

23:

24: else\ if(\exists x, \hat{x}r.op = load: \hat{x}r:=x \text{ and } \mathbb{B}(x)=\bot) // Load from memory

\mathbb{L}' := \mathbb{L}[p \longleftrightarrow (\mathbb{R}_{pc}[\$r \longleftrightarrow \mathbb{M}(\mathbf{x})], \mathbb{B})];

25:

(e_u, L) := \mathcal{M}(\mathbf{x});

26:

27:

\mathcal{M}' := \mathcal{M}[\mathbf{x} \hookleftarrow (e_u, \mathbf{L} \oplus e)];

28:

if (e_u \neq \perp \text{ and } \operatorname{tid}(e_u) \neq \operatorname{upd}(p)) {

29:

\mathcal{C}' := \mathcal{C}[e, p \longleftrightarrow c_p \sqcup \mathcal{C}(e_u)];

30:

cnf := \{e_u\};

31:

32: else\ if(\exists x, r, v.op = load: r:=x \ and \ \mathbb{B}(x) = v \neq \perp  ( // Load from buffer

33:

\mathbb{L}' := \mathbb{L}[p \longleftrightarrow (\mathbb{R}_{pc}[\$r \longleftrightarrow \mathbb{B}(\mathbf{x})], \mathbb{B})];

\mathtt{b}_p \cdot (\mathbf{x}, e_s, e_r) \cdot \mathtt{b}_p{}' := \mathcal{B}(p) where

34:

b_p' contains no elements of the form (x, -, -);

\mathcal{B}' := \mathcal{B}[p \longleftrightarrow b_p \cdot (\mathbf{x}, e_s, e) \cdot b_p'];

35:

36: }else if(op = fence){ // Fence

\mathcal{C}' := \mathcal{C}[e, p \hookleftarrow c_p \sqcup \mathcal{C}(\mathsf{upd}(p))];

38: }else{ // Some local instruction

(\mathbb{L}', \mathbb{M}', \mathcal{C}', \mathcal{B}', \mathcal{M}') := perform appropriate local modifications;

39:

41: return ((\mathbb{L}', \mathbb{M}', \mathcal{C}', \mathcal{B}', \mathcal{M}'), cnf);

```

**Fig. 12** An algorithm which computes the extended configuration reached by executing the event e from the extended configuration ( $\mathbb{L}$ ,  $\mathbb{M}$ ,  $\mathcal{C}$ ,  $\mathcal{B}$ ,  $\mathcal{M}$ ). The algorithm returns the new configuration, as well as a set cnf, which contains the earlier events which race with e

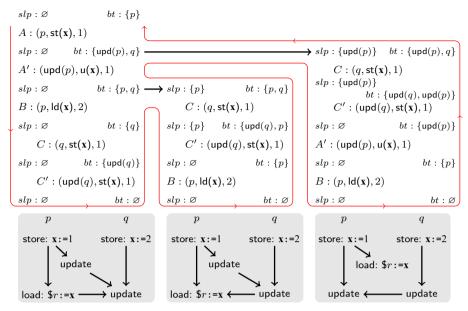

would proceed to explore that program. In Fig. 13, we revisit that exploration, and point to how it is achieved by the algorithm given in Fig. 11.

At first, the sleep set is empty, as well as the backtrack set of the current execution  $\tau = \varepsilon$ . At this point the threads p and q are enabled, but not the auxiliary threads  $\mathsf{upd}(p)$  and

Fig. 13 An exploration by TSO-Source-DPOR of the program in Fig. 5

upd(q). On line 1 of the algorithm, we pick the enabled thread p, and proceed to insert p into the backtrack set of  $\tau$  and execute the first instruction A of p. In Fig. 13, we see the execution of A at the top left. The  $slp:\emptyset$  and  $bt:\{p\}$  above A indicate that the sleep set at this point is empty, and the backtrack set is the singleton set containing p.

We continue arbitrarily scheduling the instructions of the enabled threads in the sequence A', B, C, C', down along the left-most column of Fig. 13. This gives us the first execution.

As we execute each event, the call to **TSO-post** on line 7 identifies the earlier events with which the current event has a conflict. During the first execution, two conflicts are identified: When the update C' is executed, we will have  $\mathcal{M}(\mathbf{x}) = (A', \{B\})$ , and we will find a conflict from A' to C' and one from B to C'. Hence on line 7 when C' is executed, cnf will be assigned  $\{A', B\}$ . When we enter the loop on lines 8-16, with  $e_c = A'$  we will first split the execution  $\tau = AA'BC$  into  $\tau_0 = A$  and  $\tau_1 = BC$  on line 9. Then we will identify the events in  $\tau_1 \cdot e = BCC'$  which are initial. Notice that C precedes C' in the happens-before order, but no events in BCC' precede B or C. Hence we assign  $I = \{B, C\}$ . On lines 12–15 we make certain that either B or C is in the backtrack set corresponding to the position immediately before A' was executed. In this case we choose to insert I tid(I) are into backtrack(I). Similarly in the next iteration of the loop on lines 8–16, we insert I0 into backtrack(I1).

As the first execution has been completely explored, the algorithm now starts to backtrack. After C' has been explored, on the bottom left in Fig. 13, its thread  $\mathsf{upd}(q)$  is added to the sleep set on line 29. Since the only thread in the backtrack set  $(\mathsf{upd}(q))$  is also in the sleep set, the loop on lines 3–30 terminates, and the call to **TSO-Source-DPOR** returns. The call to **TSO-Source-DPOR** which executed C immediately returns in the same way. In the call which executed B however, the backtrack set now contains one additional thread A which should be explored. Therefore, the algorithm takes an extra lap in the loop on lines 3-30, this time exploring the instruction C of A. This new branch is illustrated in Fig. 13 as the middle column. Notice that A is present in the sleep set, which prevents us from scheduling the load A until some other conflicting event has been executed.