# Formal Specification and Verification of Dynamic Parametrized Architectures

Alessandro Cimatti, Ivan Stojic<sup>(⊠)</sup>, and Stefano Tonetta

FBK-irst, Trento, Italy {cimatti,stojic,tonettas}@fbk.eu

Abstract. We propose a novel approach to the formal specification and verification of dynamic architectures that are at the core of adaptive systems such as critical infrastructure protection. Key features include run-time reconfiguration based on adding and removing components and connections, resulting in systems with unbounded number of components. We provide a logic-based specification of a Dynamic Parametrized Architecture (DPA), where parameters represent the infinite-state space of possible configurations, and first-order formulas represent the sets of initial configurations and reconfiguration transitions. We encode information flow properties as reachability problems of such DPAs, define a translation into an array-based transition system, and use a Satisfiability Modulo Theories (SMT)-based model checker to tackle a number of case studies.

#### 1 Introduction

In many applications, safety-critical systems are becoming more and more networked and open. For example, many critical infrastructures such as energy distribution, air traffic management, transport infrastructures, and industrial control nowadays employ remote communication and control. Critical infrastructure protection is becoming of paramount importance as witnessed for example by related European and US frameworks [1,2] which promote actions to make critical infrastructures more resilient.

In order to be resilient, a system must be adaptive, changing its architectural configuration at run-time, due to new requirements, component failures or attacks. A reconfiguration means adding and removing components and connections, so that the resulting system has an infinite state space where each state is an architectural configuration. In this context, simple reachability properties such as the existence of information flow paths become very challenging due to the interplay between communications and reconfigurations. The design, implementation, and certification of a system with such properties are the challenges of the European project CITADEL [3].

While the literature about the formal specification of dynamic software architectures is abundant [5,7–10,21,24–26,31–33], very few works consider their formal verification and none of them provided a concrete evaluation showing the feasibility of the proposed analysis.

<sup>©</sup> The Author(s) 2018 K. Havelund et al. (Eds.): FM 2018, LNCS 10951, pp. 625–644, 2018. https://doi.org/10.1007/978-3-319-95582-7\_37

If the number of components is bounded, formal verification can be reduced to static verification by encoding in the state if the component is active or not with possibly an additional component to control the (de)activation (see, for example, [9]). If, instead, new components can be added, the encoding is less trivial. In principle, parametrized verification, by verifying a system considering any number of replicas of components, seems a good candidate, but we need the capability to encode in the state the activation of an unbounded number of components.

In this paper, we propose Dynamic Parametrized Architectures (DPAs), which extend a standard architecture description of components and connections with (1) parameters and symbolic constraints to define a set of configurations, (2) symbolic constraints to define the sets of initial configurations and reconfigurations. In particular, the architectural topology is represented by indexed sets of components and symbolic variables that can enable/disable the connections, while the constraints are specified with first-order formulas with quantifiers over the set of indices.

We propose to use Satisfiability Modulo Theories (SMT)-based model checking for array-based transition systems [13,19], a syntactically restricted class of parametrized transition systems with states represented as arrays indexed by an arbitrary number of processes. We define carefully the fragment of first-order logic used in the architecture description so that we can provide a translation into array-based transition systems.

In this paper, we focus on simple information "can-flow" properties over DPAs: we check if information can pass from one component to another one through a sequence of communications between connected components and reconfigurations. We automatically translate the DPA and the properties into an array-based transition system and we verify the properties with Model Checker Modulo Theories (MCMT) [19].

Summarizing, the contributions of the paper are: (1) to define a new formal specification of dynamic architectures; (2) to translate the reachability problem of dynamic architectures into reachability problems for infinite-state array-based transition systems; (3) to provide a prototype implementation and an experimental evaluation of the feasibility of the approach.

The rest of the paper is structured as follows: Sect. 2 gives an account of related work; Sect. 3 exemplifies the problem using a concrete language; Sect. 4 defines the abstract syntax and semantics of DPAs; Sect. 5 describes array-based transition systems and the translation from DPAs; Sect. 6 presents some benchmarks and experimental results; and, finally, in Sect. 7, we draw some conclusions and directions for future works.

#### 2 Related Work

The approach closest to the one presented below is proposed in [31] as extension of the BIP (Behavior, Interaction, Priority) framework [6]. BIP has been extended for dynamic and parametrized connections in [7,23], and to allow

spawning new components and interactions in [9]. The work in [31] proposes a second-order logic to specify constraints on the evolution of the architecture including creation/removal of components. However, no model checking procedure is provided to verify such dynamic architectures. In this paper, we restrict the logic, for example avoiding second-order quantification, so that the language is still suitable to describe interesting dynamics but can be translated into array-based transition systems for model checking.

Since a system architecture can be seen as a graph of connections, graph grammars [29] are a good candidate for specification of dynamic architectures. In fact, in [21,26,32,33], the authors propose to model dynamic architectures in terms of graph transformation systems: the initial configuration is represented by a graph (or hypergraph) and reconfigurations as graph production rules, which are based on subgraph matching. In [21,26,32], there is no attempt at formal verification, while in [33] it is limited to finite-state model checking. Moreover, compared to our language, reconfigurations are limited to matching a finite subgraph which does not allow to express transition guards based on negation or updates that change sets of components. These limitations can be partly lifted considering infinite-state attributed graph grammars and related verification techniques [22]. After a first attempt to use these techniques as backends for DPAs, we concluded that in practice they do not scale very well on our benchmarks.

$\pi$ -calculus [27] is another clear candidate to represent the semantics of dynamic architectures, since it has the ability to describe the creation of processes and their dynamic synchronizations. As is, it does not clearly define the topology of the network, but works such as [10,24] use it as underlying semantics for dynamic extensions of architecture specification languages. Also in this context, no previous work provided a concrete proposal for model checking showing the feasibility of the approach.

The analysis of how information can flow from one component to another is addressed in many contexts such as program analysis, process modeling, access control, and flow latency analysis. The novel challenge addressed by this paper is posed by the complexity of the adaptive systems' architectures, for which design and verification is an open problem. We propose a very rich system specification and we provide verification techniques for simple information flow properties formalized as reachability problems.

In this paper, we consider information flow as reachability, which is well studied for standard state machine models. More complex information flow properties extensively studied in the literature on security are related to the notion of non-interference. In the seminal work of Goguen and Meseguer [20], the simple information flow property is extended to make sure that components at different levels of security do not interfere. The verification of non-interference on DPAs is an open problem left for future work.

## 3 An Example of a Dynamic Parametrized Architecture

In this section, we describe an example of a dynamic architecture in an extended version of the Architecture Analysis and Design Language (AADL) [16], which is an industrial language standardized by SAE International [30]. The concrete language extension is under definition [12] within the CITADEL project, while in this paper we focus on the underlying formal specification and semantics of DPAs.

In AADL, the system is specified in terms of component types, defining the interfaces and thus the input/output ports, and component implementations, defining how composite components are built from other components, called subcomponents, composed by connecting their ports. An example of an AADL component implementation is shown in Fig. 1. The system represents a network of computers, in which one is a database server that contains sensitive data; three are application servers that provide services to the clients, with two of them connected to the database server; and the others are clients. Each client is connected to one server and may be connected to other clients. As can be seen, the number of components and that of their connections are finite and static. The specification represents a single static architecture.

We now extend the example to consider an arbitrary number of servers and clients and to consider changes in the configurations so that computers and connections can be added/removed and computers can be compromised becoming untrusted (due to a fail-

**Fig. 1.** Example of a component implementation in AADL

ure or attack). We consider the system to be *safe* if no information can flow from the database to the untrusted clients; otherwise the system is *unsafe*. This dynamic version of the system is specified in Fig. 2 (for the moment, ignore the highlighted parts of the code), in an extended version of AADL. In particular, the extension has two layers:

1. Parametrized Architecture: the subcomponents can now be indexed sets (e.g., clients is a set indexed by C) and connections are specified iterating over the indices (e.g., there is a connection from servers[s] to clients[c] for each s in S, c in C); besides the sets of indices, the architecture is parametrized by other parameters that can be used in expressions that guard the connections (e.g., there exists a connection from servers[s] to clients[c] only if s = connectedTo[c]); notice that also parameters may be indexed sets.

2. Dynamic Parametrized Architecture: an initial formula defines the set of initial configurations; a set of reconfigurations defines the possible changes in the values of the parameters.

Analyzing the reconfigurations of the example (still ignoring the highlighted parts), we can see that every time an untrusted client is connected to a server, the server becomes untrusted as well. Since the connection with the database is disabled when the server is not trusted, one may erroneously think that no information can flow from the database to an untrusted client. In fact, the information can flow to the server while it is trusted, a reconfiguration may happen making the server untrusted, and the information can then flow to an untrusted client, making the system unsafe.

```

system implementation sys.impl

parameters

C: set of indices;

C: set of indices;

trustedClients: set indexed by C of bool;

trustedClients set indexed by C of index;

subcomponents

d: system databaseServer;

servers: set indexed by S of system applicationServer;

clients: set indexed by S of system applicationServer;

clients: set indexed by C of system Client;

connections

con1: port d.output -> servers[s].input if protected and trustedServers[s] for s in S;

con2: port servers[s].output -> clients[c].input if s = connectedTo[c] for c in C, r in C;

con3: port clients[c].output -> clients[r].input if not trustedClients[c] for c in C, r in C;

initial

not protected and

forall(c in C, forall (s in S, (not trustedClients[c] and s = connectedTo[c]) -> (not trustedServers[s])))) and

forall(c in C, forall (s not in S, s != connectedTo[c]));

reconfigurations

next(protected) = true:

exists(s not in S, next(S) = add(S, s) and next(trustedServers[s]) = true);

exists(s in S, mot protected and next(trustedServers[s]) = false);

exists(s in S, exists (c not in C, not trustedServers[s]) = sand next(trustedClients[c]) = true));

exists(s in S, exists (c in C, not trustedClients[c]) = s and next(trustedClients[c]) = true));

exists(s in S, exists (c in C, trustedClients[c]) = sand next(trustedServers[s]) = false));

exists(s in S, exists (c in C, trustedClients[c]) = sand next(trustedServers[s]) = false));

exists(s in S, exists (c in C, trustedClients[c]) = sand next(trustedServers[s]) = false));

exists(s in S, exists (c in C, trustedClients[c]) = sand next(trustedServers[s]) = false));

exists(s in S, exists (c in C, trustedClients[c]) = sand next(trustedServers[s]) = false));

exists(s in S, exists (c in C, trustedClients[c]) = sand next(trustedServers[s]) = false));

exists(s in S, exists (c in C, trustedClients[c]) = sand next(trustedServers[s]) = false));

exists(sin S, exists (c in C, trustedClients[c]) = sand next(trustedServers[s]) = false));

exists(sin S, exists (c in C, trustedClients[c]) = sand next(trustedServers[s]) = false));

```

Fig. 2. Example of a DPA specified in an extension of AADL

The version of the example with the highlighted parts is safe because it introduces two phases (represented by the protected parameter) and it allows connection to the database only in the protected mode, while reconfigurations downgrading the servers are allowed only in the unprotected mode. Proving automatically that this system is safe is quite challenging.

# 4 Formal Specification of Dynamic Parametrized Architectures

#### 4.1 Definitions

In the following, let N be a countable set of indexes (in practice, we set  $N = \mathbb{Z}$ ). An *index set* is a finite subset of N. Given a set S and an index set I, S is

indexed by I iff there exists a bijective mapping from I to S. If S is indexed by I, we write  $S = \{s_i\}_{i \in I}$ . An index set parameter is a variable whose domain is the set of finite subsets of N.

**Definition 1.** An architectural configuration is a pair (C, E), where C is a set of components and  $E \subseteq C \times C$  is a set of connections between components.

We now define a more structured version of architecture, still flat but in which components are grouped into sets. We use indexed sets of components. For example,  $I = \{1, 2, 3\}$  is a set of indexes and  $C = \{c_1, c_2, c_3\}$  and  $C' = \{c'_1, c'_2, c'_3\}$  are two sets of components indexed by I.

**Definition 2.** An architectural structured configuration is a pair (C, E), where:

- C is a finite set of disjoint sets of components indexed by some index sets;

- $-E \subseteq \bigcup_{C \in \mathcal{C}} \times \bigcup_{C \in \mathcal{C}}$  is a set of connections between components.

If  $c \in C$  and  $C \in C$  we write simply (abusing notation)  $c \in C$ .

For example, consider index sets  $I_1, I_2$ , where  $I_1 = \{1, 2, 3\}$ ,  $I_2 = \{2\}$ ,  $C = \{C_1, C_2, C_3\}$ ,  $C_1 = \{c_{1i}\}_{i \in I_1}$ ,  $C_2 = \{c_{2i}\}_{i \in I_1}$ ,  $C_3 = \{c_{3i}\}_{i \in I_2} = \{c_{32}\}$ ,  $E = \{\langle c_{1i}, c_{2i} \rangle \mid i \in I_1\}$ .

**Definition 3.** A system of parameters is a pair  $(\mathcal{I}, \mathcal{V})$  where  $\mathcal{I}$  is a finite set of symbols for index set parameters and  $\mathcal{V}$  is a finite set of symbols for indexed sets of parameters, where each  $V \in \mathcal{V}$  is associated with an index set parameter symbol  $I_V \in \mathcal{I}$  and with a sort sort V (in practice, sort  $V \in \{\text{bool}, \text{int}\}$ ).

**Definition 4.** An assignment to a system of parameters  $(\mathcal{I}, \mathcal{V})$  is a tuple  $\mu = (\mu_{\mathcal{I}}, \{\mu_{V}\}_{V \in \mathcal{V}})$ , where

- $\mu_{\mathcal{I}}: \mathcal{I} \to \{S \subset N : Sfinite\};$

- For  $V \in \mathcal{V}$ ,  $\mu_V : \mu_{\mathcal{I}}(I_V) \to R(sort_V)$  (in practice,  $R(\texttt{bool}) = \mathbb{B} = \{\top, \bot\}$  and  $R(\texttt{int}) = \mathbb{Z}$ ).

The following definitions refer to formulas of the logic for systems of parameters and the evaluation (under an assignment  $\mu$ )  $\llbracket \cdot \rrbracket_{\mu}$  of its expressions and formulas. These are defined later in Sect. 4.2.

**Definition 5.** A parametrized architecture is a tuple  $A = (\mathcal{I}, \mathcal{V}, \mathcal{P}, \Psi, \Phi)$  where

- $(\mathcal{I}, \mathcal{V})$  is a system of parameters;

- $\mathcal{P}$  is a finite set of parametrized indexed sets of components; each set  $P \in \mathcal{P}$  is associated with an index set  $I_P \in \mathcal{I}$ ;

- $-\Psi = \{\psi_P(x)\}_{P \in \mathcal{P}}$  is a set of formulas (component guards) over  $(\mathcal{I}, \mathcal{V})$  and a free variable x;

- $\Phi = {\phi_{PQ}(x,y)}_{P,Q\in\mathcal{P}}$  is a set of formulas (connection guards) over  $(\mathcal{I},\mathcal{V})$  and free variables x, y.

Given an assignment  $\mu$  to the system of parameters  $(\mathcal{I}, \mathcal{V})$ , the instantiated (structured architectural) configuration defined by the assignment  $\mu$  is given by  $\mu(A) := (\mathcal{C}, E)$  (we also write  $(\mathcal{C}_{\mu}, E_{\mu})$ ) where

- $-\mathcal{C} = \{C_{\mu P} : P \in \mathcal{P}\}.$  For all  $C_{\mu P} \in \mathcal{C}$ , for all indexes  $i, c_{Pi} \in C_{\mu P}$  iff  $i \in \mu_{\mathcal{I}}(I_P)$  and  $\llbracket \psi_P(i/x) \rrbracket_{\mu} = \top$ .

- for all  $C_{\mu P}, C_{\mu Q} \in \mathcal{C}$ , for all component instances  $c_{Pi} \in C_{\mu P}, c_{Qj} \in C_{\mu Q},$   $(c_{Pi}, c_{Qj}) \in E$  iff  $\llbracket \phi_{PQ}(i/x, j/y) \rrbracket_{\mu} = \top$ .

Syntactic restrictions: formulas in  $\Psi$  and  $\Phi$  are quantifier-free and do not contain index set predicates =,  $\subseteq$ .

Example: For  $\mathcal{I} = \{I_1, I_2\}$ ,  $\mathcal{V} = \{V\}$ , V a set of Boolean variables, with  $I_V = I_1$ ,  $\mathcal{P} = \{P_1, P_2, P_3\}$ ,  $I_{P_1} = I_1$ ,  $I_{P_2} = I_1$ ,  $I_{P_3} = I_2$ ,  $\psi_{P_1}(x) = \psi_{P_2}(x) = \psi_{P_3}(x) := \top$ ,  $\phi_{P_1 P_2}(x,y) := x = y \land x \in I_V \land V[x], \phi_{P_1 P_3}(x,y) := x \in I_V \land \neg V[x], \phi_{P_2 P_3}(x,y) = \phi_{P_2 P_1}(x,y) = \phi_{P_3 P_1}(x,y) = \phi_{P_3 P_2}(x,y) := \bot$ . By assigning  $\mu_{\mathcal{I}}(I_1) = \{1,2,3\}$ ,  $\mu_{\mathcal{I}}(I_2) = \{2\}$ ,  $\mu_{V}(1) = \mu_{V}(2) = \mu_{V}(3) = \top$ , we get the configuration in the previous example.

**Definition 6.** A dynamic parametrized architecture is a tuple  $(A, \iota, \kappa, \tau)$ , where

- $A = (\mathcal{I}, \mathcal{V}, \mathcal{P}, \Psi, \Phi)$  is a parametrized architecture;

- $\iota$  is a formula over  $(\mathcal{I}, \mathcal{V})$ , specifying the set of initial assignments;

- $\kappa$  is a formula over  $(\mathcal{I}, \mathcal{V})$ , specifying the invariant;

- $-\tau$  is a transition formula over  $(\mathcal{I}, \mathcal{V})$ , specifying the reconfiguration transitions.

The dynamic parametrized architecture defines a dynamically changing architecture as a transition system over (structured architectural) configurations obtained by instantiation from A. The set of initial configurations is given by

```

\{\mu(A): \mu \text{ is an assignment to } (\mathcal{I}, \mathcal{V}) \text{ such that } \llbracket \iota \rrbracket_{\mu} = \top \text{ and } \llbracket \kappa \rrbracket_{\mu} = \top \}.

```

A configuration  $\mu'(A)$  is directly reachable from a configuration  $\mu(A)$  iff  $\llbracket \tau \rrbracket_{\mu\mu'} = \top$  and  $\llbracket \kappa \rrbracket_{\mu'} = \top$ .

Syntactic restrictions:

- $\iota$  is of the form  $\forall_{\underline{I}_1}\underline{i}_1\forall_{\underline{I}_2^C}\underline{i}_2$   $\alpha$ , where  $\alpha$  is a quantifier-free formula in which index set predicates =,  $\subseteq$  do not appear under negation.

- $\kappa$  is a quantifier-free formula without index set predicates =,  $\subseteq$ .

- τ is a disjunction of transition formulas of the form ∃<sub>I₁</sub>i₁∃<sub>I₂</sub>i₂ (α ∧ β ∧ γβ) where I₁, I₂ ⊆ I, α is a quantifier-free formula, β is a conjunction of transition formulas of the forms 1) I' = I ∪ {tk}k, 2) I' = I \ {tk}k, 3) t ∈ I', 4) V'[t] = e, 5) ∀<sub>I'<sub>V</sub></sub>, j V'[j] = e, where I ∈ I, I' ∈ I' are variables of sort is (each variable I' ∈ I' may appear at most once), t, t<sub>k</sub> are terms over (I, V) of sort idx, V' ∈ V' is a variable of one of the sorts vs<sub>k</sub> (for each V', either atoms of the form 4 appear in β, or at most a single atom of the form 5 appears: atoms of forms 4, 5 never appear together), e are terms over (I, V) of sorts el<sub>k</sub>, and j is a variable of sort idx; furthermore, value V'[t<sub>k</sub>] of every introduced (by an atom of form 1, with I' = I'<sub>V</sub>, and I = I<sub>V</sub>) parameter must be set in β with an atom of form 4 or 5; finally, the frame condition γ<sub>β</sub> is a conjunction of

- transition formulas  $\forall_{I'_{V'}}, j\left(\left(\bigwedge_{t \in t_{V'}}(j \neq t)\right) \to V'[j] = V[j]\right)$  for all  $V' \in \mathcal{V}$  which do not appear in a conjunct of form 5 in  $\beta$ , where  $t_{V'}$  is the (possibly empty) set of all terms which appear as indexes of V' in  $\beta$ , and

- transition formulas I' = I for all  $I' \in \mathcal{I}'$  which do not appear in conjuncts of forms 1, 2 in  $\beta$ .

(In practice, when specifying the transition formulas, the frame condition  $\gamma_{\beta}$  is generated automatically from  $\beta$ , instead of being specified directly by the user.)

Example: Consider the parametrized architecture from the previous example, with  $\iota := I_1 = \{1,2,3\} \land I_2 = \{2\} \land V[1] \land V[2] \land V[3];$ ,  $\kappa := \top$  and  $\tau := \tau_1 \lor \tau_2$ , where  $\tau_1 := \exists_{I_1^C} i \, (I_1' = I_1 \cup \{i\} \land V'[i])$  and  $\tau_2 := \exists_{I_1} i \, (\neg V'[i])$ . This defines the set of initial architectures which contains only the single architecture from the previous example and two transitions. The transition  $\tau_1$  adds a new index  $i \in I_1^C$  into the index set  $I_1$ , adding two new components  $C_{1i}$  and  $C_{2i}$  and a new parameter V[i] and sets the value of the newly added parameter V[i] to  $\top$ , adding a connection between the two new components  $C_{1i}$  and  $C_{2i}$ . The transition  $\tau_2$  changes the value of some V[i] to  $\bot$ , removing the connection between components  $C_{1i}$  and  $C_{2i}$  and adding connections between component  $C_{1i}$  and each of the components  $C_{3i}$ ,  $j \in I_2$ .

**Definition 7.** Given a dynamic parametrized architecture  $(A, \iota, \kappa, \tau)$ , where  $A = (\mathcal{I}, \mathcal{V}, \mathcal{P}, \Psi, \Phi)$ , a configuration is an assignment to the system of parameters  $(\mathcal{I}, \mathcal{V})$ . For a configuration  $\mu(A) = (\mathcal{C}, E)$ , a communication event is a connection  $e \in E$ .

Trace of the dynamic parametrized architecture is a sequence  $e_1, e_2, \ldots$  of configurations and communication events, such that:

- $e_1 = \mu_1$  is a configuration such that  $\mu_1(A)$  is in the set of initial configurations.

- The subsequence  $e_{k_1}, e_{k_2}, \ldots$  of all configurations in the trace is such that for all  $k_i$ ,  $e_{k_{i+1}}(A)$  (if it exists) is directly reachable from  $e_{k_i}(A)$ .

- For all communication events  $e_k = (c_k, c'_k)$  in the trace,  $(c_k, c'_k) \in E_{e_{r(k)}}$ , where  $e_{r(k)}$ ,  $r(k) := \max\{n \in \mathbb{N} : n < k, e_n \text{ is a configuration}\}$ , is the last configuration prior to  $e_k$ .

**Definition 8.** An instance of the dynamic information flow problem is a tuple  $(D, P_{src}, \rho_{src}, P_{dst}, \rho_{dst})$  where

- $D = (A, \iota, \kappa, \tau)$  is a dynamic parametrized architecture;

- $P_{src} \in \mathcal{P}_A$  and  $P_{dst} \in \mathcal{P}_A$  are (source and destination) parametrized indexed sets of components;

- $\rho_{src}(x)$  and  $\rho_{dst}(x)$  (source and destination guard) are formulas over  $(\mathcal{I}_A, \mathcal{V}_A)$ .

The problem is to determine whether there exists a finite trace (called information flow witness trace)  $e_1, e_2, \ldots, e_n$  of D with a subtrace  $e_{k_1} = (c_{k_1}, c'_{k_1}), \ldots, e_{k_m} = (c_{k_m}, c'_{k_m})$  of communication events such that:

- $c_{k_1} = c_{P_{src}i_{src}} \in C_{e_{r(k_1)}P_{src}}$  for some  $i_{src}$ , and  $[\![\rho_{src}(i_{src}/x)]\!]_{e_{r(k_1)}} = \top$  (the information originates in a source component);

- $c'_{k_m} = c_{P_{dst}i_{dst}} \in C_{e_{r(k_m)}P_{dst}}$  for some  $i_{dst}$ , and  $[\![\rho_{dst}(i_{dst}/x)]\!]_{e_{r(k_m)}} = \top$  (the information is received by a destination component);

- for all n such that  $1 \leq n < m$ ,  $c'_{k_n} = c_{k_{n+1}}$  (the intermediate components form a chain over which the information propagates);

- for all  $n, 1 \leq n < m$ , for all configurations  $e_{k'}$  such that  $k_n < k' < k_{n+1}$ ,  $c_{k_{n+1}} \in \mathcal{C}_{e_{k'}}$  (after an intermediate component receives the information and before it passes it on, it is not replaced by a fresh component with the same index).

If such a trace exists, we say that information may flow from a source component which satisfies the source condition given by  $P_{src}$ ,  $\rho_{src}$  to a destination component which satisfies the destination condition given by  $P_{dst}$ ,  $\rho_{dst}$ .

Syntactic restrictions:  $\rho_{src}$  and  $\rho_{dst}$  are quantifier-free formulas, without index set predicates =,  $\subseteq$ .

#### 4.2 Logic for Systems of Parameters

In the following, we define a many-sorted first-order logic [15]. Signatures contain no quantifier symbols except those explicitly mentioned.

**Syntax.** Theory  $T_{IDX} = (\Sigma_{IDX}, \mathcal{C}_{IDX})$  of indexes with a single sort idx (in practice, we are using the theory of integers with sort int and with standard operators).

A finite number K of theories  $T_{EL_k} = (\Sigma_{EL_k}, \mathcal{C}_{EL_k})$  of elements, each with a single sort  $el_k$  with a distinguished constant symbol  $d_{el_k}$  (a default value) (in practice, we consider the theory of booleans with sort bool and the theory of integers, the same as the theory  $T_{IDX}$ ).

The theory  $SP_{IDX}^{EL_1,...,EL_K}$  (or simply  $SP_{IDX}^{EL}$ ) of systems of parameters with indexes in  $T_{IDX}$  and elements in  $EL_1, ..., EL_K$  is a combination of the above theories. Its sort symbols are  $\mathrm{idx}$ ,  $\mathrm{is}$ ,  $\mathrm{el}_1, ..., \mathrm{el}_K$ ,  $\mathrm{vs}_1, ..., \mathrm{vs}_K$ , where is is a sort for index sets and  $\mathrm{vs}_k$  is a sort for indexed sets of parameters of sort  $\mathrm{el}_k$ . The set of variable symbols for each sort  $\mathrm{vs}_k$  contains a countable set of variables  $\{V_{k,n}^I\}_{n\in\mathbb{N}}$  for each variable symbol I of sort is (we omit the superscript and subscripts when they are clear from the context). The signature is the union of the signatures of the above theories,  $\Sigma_{IDX} \cup \bigcup_{k=1}^K \Sigma_{EL_k}$ , with the addition of: for sort idx, quantifier symbols  $\forall$ ,  $\exists$ , and  $\forall$ <sub>I</sub>,  $\forall$ <sub>IC</sub>,  $\exists$ <sub>I</sub>,  $\exists$ <sub>IC</sub> for all variables I of the sort is; predicate symbol  $\in$  of sort (idx, is); predicate symbols =,  $\subseteq$  of sort (is, is); function symbols  $\cup$ ,  $\cap$ ,  $\setminus$  of sort (is, is, is); for every  $n \in \mathbb{N}$ , n-ary function symbol  $\{\cdot, \ldots, \cdot\}^{(n)}$  (we write simply  $\{\cdot, \ldots, \cdot\}$ ) of sort (idx, ..., idx, is); function symbols  $\cdot [\cdot]_k, k = 1, \ldots, K$  (we write simply  $\cdot [\cdot]$ ) of sorts ( $\mathrm{vs}_k$ , idx,  $\mathrm{el}_k$ ).

**Semantics.** A structure  $\mathcal{M} = (\mathrm{idx}^{\mathcal{M}}, \mathrm{is}^{\mathcal{M}}, \mathrm{el}_1^{\mathcal{M}}, \dots, \mathrm{el}_k^{\mathcal{M}}, \mathrm{vs}_1^{\mathcal{M}}, \dots, \mathrm{vs}_k^{\mathcal{M}}, \mathcal{I}_{\mathcal{M}})$  for  $SP_{IDX}^{EL}$  is restricted in the following manner:

- $is^{\mathcal{M}}$  is the power set of  $idx^{\mathcal{M}}$ ;

- each  $vs_k^{\mathcal{M}}$  is the set of all (total and partial) functions from  $idx^{\mathcal{M}}$  to  $el_k^{\mathcal{M}}$ ;

- $\in$  is interpreted as the standard set membership predicate;

- -=,  $\subseteq$  are interpreted as the standard set equality and subset predicates;

- $-\cup$ ,  $\cap$ ,  $\setminus$  are interpreted as the standard set union, intersection and difference on  $is^{\mathcal{M}}$ , respectively;

- for every  $n \in \mathbb{N}$ ,  $\mathcal{I}_{\mathcal{M}}(\{\cdot,\ldots,\cdot\}^{(n)})$  is the function that maps the *n*-tuple of its arguments to the set of indexes containing exactly the arguments, i.e. it maps every  $(x_1,\ldots,x_n) \in (\mathrm{idx}^{\mathcal{M}})^n$  to  $\{x_1,\ldots,x_n\} \in \mathrm{is}^{\mathcal{M}};$

- $-\cdot [\cdot]_k, k = 1, \ldots, K$  are interpreted as function applications:  $(V[i])^{\mathcal{M}} := V^{\mathcal{M}}(i^{\mathcal{M}}).$

The structure  $\mathcal{M}$  is a model of  $SP_{IDX}^{EL}$  iff it satisfies the above restrictions and  $(\mathrm{idx}^{\mathcal{M}}, \mathcal{I}_{\mathcal{M}}|_{\Sigma_{IDX}}), (\mathrm{el}_{1}^{\mathcal{M}}, \mathcal{I}_{\mathcal{M}}|_{\Sigma_{EL_{1}}}), \ldots, (\mathrm{el}_{K}^{\mathcal{M}}, \mathcal{I}_{\mathcal{M}}|_{\Sigma_{EL_{K}}})$  are models of  $T_{IDX}$ ,  $T_{EL_{1}}, \ldots, T_{EL_{K}}$ , respectively.

**Definition 9.** A formula (resp. term) over a system of parameters  $(\mathcal{I}, \mathcal{V})$  is a formula (resp. term) of the logic  $SP_{IDX}^{EL}$  in which the only occurring symbols of sort idx are from  $\mathcal{I}$  and the only occurring symbols of sort  $vs_k$  are from the set  $\{V \in \mathcal{V} : sort_V = el_k\}$ , for k = 1, ..., K. Furthermore, in the formula all accesses  $V[\cdot]$  to parameters  $V \in \mathcal{V}$  are guarded parameter accesses, i.e. each atom  $\alpha(V[t])$  that contains a term of the form V[t] must occur in conjunction with a guard which ensures that index term t is present in the corresponding index set:  $t \in I_V \land \alpha(V[t])$ .

**Definition 10.** A transition formula over the system of parameters  $(\mathcal{I}, \mathcal{V})$  is a formula of the logic  $SP_{IDX}^{EL}$  in which the only occurring symbols of sort idx are from  $\mathcal{I} \cup \mathcal{I}'$  and the only occurring symbols of sort  $vs_k$  are from the set  $\{W \in \mathcal{V} \cup \mathcal{V}' : sort_W = el_k\}$ , for  $k = 1, \ldots, K$ . Furthermore, all accesses  $W[\cdot]$  to parameters  $W \in \mathcal{V} \cup \mathcal{V}'$  are guarded parameter accesses (as defined in Definition 9).

The subscripted quantifier symbols are a syntactic sugar for quantification over index sets and their complements: all occurrences of the quantifiers  $\forall_{I} i \ \phi$ ,  $\forall_{I} c i \ \phi$ ,  $\exists_{I} c i \ \phi$ —where I is a variable of sort is, i is a variable of sort idx, and  $\phi$  is a formula—are rewritten to  $\forall i \ (i \in I \to \phi), \ \forall i \ (i \notin I \to \phi), \ \exists i \ (i \in I \land \phi), \ \exists i \ (i \notin I \land \phi), \ \text{respectively}$ , after which the formula is evaluated in the standard manner.

**Definition 11.** Evaluation  $[\![\phi]\!]_{\mu}$  with respect to an assignment  $\mu$  to a system of parameters  $(\mathcal{I}, \mathcal{V})$ , of a formula (or a term)  $\phi$  over  $(\mathcal{I}, \mathcal{V})$  is defined by interpreting I with  $I^{\mathcal{M}} = \mu_{\mathcal{I}}(I)$  for every  $I \in \mathcal{I}$  and interpreting V[x] as follows for every  $V \in \mathcal{V}$ :  $(V[x])^{\mathcal{M}} = \mu_{V}(x^{\mathcal{M}})$  if  $x^{\mathcal{M}} \in \mu(I_{V})$ , and  $(V[x])^{\mathcal{M}} = d_{\mathtt{sort}_{V}}^{\mathcal{M}}$  otherwise. The evaluation  $[\![\phi]\!]_{\mu\mu'}$  of a transition formula with respect to two assignments  $\mu$ ,  $\mu'$  is defined by interpreting, in the above manner,  $(\mathcal{I}, \mathcal{V})$  with  $\mu$  and  $(\mathcal{I}', \mathcal{V}')$  with  $\mu'$ .

## 5 Analysis with SMT-Based Model Checking

#### 5.1 Background Notions on SMT-Based Model Checking

Many-sorted first-order logic of arrays. The target logic for the translation is the many-sorted first-order logic [15] with theories for indexes, elements and arrays as defined in [18]. Following that paper, we fix a theory  $T_I = (\Sigma_I, \mathcal{C}_I)$  for indexes whose only sort symbol is index and we fix theories  $T_{E_k} = (\Sigma_{E_k}, \mathcal{C}_{E_k}), k = 1, \ldots, K$  whose only sort symbols are  $\mathsf{elem}_k$ , respectively. The theory  $A_I^{E_1, \ldots, E_K}$  (or simply  $A_I^E$ ) of arrays with indexes in  $T_I$  and elements in  $E_1, \ldots, E_K$  is defined as the combination of theories  $T_I, T_{E_1}, \ldots, T_{E_K}$  as follows. The sort symbols of  $A_I^E$  are index,  $\mathsf{elem}_1, \ldots, \mathsf{elem}_K$ ,  $\mathsf{array}_1, \ldots, \mathsf{array}_K$ , the signature is  $\Sigma := \Sigma_I \cup \bigcup_{k=1}^K \Sigma_{E_i} \cup \bigcup_{k=1}^K \{ \cdot [\cdot]_k \}$  where  $\cdot [\cdot]_k$  are function symbols of sorts  $(\mathsf{array}_k, \mathsf{index}, \mathsf{elem}_k)$ . A structure  $\mathcal{M} = (\mathsf{index}^\mathcal{M}, \mathsf{elem}_1^\mathcal{M}, \ldots, \mathsf{elem}_K^\mathcal{M}, \mathsf{array}_1^\mathcal{M}, \ldots, \mathsf{array}_K^\mathcal{M}, \mathcal{I})$  is a model of  $A_I^E$  iff  $\mathsf{array}_k^\mathcal{M}$  are sets of all functions from  $\mathsf{index}^\mathcal{M}$  to  $\mathsf{elem}_k^\mathcal{M}$ , respectively, the function symbols  $\cdot [\cdot]_k$  are interpreted as function applications, and  $\mathcal{M}_I = (\mathsf{index}^\mathcal{M}, \mathcal{I} \upharpoonright_{\Sigma_I}), \, \mathcal{M}_{E_k} = (\mathsf{elem}_k^\mathcal{M}, \mathcal{I} \upharpoonright_{\Sigma_{E_k}})$  are models of  $T_I$ ,  $T_{E_k}, k = 1, \ldots, K$ , respectively.

**Array-Based Transition Systems.** In the following, i, j denote variables of the sort index,  $\underline{i}$  denotes a set of such variables, a denotes a variable of one of the array sorts,  $\underline{a}$  denotes a set of such variables, notation  $\underline{a}[\underline{i}]$  denotes the set of terms  $\{a[\underline{i}]: a \in \underline{a}, i \in \underline{i}\}$ , and  $\phi(x), \psi(x)$  denote quantifier free  $\Sigma(x)$  formulas.

As in [18], an array-based (transition) system (for  $(T_I, T_{E_1}, \ldots, T_{E_K})$ ) is a triple S = (a, Init, Tr) where

- $-\underline{a} = \{a_1, \dots, a_n\}$  is a set of state variables of the sorts  $\mathtt{array}_1, \dots, \mathtt{array}_K$ .

- $Init(\underline{a})$  is the *initial*  $\Sigma(\underline{a})$ -formula of the form

$$\forall \underline{i}.\phi(\underline{i},\underline{a}[\underline{i}]). \tag{1}$$

-  $Tr(\underline{a}, \underline{a}')$  is the transition  $\Sigma(\underline{a}, \underline{a}')$ -formula and is a disjunction of formulas of the form

$$\exists \underline{i} \left( \psi(\underline{i}, \underline{a}[\underline{i}]) \land \bigwedge_{k=1}^{n} \forall j \ a'_{k}[j] = t_{k}(\underline{i}, \underline{a}[\underline{i}], j, \underline{a}[j]) \right)$$

(2)

where each  $t_k$  is a  $\Sigma(\underline{a})$ -term which may contain nested if-then-else operators.

Given an array-based system  $S = (\underline{a}, Init, Tr)$  and a  $\Sigma(\underline{a})$ -formula U (unsafe formula) of the form

$$\exists \underline{i}.\phi(\underline{i},\underline{a}[\underline{i}]) \tag{3}$$

an instance of the array-based safety problem is to decide whether there exists  $n \in \mathbb{N}$  such that the formula  $Init(\underline{a}_0) \wedge Tr(\underline{a}_0,\underline{a}_1) \wedge \cdots \wedge Tr(\underline{a}_{n-1},\underline{a}_n) \wedge U(\underline{a}_n)$  is  $A_I^E$ -satisfiable.

Decidability of the Array-Based Safety Problem. The array-based safety problem is in general undecidable (Thm. 4.1. in [18]), but it becomes decidable

under 1) the following assumptions on the theory  $T_I$  of indexes: local finiteness, closedness under substructures, decidability of  $SMT(T_I)$ , 2) assumptions of local finiteness of  $T_E$  and of decidability of  $SMT(T_E)$ , and 3) further assumptions on the array-based transition system under analysis (for details see Theorem 3.3. and Theorem 4.6. in [18]).

#### 5.2 Encoding into SMT-Based Model Checking

**Translation of Formulas.** We recursively define the translation  $\cdot^A$  of formulas and transition formulas of  $SP_{IDX}^{EL}$  to formulas of  $A_I^E$ . We set the index and element sorts to correspond, i.e. index := idx and elem<sub>k</sub> := el<sub>k</sub>, k = 1, ..., K. In practice, we set  $T_I$  to be the theory of integers (with sort index = int), number of element theories to K = 2, and we set  $E_1 = T_I$  and  $E_2$  to be the theory of Booleans (with sort elem<sub>2</sub> = bool).

- Symbols of the sorts idx and  $el_k, k = 1, ..., K$  are treated as symbols of the sorts index,  $elem_k, k = 1, ..., K$ , respectively.

- For a variable I of sort is,  $I^{\mathcal{A}} := a_I$ , where  $a_I$  is of the sort  $\mathtt{array}_{\mathtt{bool}}$ .

- For a variable V of sort  $vs_k$ ,  $V^A := a_V$ , where  $a_V$  is of the sort  $array_{elem_i}$ .

- For a term t of sort idx and term T of sort is,  $(t \in T)^A := T^{A_t}$ .

- For terms  $T_1, T_2$  of sort is,  $(T_1 \cap T_2)^{\mathcal{A}_t} := T_1^{\mathcal{A}_t} \wedge T_2^{\mathcal{A}_t}$ ; analogously for  $\cup$  and  $\setminus$ .

- For a variable I of sort is,  $I^{A_t} := I^A[t^A]$ .

- $(\{e_1, \dots, e_n\})^{A_t} := \bigvee_{k=1}^n (t^A = e_k^A).$

- For terms  $T_1, T_2$  of sort is,  $(T_1 = T_2)^{\mathcal{A}} := \forall i \ (T_1^{\mathcal{A}_i} = T_2^{\mathcal{A}_i})$ , where i is a fresh variable of sort idx; analogously for  $\subseteq$  which is translated using  $\rightarrow$ .

- For a variable V of sort  $vs_k$  and a term t of sort idx,  $(V[t])^A := V^A[t^A]$ .

- Other logical connectives, quantifiers and operators are present in both logics and are translated directly, e.g.  $(e_1 \leq e_2)^{\mathcal{A}} := e_1^{\mathcal{A}} \leq e_2^{\mathcal{A}}$  and  $(\phi_1 \wedge \phi_2)^{\mathcal{A}} := \phi_1^{\mathcal{A}} \wedge \phi_2^{\mathcal{A}}$ .

Translation of a Dynamic Information Flow Problem to an Array-Based Safety Problem. Given a dynamic parametrized architecture  $D = (A, \iota, \kappa, \tau)$  where  $A = (\mathcal{I}, \mathcal{V}, \mathcal{P}, \Psi, \Phi)$ , and given an information flow problem instance  $(D, P_{src}, \rho_{src}, P_{dst}, \rho_{dst})$ , we generate a safety problem  $(\mathcal{S}, U)$  where  $\mathcal{S} = (a, Init, Tr)$ , as follows.

Given a system of parameters  $(\mathcal{I}, \mathcal{V})$ , we set  $\underline{a}$  to be the (disjoint) union:

$$\underline{a} := \{a_I : I \in \mathcal{I}, sort(a_I) = \mathtt{array_{bool}}\}$$

$$\cup \{a_V : V \in \mathcal{V}, sort(a_V) = \mathtt{array_{sort}_V}\}$$

$$\cup \{a_P : P \in \mathcal{P}, sort(a_P) = \mathtt{array_{bool}}\},$$

$$(4)$$

of the set of boolean array symbols  $a_I$  which model index sets, the set of array symbols  $a_V$  which model sets of parameters, and the set of boolean array symbols  $a_P$  which model information taint of the component instances.

The initial formula *Init* is set to

$$\iota^{\mathcal{A}} \wedge \kappa^{\mathcal{A}} \wedge \forall j \left( a_{P_{src}}[j] = \left( a_{I_{P_{src}}}[j] \wedge \psi_{P_{src}}(j/x)^{\mathcal{A}} \wedge \rho_{src}(j/x)^{\mathcal{A}} \right) \right)$$

$$\wedge \bigwedge_{P \in \mathcal{P} \setminus \{P_{src}\}} \forall j \ a_{P}[j] = \bot.$$

(5)

Here the third conjunct models the initial taint of the source components, by specifying that a source component with index j is tainted iff it is present in the system and satisfies the constraint  $\rho_{src}$ , and the last conjunct models the fact that initially all non-source components are not tainted.

Recall that  $\tau = \bigvee_k \tau_k$ , where  $\tau_k$  are of the form  $\exists_{\underline{I}_1} \underline{i}_1 \exists_{\underline{I}_2^C} \underline{i}_2 (\alpha_k \wedge \beta_k \wedge \gamma_{\beta_k})$  (see Definition 6). The transition formula Tr is set to

$$\bigvee_{P,Q \in \mathcal{P}} Taint(P,Q) \vee \bigvee_{k} Reconf_{k}. \tag{6}$$

Here Taint(P,Q) is the following formula that models taint propagation between two connected component instances of which the first one is tainted:

$$\exists i_1 \exists i_2 \ \left( \phi_{PQ}(i_1/x, i_2/y)^{\mathcal{A}} \wedge a_{I_P}[i_1] \wedge \psi_P(i_1/x)^{\mathcal{A}} \wedge a_{I_Q}[i_2] \wedge \psi_Q(i_2/x)^{\mathcal{A}} \right. \\ \wedge a_P[i_1] \wedge \forall j \ \left( a'_O[j] = (j = i_2 ? \top : a_Q[j]) \right) \wedge \bigwedge_{a \neq a_O} \forall j \ \left( a'[j] = a[j] \right).$$

(7)

$Reconf_k$  is obtained from  $\tau_k$  by the following steps.

Differentiation of Primed Parameter Accesses. We say that accesses to a primed parameter  $V' \in \mathcal{V}'$  in  $\tau_k$  are differentiated if for all pairs of conjuncts of form 4 in  $\beta_k$  as defined in Definition 6,  $V'[t_1] = e_1$  and  $V'[t_2] = e_2$ ,  $\alpha_k$  contains a top-level conjunct  $(t_1 \neq t_2)$ , i.e.,  $\alpha_k$  is of the form  $\alpha'_k \wedge (t_1 \neq t_2)$ . We may assume that in  $\tau_k$ , accesses to all primed parameters  $V' \in \mathcal{V}'$  are differentiated. Note that if the accesses to some primed parameter  $V' \in \mathcal{V}'$  in  $\tau_k$  are not differentiated, then for a pair of undifferentiated accesses  $V'[t_1] = e_1$  and  $V'[t_2] = e_2$  formula  $\tau_k$  can be rewritten as a disjunction of two formulas  $\tau_k^=$  and  $\tau_k^\neq$  which are of the same general form as  $\tau_k$  and are defined by

$$\begin{array}{l} -\tau_k^{=} := \exists_{\underline{I}_1}\underline{i}_1\exists_{\underline{I}_2^C}\underline{i}_2\left(\alpha_k^{=} \wedge \beta_k^{=} \wedge \gamma_{\beta_k^{=}}\right) \text{ where } \alpha_k^{=} := \alpha_k \wedge (t_1 = t_2) \wedge (e_1 = e_2),\\ \text{and } \beta_k^{=} \text{ is obtained from } \beta_k \text{ by removing the conjunct } V'[t_2] = e_2; \end{array}$$

$$-\tau_k^{\neq} := \exists_{\underline{I}_1} \underline{i}_1 \exists_{\underline{I}_2^C} \underline{i}_2 \left( \alpha_k^{\neq} \wedge \beta_k \wedge \gamma_{\beta_k} \right) \text{ where } \alpha_k^{\neq} := \alpha_k \wedge (t_1 \neq t_2).$$

It is easy to verify that the formulas  $\tau_k$  and  $\tau_k^= \vee \tau_k^{\neq}$  are equivalent. By continuing the rewriting recursively,  $\tau$  can be transformed into a disjunction of formulas with differentiated accesses to primed parameters.

For a symbol  $I' \in \mathcal{I}'$ , there is exactly one conjunct in  $\tau_k$  in which I' appears in the equality, and it is one of  $I' = I \cup \{t_k\}_k$ ,  $I' = I \setminus \{t_k\}_k$ , or I' = I. In all three cases, value of I' is a function of the value of I and some terms over  $(\mathcal{I}, \mathcal{V})$ , and therefore the conjunct can be rewritten as  $\forall j \ (j \in I' \leftrightarrow Update_I(j))$  where  $Update_I$  is a term of sort bool over  $(\mathcal{I}, \mathcal{V})$  and a free variable. For example, for the first case we have  $Update_I(j) = (j \in I \lor \bigvee_k (j = t_k))$ . The conjuncts in  $\tau_k$  of the form  $t \in I'$  can be rewritten as  $Update_I(t)$ . From  $\tau_k$  we obtain  $\tau_k'$  by

performing the above rewriting of conjuncts which contain I', for all  $I' \in \mathcal{I}'$ . It

For a symbol  $V' \in \mathcal{V}'$ , the set of conjuncts in the  $\tau_k'$  in which V' occurs is either equal to  $\{V'[t_k] = e_k : k = 1, \ldots, n\} \cup \{\forall_{I'_{V'}} j ((\bigwedge_{k=1}^n (j \neq t_k)) \to V'[j] = V[j])\}$ where  $t_k$  are differentiated, or to  $\{\forall_{I'_{V'}} j \ V'[j] = e_j\}$ . In both cases, the set of conjuncts can be rewritten as  $\forall j \ (V'[j] = Update_V(j))$ , where  $Update_V$  is a term of sort  $sort_{V'}$ : in the first case.

$$Update_V(j) := \text{if } j = t_1 \text{ then } e_1 \text{ else if } \dots \text{ else if } j = t_n \text{ then } e_n$$

else if  $Update_{I_V}(j)$  then  $V[j]$  else  $d_{\mathtt{sort}_{V'}}$

and in the second case  $Update_V(j) := \text{if } Update_{I_V}(j) \text{ then } V[j] \text{ else } d_{\mathtt{sort}_{V'}}$ . Formula  $\tau''_k$  is obtained from  $\tau'_k$  by performing the above rewrites for every  $V' \in \mathcal{V}'$ . It is easy to verify that  $\tau''_k$  and  $\tau'_k$  are equivalent.

From the invariant formula  $\kappa$  we obtain the next-state invariant  $\kappa'$  by first distributing set membership operator over the set operations (e.g. transforming  $t \in I \cup J$  to  $t \in I \lor t \in J$ ), and then replacing, for all  $I \in \mathcal{I}$ , each term of the form  $t \in I$  with the term  $Update_I(t)$ , and replacing, for all  $V \in \mathcal{V}$ , each term of the form V[t] with the term  $Update_V(t)$ . Analogously, from the formula  $\rho_{src}$ and component guards  $\psi_P, P \in \mathcal{P}$  we obtain their next-state versions  $\rho'_{src}$  and  $\psi_P', P \in \mathcal{P}$  by performing the same transformations.  $Reconf_k$  is set to

$$\tau_{k}^{"A} \wedge \kappa'^{A} \wedge$$

$$\forall j \left( a'_{P_{src}}[j] = \left( Update_{I_{P_{src}}}(j)^{A} \wedge \psi'_{P_{src}}(j/x)^{A} \wedge \left( a_{P_{src}}[j] \vee \rho'_{src}(j/x)^{A} \right) \right) \right)$$

$$\wedge \bigwedge_{P \in \mathcal{P} \setminus \{P_{src}\}} \forall j \left( a'_{P}[j] = \left( Update_{I_{P}}(j)^{A} \wedge \psi'_{P}(j/x)^{A} \wedge a_{P}[j] \right) \right).$$

(8)

Here the last conjunct updates the information taint for all components, by setting it to true iff the component is present in the next state and it is currently tainted. The third conjunct performs the same update for source components, taking care to also taint the source components which satisfy the next-state source condition  $\rho'_{src}$ .

Finally, the unsafe formula U is set to

$$\exists i \left( a_{I_{P_{dst}}}[i] \wedge \psi_{P_{dst}}(i/x)^{\mathcal{A}} \wedge \rho_{dst}(i/x)^{\mathcal{A}} \wedge a_{P_{dst}}[i] \right), \tag{9}$$

modeling the set of states in which there exists a destination component with index i which satisfies the destination condition  $\rho_{dst}$  and is tainted.

The following theorems state that the information flow problem can be reduced to the array-based safety problem, using the above translation. The detailed proofs can be found in the extended version of the paper at https://es. fbk.eu/people/stojic/papers/fm18.

**Theorem 1.** Problem (S, U), S = (a, Init, Tr), which is obtained by translation from an arbitrary information flow problem, where a is given by (4), Init is given by (5), Tr is given by (6), (7), (8), and U is given by (9), is an array-based safety problem.

The proof amounts to the inspection of the obtained formulas, to confirm that they are indeed in the required fragment.

**Theorem 2.** Let  $DIFP = (D, P_{src}, \rho_{src}, P_{dst}, \rho_{dst})$  be an arbitrary instance of the dynamic information flow problem, and ASP = (S, U) the array-based safety problem obtained by translation from DIFP. There is an information flow witness trace for DIFP if and only if ASP is unsafe.

The proof involves constructing, for an information flow witness trace for DIFP, a counterexample (unsafe) trace of the problem ASP, and vice-versa.

**Decidability.** The dynamic information flow problem is undecidable in general (it is straightforward to model Minsky 2-counter machines [28]), but it is decidable under certain assumptions inherited from the array-based transition systems (see the remark on decidability at the end of Sect. 5.1).

#### 6 Experimental Evaluation

#### 6.1 Setup

**Back-End Solver.** We use MCMT [4] version 2.5.2 to solve array-based safety problems. MCMT is a model checker for array-based systems, based on the SMT solver Yices<sup>1</sup>. We run MCMT with the default settings. The time-out for testing is set to 1000 seconds.

Translation Implementation. We have implemented in C the translation from the extended version of AADL to the input language for MCMT using the parser generator GNU Bison. The input language of MCMT is low level and as such is not suitable for manual modeling of anything but the simplest examples, being instead intended as a target language for automatic generation from specifications written in a higher level language [17]. The translation follows the same outline as its theoretical description in Sect. 5.2, but is more complicated due to the specific features, limitations and idiosyncracies of the target MCMT input language. In particular, the more constraining limitations of MCMT, in addition to the theoretical restrictions on formulas from Sect. 5.1, are:

- The initial formula can contain at most two universally quantified variables.

- The transitions can contain at most two existentially quantified variables.

- The maximum number of transitions (the disjuncts in the transition formula) is 50.

- The unsafe formula can contain at most four existentially quantified variables.

- A term can contain at most ten index variables.

Our translator inherits the above restrictions on the formulas specified in the extended AADL model. While these restrictions do not severely limit the expressivity of the language, the limitation on the maximum number of transitions

<sup>1</sup> http://yices.csl.sri.com/.

limits the size of the examples that can be handled by the present version of the tool.

**Hardware.** We have used a desktop PC based on an Intel<sup>®</sup> Core<sup>TM</sup> i7 CPU 870 clocked at 2.93GHz, with 8 GB of main memory and running Ubuntu 14.04.5 LTS.

**Distribution Tarball.** The translator, tested models, scripts which automatically perform the translation from extended AADL to MCMT input language and run MCMT, as well as setup and usage instructions can be found at https://es.fbk.eu/people/stojic/papers/fm18/.

#### 6.2 Benchmarks and Results

In the following diagrams, arrows between (sets of) components represent connections from all components in the source set to all components in the destination set, unless further restricted in the model description. All sets of components are dynamic, allowing addition/removal of components.

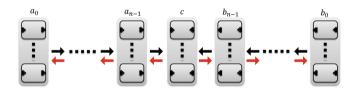

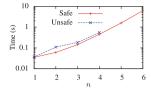

Converging Model. This model contains 2n + 1 sets of components  $a_0, \ldots, a_{n-1}, b_0, \ldots, b_{n-1}, c$ , with the connections shown as black arrows in Fig. 3. There are also connections between all pairs of components in the same set. We test for information flow from the set  $a_{\lfloor n/2 \rfloor}$  to the set  $b_0$ . The unsafe model in addition contains the connections shown as red arrows. Results for the model are in Fig. 7. We hit the MCMT limitation on the number of transitions (see Sect. 6.1) for n = 7 for the safe model, and for n = 5 for the unsafe model. Number of calls made by MCMT to the underlying SMT solver ranges from 211 (safe, n = 1) to 29907 (safe, n = 6).

Fig. 3. Converging model (Color figure online)

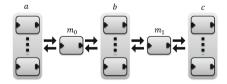

Messenger Model. In this model, for n=1 there are two sets of components, a and b, and a singleton component  $m_0$ .  $m_0$  models a messenger which is intended to allow components within the same set to communicate;  $m_0$  can connect in turn to any single component in a or in b, but not at the same time. We test for infor-

Fig. 4. Messenger model

mation flow from set a to set b. The system as described is unsafe because  $m_0$

can connect to some a[i], disconnect, and then connect to some b[j], therefore establishing a path for flow of information. The safe model removes such paths by using Boolean parameters to record whether  $m_0$  has previously connected to components in a and b. If it has previously connected to one of these sets, then it is not allowed to connect to the other set before it is scrubbed (which is modeled by removing and re-adding it). For n = 2 (Fig. 4), the system is extended with another set of contents of the statement of the system is extended with another set of contents.

| Model              | n | Time (s) | SMT calls |

|--------------------|---|----------|-----------|

| Messenger (safe)   | 1 | 1.894    | 9370      |

| Messenger (safe)   | 2 | ТО       | -         |

| Messenger (unsafe) |   | 0.240    | 1563      |

| Messenger (unsafe) | 2 | 24.639   | 82648     |

| Messenger (unsafe) | 3 | ТО       | -         |

| Network (safe)     | - | 0.875    | 3327      |

| Network (unsafe)   | - | 0.171    | 1063      |

**Fig. 5.** Messenger and Network models results

system is extended with another set of components c and another messenger  $m_1$  which is shared by b and c, and we check for information flow between a and c. Results are shown in Fig. 5.

**Network Model.** This is the model whose safe version is specified in Fig. 2, while the highlighted parts are omitted in the unsafe version. Results are shown in Fig. 5.

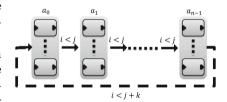

**Sequence Model.** This is a scalable example which models a sequence of n sets of components  $a_0, \ldots, a_{n-1}$  (see Fig. 6 ignoring the dashed loop-back arrow). There is a connection from  $a_x[i]$  to  $a_y[j]$  iff  $(x = y - 1 \lor x = y) \land i < j$ . We check for information flow from  $a_0[0]$  to  $a_{n-1}[n-2]$  in the safe version and from  $a_0[0]$  to  $a_{n-1}[n-1]$  in the unsafe version. The results are shown in Fig. 8. The verification of this model times out for n = 6 (safe) and n = 7 (unsafe). Number of calls to the SMT solver ranges from 116 (unsafe, n = 1) to 60799 (unsafe, n = 6).

Ring Model. This model is the same as the Sequence model, but with additional connections from  $a_{n-1}[i]$  to  $a_0[j]$  (dashed loop-back arrow in Fig. 6) which are present only when i < j + n in the safe version (i < j + n + 1 in the unsafe version), and we check for information flow from  $a_0[0]$  to  $a_{n-1}[n-2]$  in both the safe and unsafe versions. The results are shown

Fig. 6. Sequence and Ring models

in Fig. 9. The verification of this model times out for n=6 (safe) and n=5 (unsafe). Number of calls to the SMT solver ranges from 188 (unsafe, n=1) to 130068 (unsafe, n=4).

Fig. 7. Converging model results

Fig. 8. Sequence model results

Fig. 9. Ring model results

#### 7 Conclusions and Future Work

We propose a new logic-based specification of dynamic architectures where the architectural topology is represented by a set of parameters, while first-order formulas over such parameters define the sets of initial configurations and reconfigurations. The Dynamic Parametrized Architectures so defined can be translated into array-based transition systems, which are amenable to SMT-based model checking. We provide an initial experimental evaluation of various DPAs proving safe and unsafe cases with the MCMT model checker. The results show that the approach is feasible and promising.

As future work, we aim at trying other SMT-based model checkers such as Cubicle [13] and nuXmv [11]. We will investigate new algorithms that directly exploit the topology of the architecture. We will extend the specification to incorporate component behavior and more complex interactions, as well as more general properties. Finally, we are interested in generating certifying proofs for the safe DPAs, possibly exploiting the existing automatic generation of proofs for array-based transition systems [14].

#### References

- European Programme for Critical Infrastructure Protection (EPCIP). http://eur-lex.europa.eu/LexUriServ/LexUriServ.do?uri=COM:2006:0786:FIN:EN:PDF. Accessed 15 Jan 2018

- NIST Cybersecurity Framework. http://www.nist.gov/cyberframework. Accessed 15 Jan 2018

- 3. The CITADEL Project (Critical Infrastructure Protection using Adaptive MILS). http://www.citadel-project.org/. Accessed 15 Jan 2018

- Alberti, F., Ghilardi, S., Sharygina, N.: A framework for the verification of parameterized infinite-state systems. In: CEUR Workshop Proceedings, vol. 1195, pp. 302–308 (2014)

- Allen, R., Douence, R., Garlan, D.: Specifying and analyzing dynamic software architectures. In: Astesiano, E. (ed.) FASE 1998. LNCS, vol. 1382, pp. 21–37. Springer, Heidelberg (1998). https://doi.org/10.1007/BFb0053581

- Basu, A., Bozga, M., Sifakis, J.: Modeling heterogeneous real-time components in BIP. In: Fourth IEEE International Conference on Software Engineering and Formal Methods (SEFM 2006), Pune, India, pp. 3–12, 11–15 September 2006

- Bozga, M., Jaber, M., Maris, N., Sifakis, J.: Modeling dynamic architectures using Dy-BIP. In: Gschwind, T., De Paoli, F., Gruhn, V., Book, M. (eds.) SC 2012. LNCS, vol. 7306, pp. 1–16. Springer, Heidelberg (2012). https://doi.org/10.1007/ 978-3-642-30564-1\_1

- 8. Bradbury, J.S., Cordy, J.R., Dingel, J., Wermelinger, M.: A survey of self-management in dynamic software architecture specifications. In: Proceedings of the 1st ACM SIGSOFT Workshop on Self-Managed Systems WOSS 2004, Newport Beach, California, USA, pp. 28–33, 31 October 1 November 2004

- Bruni, R., Melgratti, H., Montanari, U.: Behaviour, interaction and dynamics. In: Iida, S., Meseguer, J., Ogata, K. (eds.) Specification, Algebra, and Software. LNCS, vol. 8373, pp. 382–401. Springer, Heidelberg (2014). https://doi.org/10.1007/978-3-642-54624-2\_19

- Canal, C., Pimentel, E., Troya, J.M.: Specification and refinement of dynamic software architectures. In: Donohoe, P. (ed.) Software Architecture. ITIFIP, vol. 12, pp. 107–125. Springer, Boston, MA (1999). https://doi.org/10.1007/978-0-387-35563-4\_7

- Cavada, R., Cimatti, A., Dorigatti, M., Griggio, A., Mariotti, A., Micheli, A., Mover, S., Roveri, M., Tonetta, S.: The NuXmv symbolic model checker. In: Biere, A., Bloem, R. (eds.) CAV 2014. LNCS, vol. 8559, pp. 334–342. Springer, Cham (2014). https://doi.org/10.1007/978-3-319-08867-9\_22

- CITADEL Modeling and Specification Languages. Technical report D3.1, Version 2.2, CITADEL Project, April 2018

- Conchon, S., Goel, A., Krstić, S., Mebsout, A., Zaïdi, F.: Cubicle: a parallel SMT-based model checker for parameterized systems. In: Madhusudan, P., Seshia, S.A. (eds.) CAV 2012. LNCS, vol. 7358, pp. 718–724. Springer, Heidelberg (2012). https://doi.org/10.1007/978-3-642-31424-7\_55

- Conchon, S., Mebsout, A., Zaïdi, F.: Certificates for parameterized model checking.

In: Bjørner, N., de Boer, F. (eds.) FM 2015. LNCS, vol. 9109, pp. 126–142. Springer,

Cham (2015). https://doi.org/10.1007/978-3-319-19249-9\_9

- 15. Enderton, H.B.: A Mathematical Introduction to Logic, 2nd edn. Academic Press, Boston (2001)

- Feiler, P.H., Gluch, D.P.: Model-Based Engineering with AADL An Introduction to the SAE Architecture Analysis and Design Language. Addison-Wesley, SEI series in software engineering (2012)

- 17. Ghilardi, S.: MCMT v2.5 User Manual (2014). http://users.mat.unimi.it/users/ghilardi/mcmt/UM\_MCMT\_2.5.pdf. Accessed 15 Jan 2018

- Ghilardi, S., Ranise, S.: Backward reachability of array-based systems by SMT solving: termination and invariant synthesis. Log. Meth. Comput. Sci. 6(4), 1–48 (2010)

- Ghilardi, S., Ranise, S.: MCMT: a model checker modulo theories. In: Giesl, J., Hähnle, R. (eds.) IJCAR 2010. LNCS (LNAI), vol. 6173, pp. 22–29. Springer, Heidelberg (2010). https://doi.org/10.1007/978-3-642-14203-1\_3

- Goguen, J.A., Meseguer, J.: Security policies and security models. In: 1982 IEEE Symposium on Security and Privacy, Oakland, CA, USA, pp. 11–20, 26–28 April 1982

- Hirsch, D., Inverardi, P., Montanari, U.: Reconfiguration of software architecture styles with name mobility. In: Porto, A., Roman, G.-C. (eds.) COORDINATION 2000. LNCS, vol. 1906, pp. 148–163. Springer, Heidelberg (2000). https://doi.org/ 10.1007/3-540-45263-X\_10

- 22. König, B., Kozioura, V.: Towards the verification of attributed graph transformation systems. In: Ehrig, H., Heckel, R., Rozenberg, G., Taentzer, G. (eds.) ICGT 2008. LNCS, vol. 5214, pp. 305–320. Springer, Heidelberg (2008). https://doi.org/10.1007/978-3-540-87405-8\_21

- Konnov, I.V., Kotek, T., Wang, Q., Veith, H., Bliudze, S., Sifakis, J.: Parameterized systems in BIP: design and model checking. In: 27th International Conference on Concurrency Theory CONCUR 2016, Québec City, Canada, pp. 30:1–30:16, 23–26 August 2016

- Magee, J., Kramer, J.: Dynamic structure in software architectures. In: SIGSOFT 1996 Proceedings of the Fourth ACM SIGSOFT Symposium on Foundations of Software Engineering, San Francisco, California, USA, pp. 3–14, 16–18 October 1996

- Medvidovic, N., Taylor, R.N.: A classification and comparison framework for software architecture description languages. IEEE Trans. Softw. Eng. 26(1), 70–93 (2000)

- Métayer, D.L.: Describing software architecture styles using graph grammars. IEEE Trans. Softw. Eng. 24(7), 521–533 (1998)

- 27. Milner, R., Parrow, J., Walker, D.: A Calculus of Mobile Processes I and II. Inf. Comput. **100**(1), 1–77 (1992)

- Minsky, M.L.: Computation: Finite and Infinite Machines. Prentice-Hall Inc, Upper Saddle River (1967)

- 29. Rozenberg, G. (ed.): Handbook of Graph Grammars and Computing by Graph Transformations, Volume 1: Foundations. World Scientific, Singapore (1997)

- 30. Architecture Analysis & Design Language (AADL) (rev. B). SAE Standard AS5506B, International Society of Automotive Engineers, September 2012

- Sifakis, J., Bensalem, S., Bliudze, S., Bozga, M.: A theory agenda for component-based design. In: De Nicola, R., Hennicker, R. (eds.) Software, Services, and Systems. LNCS, vol. 8950, pp. 409–439. Springer, Cham (2015). https://doi.org/10.1007/978-3-319-15545-6\_24

- 32. Wermelinger, M., Fiadeiro, J.L.: Algebraic software architecture reconfiguration. In: Nierstrasz, O., Lemoine, M. (eds.) ESEC/SIGSOFT FSE -1999. LNCS, vol. 1687, pp. 393–409. Springer, Heidelberg (1999). https://doi.org/10.1007/3-540-48166-4\_24

- Xu, H., Zeng, G., Chen, B.: Description and verification of dynamic software architectures for distributed systems. JSW 5(7), 721–728 (2010)

Open Access This chapter is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this chapter are included in the chapter's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the chapter's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.