# **Cross-Layer Resilience Against Soft Errors: Key Insights**

Daniel Mueller-Gritschneder, Eric Cheng, Uzair Sharif, Veit Kleeberger, Pradip Bose, Subhasish Mitra, and Ulf Schlichtmann

# 1 Introduction

Two tasks need to be solved when designing systems for safety-critical application domains: firstly, the safety of the intended functionality (SoiF) must be guaranteed. SoiF focuses on the ability of the system to sense its environment and act safely. Achieving SoiF becomes a highly challenging task due to the rising complexity of various safety-critical applications such as autonomous driving or close robot-human interaction, which may require complex sensor data processing and interpretation. Secondly, and no less important, the system must also always remain or transit into a safe state given the occurrence of random hardware faults. To achieve this requirement, the system must be capable of detecting as well as handling or correcting possible errors. Safety standards such as ISO26262 for road vehicles define thresholds on detection rates for different automotive safety integration levels (ASIL) depending on the severity of a possible system failure, the controllability by the driver, and the nominal usage time of the system. It is commonly understood that safety-critical systems must be designed from the beginning with the required error protection in mind [39] and that for generalpurpose computing systems, error protection is required to achieve dependable computing [19, 21].

E. Cheng · S. Mitra Stanford University, Stanford, CA, USA e-mail: eccheng@stanford.edu; subh@stanford.edu

P. Bose IBM, New York, NY, USA e-mail: pbose@us.ibm.com

U. Sharif · D. Mueller-Gritschneder (⊠) · U. Schlichtmann · V. Kleeberger Infineon Technologies AG, Neubiberg, Germany e-mail: daniel.mueller@tum.de; uzair.sharif@tum.de; ulf.schlichtmann@tum.de

This requirement is becoming increasingly challenging as integrated systems following the continuous trend of Dennard scaling-become more susceptible to fault sources due to smaller transistor dimensions and lower supply voltages. As transistor dimensions scale down the charge stored in memory cells such as SRAM or flip-flops decreases. Soft errors occur due to charge transfers when primary or secondary particles from cosmic radiation hit the silicon [11]. This charge transfer may lead to the corruption of the value stored in the cell. This is referred to as a "soft error" as it does not permanently damage the cell. The vulnerability of cells increases even further with shrinking supply voltage levels or sub-threshold operation. Thus, for the design of safety-critical digital systems, the protection against radiation-induced soft errors is a crucial factor to avoid unacceptable risks to life or property.

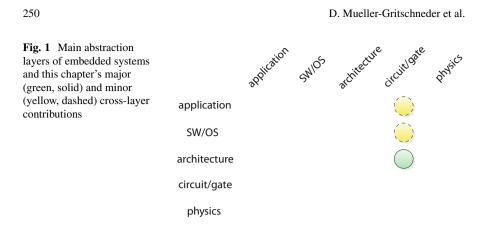

This reality motivates methods that aim to increase the resilience of safetycritical systems against radiation-induced soft errors in digital hardware. Common protection techniques against soft errors either harden the memory elements to reduce the probability of soft errors occurring or add redundancy at different layers of the design (circuit, logic, architecture, OS/schedule, compiler, software, algorithm) to detect data corruptions, which can subsequently be handled or corrected by appropriate error handlers or recovery methods. Each protection technique adds overheads and, hence, additional costs. Especially, adding protection techniques on top of each other at all layers-not considering combined effects-may lead to inefficient protection and non-required redundancy. The idea of cross-layer resiliency is to systematically combine protection techniques that work collaboratively across the layers of the system stack. The target is to find more efficient protection schemes with the same soft error resilience at a lower cost than can be reached by ignoring cross-layer effects. For this, cross-layer techniques combine accurate evaluation of the soft error resilience with a broad cross-layer exploration of different combinations of protection techniques. This work demonstrates how to apply the cross-layer resilience principle on custom processors, fixed-hardware processors, accelerators, and SRAM memories with a focus on soft errors. Its main focus spans from application to circuit layer as illustrated in Fig 1. These works lead to a range of key insights, important for realizing cross-layer soft error resilience for a wide range of system components:

- accurate resilience evaluation is key, e.g., simulation-based fault injection at the flip-flop level is required to accurately evaluate soft errors in logic,

- multi-level/mixed-mode simulation enables very efficient resilience evaluation using fault injection,

- cross-layer resilience exploration must be customized for the component under consideration such as a custom processor, uncore components, third-party processor, accelerator, or SRAM,

- embedded applications such as control algorithms have inherent fault resilience that can be exploited,

- circuit-level techniques are crucial for cost-effective error resilience solutions, and

- existing architecture- and software-level techniques for hardware error resilience are generally expensive or provide too little resilience when implemented using their low-cost variants.

The chapter is structured as follows: first, evaluation methods using fault injection are covered, followed by cross-layer resilience exploration. Finally, experimental results are provided.

### 2 Evaluation of Soft Error Resilience Using Fault Injection

Fault injection is commonly used to evaluate soft error resilience. Radiation-induced soft errors can be modeled as bit flips [23], which are injected into the system's memory cells such as flip-flops and SRAM cells. There exists a wide range of fault injection methods, which will briefly be discussed in the following.

### 2.1 Overview on Fault Injection Methods

*Hardware-based fault injection* injects the fault in a hardware prototype of the system. For example, a radiation beam experiment can be used to provoke faults in an ASIC. This is a very expensive experimental setup, e.g., requiring a radiation source such as used in [1]. The chip hardware can also be synthesized to an FPGA, which is instrumented with additional logic to change bit values in the memory, flip-flops, or combinational paths of the logic to inject a fault using *emulation-based fault injection* [10, 13]. Embedded processors have a debug port to read out their internal states such as architectural registers. These debug ports often also enable the ability to change the internal states. This can be used to inject a fault in the processor using *debug-based fault injection* [15, 41]. Software running on the system can be used to mimic faults in *software-implemented fault injection*, e.g., as

presented in [26, 30, 44]. The compiler can be used to instrument the binary with fault injection code, for *compiler-based fault injection*, e.g., implemented in [18]. *Simulation-based fault injection* injects faults in a simulation model of the system. It is commonly applied to investigate the error resilience of the system and, hence, is the primary focus of this work.

### 2.2 Simulation-Based Fault Injection

Simulation-based fault injection provides very good properties in terms of parallelism, observability, and early availability during the design. Simulation-based fault injection can be realized at different levels of abstraction. For gate-level fault injection, the fault is injected into the gate Netlist of the system obtained after logic synthesis. For *flip-flop-level fault injection*, the fault is injected into the RTL implementation of the system. The fault impact is simulated using logic simulation, e.g., as used in [12, 46]. In architectural-level fault injection, the fault is injected either in a micro-architectural simulator or Instruction Set Simulator (ISS). Microarchitectural simulators such as Gem5 [3] simulate all architectural and some microarchitectural states such as pipeline registers of the processor, e.g., as presented in [25], but usually do not accurately model the processor's control logic. An ISS usually only simulates the architectural registers, but not any micro-architectural registers. ISSs are used for fault injection in [14, 24, 35]. In software-level fault injection, the fault is directly injected into a variable of the executing program. The software can then be executed to determine the impact of the corrupted variable on the program outputs.

A key insight of previous work was that the evaluation of the soft error resilience of logic circuits such as processor pipelines requires flip-flop-level fault injection, e.g., using the RTL model [9, 38]. Architectural-level and software-level fault injection may not yield accurate results as they do not include all details of the logic implementation as will also be shown in the results in Sect. 4.1. In contrast, soft errors in memories such as SRAM may be investigated at architectural level, which models memory arrays in a bit-accurate fashion.

### 2.3 Fast Fault Injection for Processor Cores

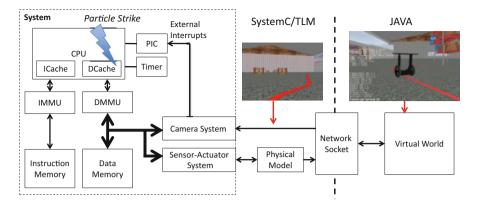

A good estimation of soft error resilience requires simulating a large amount of fault injection scenarios. This may become computationally infeasible when longrunning workloads are evaluated, e.g., for embedded applications. Such long test cases arise in many applications. For example, in order to evaluate the impact of a soft error on a robotic control application, the control behavior needs to simulate several seconds real time, possibly simulating several billion cycles of the digital hardware. An efficient analysis method called ETISS-ML for evaluating the resilience against soft errors in the logic of a processor sub-system is presented in [37, 38]. A typical processor sub-system of a micro-controller consists of the pipeline, control path, exception unit, timer, and interrupt controller. ETISS-ML is especially efficient for evaluating the impact of soft errors for long software test cases.

#### 2.3.1 Multi-Level Fault Injection

ETISS-ML reduces the computational cost of each fault injection run by applying a multi-level simulation approach, which was also applied in other fault injection environments such as [16, 31, 45]. The key idea is to switch abstraction of the processor model during the fault injection run and to minimize the number of cycles simulated at flip-flop level. For this, an ISS is used in addition to the RTL model of the processor at flip-flop level.

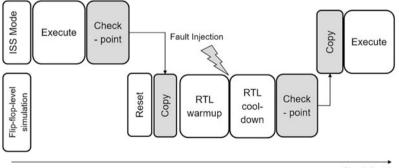

The proposed multi-level flow is illustrated in Fig. 2. First the system is booted in ISS mode. This allows to quickly simulate close to the point of the fault injection, at which point, the simulation switches to flip-flop-level. During the RTL warmup phase, instructions are executed to fill the unknown micro-architectural states of the processor sub-system. This is required as the architectural registers are not visible to the ISS simulation. After this RTL warmup, the fault is injected as a bit flip. During the following RTL cool-down phase, the propagation of the fault is tracked. Once the initial impact of the fault propagates out of the processor's micro-architecture or is masked, the simulation can switch back to ISS mode. ETISS-ML reaches between 40x-100x speedup for embedded applications compared to pure flip-flop-level fault injection while providing the same accuracy [37, 38].

Both the switch from ISS mode to RTL mode as well as the switch from RTL to ISS mode require careful consideration. If a simulation artifact (wrong behavior) is produced by the switching process, it may be wrongly classified as fault impact.

Simulation time

Fig. 2 Multi-level simulation flow of ETISS-ML

Next, we will detail the state of the art approach used by ETISS-ML to solve these challenges.

#### 2.3.2 Switch from ISS Mode to Flip-Flop-Level Simulation

As shown in Fig. 2, a checkpoint is taken from the ISS to initialize the state in the RTL processor model. This checkpoint only includes the architectural states, the micro-architectural states such as pipeline registers are unknown. In the RTL warmup phase instructions are executed to fill up these micro-architectural states. In order to verify the RTL warmup phase, a (0, 1, X) logic simulation can be applied [37]. All micro-architectural states are initialized to X (unknown), while the values of architectural states are copied from the checkpoint. Additionally, the inputs loaded from external devices such as instruction and data memories as well as peripheral devices are also known from ISS simulation. Naturally, one expects that the micro-architectural states take known values after a certain number of instructions are executed. A key insight here was that this is not the case. Several state machines in the control path and bus interfaces of the processor would start from an unknown state. Hence, all following states remain unknown. One must assume initial states for the RTL state machines, e.g., the reset state. Then one can observe the removal of X values in the RTL model to derive a suitable RTL warmup length for a given processor architecture.

#### 2.3.3 Switch from Flip-Flop-Level Simulation Back to ISS Mode

After the fault has been injected into the RTL model, the flip-flop level simulation is continued during the RTL cool-down phase. When switching back to ISS mode, all micro-architectural states are lost, as only the architectural states are copied over. Hence, one must ensure that one does not lose information about the impact of the fault as this would result in an incorrect estimation. One can take a fixed, very long cool-down phase as proposed in [45]. Yet, this leads to inefficient simulation as many cycles need to be evaluated at flip-flop level. Additionally, one does not gain information as to whether or not the soft error impact is still present in the micro-architectural states. This can be improved by simulating two copies of the RTL model, a faulty processor model and a tracking model [38]. The external state of memories, peripherals, or the environment is not duplicated. The soft error is only injected into the faulty model. In contrast, the tracking model simulates without the error. Writes to the external devices (memories, peripherals) are only committed from the faulty model. Reads from those devices are supplied to both models. Hence, when the soft error is not masked, it may propagate from the faulty model to the architectural state, external memories and devices and, then, be read back to the faulty and tracking model. Whenever both models have the same micro-architectural state, one can be sure that the error either has been masked or has propagated fully to the architectural state or external devices and memories. At this point the simulation can switch to ISS mode as the architectural state and external devices and memories are also modeled at ISS level. It turns out that some errors never propagate out of the micro-architectural states, e.g., because a configuration is corrupted that is never rewritten by the software. In this case the switch back to ISS mode is not possible as it would cause inaccuracies, e.g., as would be observed with a fixed cool-down length.

### 2.4 Fast Fault Injection in Uncore Components

In addition to errors impacting processor cores, it is equally important to consider the impact of errors in uncore components, such as cache, memory, and I/O controllers, as well. In SoCs, uncore components are comparable to processor cores in terms of overall chip area and power [33], and can have significant impact on the overall system reliability [8].

Mixed-mode simulation platforms are effective for studying the system-level impact and behavior of soft errors in uncore components as well. As presented in [8], such a platform would achieve a  $20,000 \times$  speedup over RTL-only injection while ensuring accurate modeling of soft errors. Full-length applications benchmarks can be analyzed by simulating processor cores and uncore components using an instruction-set simulator in an accelerated mode. At the time of injection, the simulation platform would then enter a co-simulation mode, where the target uncore component is simulated using accurate RTL simulation. Once co-simulation is no longer needed (i.e., all states can be mapped back to high-level models), the accelerated mode can resume, allowing application benchmarks to be run to completion.

## 2.5 Fast Fault Injection for SRAM Memories Using Mixture Importance Sampling

Memories such as on-chip SRAM or caches are already modeled bit-accurately at micro-architectural and instruction-level. Hence, for the evaluation of soft errors in memories, fault injection into faster instruction-level models is possible. Yet, modern SRAMs are very dense such that the probability of multi-bit upsets (MBUs) due to soft errors is not negligible. For MBU fault models, straightforward Monte Carlo simulation requires a large sample size in the range of millions of sample elements to obtain sufficient confidence bounds.

To address this challenge one can apply mixture importance sampling to connect a technology-level fault model with a system-level fault simulation [29]. This propagation of low-level information to the system level is motivated by the Resilience Articulation Point (RAP) approach proposed in [23]. The key idea behind

RAP is that errors in the system should be modeled by probabilistic functions describing MBU's bit flip probabilities including spatial and temporal correlations. Thus, the impact of errors in the system can be evaluated, while maintaining a direct connection to their root causes at the technology level. The sample size to estimate the resilience of the system to soft errors in SRAMs can be massively reduced by guiding the Monte Carlo simulation to important areas. As an illustrative example, we assume that the SRAM is used to realize a data cache with 1-bit parity protection. MBUs that alter an odd number of bits in a cache line are detected by the parity checks and may be corrected by loading the correct value from the next level of memory. MBUs that alter an even number of bits in a cache line remain undetected and may cause silent data corruption. Additionally, MBUs may perturb several neighboring cache lines due to different MBU mechanisms. This can lead to mixed cases of recoverable errors and silent data corruption. For a cache with one bit parity protection, MBUs with even number (2, 4, ...) of bits in one cache line are critical as they may provoke silent data corruption (SDC). The sampling strategy can be biased towards these MBUs by mixture important sampling, which speeds up the resilience evaluation significantly. It is shown that results with high confidence can be obtained with sample sizes in the thousands instead of millions [29]. The resulting fast evaluation enables the efficient exploration of the most efficient crosslayer protection mechanisms for the SRAM memory for an overall optimized reliable system.

# **3** Cross-Layer Exploration of Soft Error Resilience Techniques

Most safety-critical systems already employ protection techniques against soft errors at different layers. Yet often, possible combinations are not systematically explored and evaluated to identify a low-cost solution. This may result in inefficient redundancy and hardening, e.g., that certain types of faults are detected by multiple techniques at different layers, or certain redundancy is not required, as the circuit is adequately protected (e.g., by circuit-hardening techniques).

In this section several approaches are outlined that focus on cross-layer exploration for finding low-cost soft error protection:

- the CLEAR approach can generate resilience solutions for custom processors with selective hardening in combination with architectural and software-level protection schemes.

- Using a similar approach, on-chip SRAM can be protected with a combination of hardening and error detection codes.

- For third-party processors, hardening and hardware redundancy are not an option. Hence, we show how application resilience can be used in combination with software-level protection to achieve cross-layer resilience.

#### Cross-Layer Resilience Against Soft Errors: Key Insights

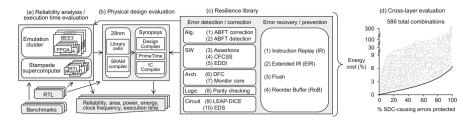

**Fig. 3** CLEAR framework: (a) BEE3 emulation cluster/Stampede supercomputer injects over 9 million errors into two diverse processor architectures running 18 full-length application benchmarks. (b) Accurate physical design evaluation accounts for resilience overheads. (c) Comprehensive resilience library consisting of ten error detection/correction techniques + four hardware error recovery techniques. (d) Example illustrating thorough exploration of 586 cross-layer combinations with varying energy costs vs. percentage of SDC-causing errors protected

• Finally, we also discuss how accelerators can be protected with cross-layer resilience techniques.

#### 3.1 CLEAR: Cross-Layer Resilience for Custom Processors

CLEAR (Cross-Layer Exploration for Architecting Resilience) is a first of its kind framework to address the challenge of designing robust digital systems: given a set of resilience techniques at various abstraction layers (circuit, logic, architecture, software, algorithm), how does one protect a given design from radiation-induced soft errors using (perhaps) a combination of these techniques, across multiple abstraction layers, such that overall soft error resilience targets are met at minimal costs (energy, power, execution time, area)?

CLEAR has broad applicability and is effective across a wide range of diverse hardware designs ranging from in-order (InO-core) and out-of-order (OoO-core) processor cores to uncore components such as cache controllers and memory controllers to domain-specific hardware accelerators. CLEAR provides the ability to perform extensive explorations of cross-layer combinations across a rich library of resilience techniques and error sources.

Figure 3 gives an overview of the CLEAR framework. Individual components are described briefly in the following:

#### 3.1.1 Reliability Analysis

While the CLEAR framework provides the ability to analyze the reliability of designs, this component does not comprise the entirety of the framework. The modularity of the CLEAR framework enables one to make use of any number of the accurate fault-injection simulation components described in detail in Sect. 2.2

to perform reliability analysis. The analysis considered in this chapter encompasses both Silent Data Corruption (SDC) and Detected but Uncorrected Errors (DUE).

#### 3.1.2 Execution Time Evaluation

Execution time is measured using FPGA emulation and RTL simulation. Applications are run to completion to accurately capture the execution time of an unprotected design. For resilience techniques at the circuit and logic levels, CLEAR ensures that modifications incorporating such resilience techniques will maintain the same clock speed as the unprotected design. For resilience techniques at the architecture, software, and algorithm levels, the error-free execution time impact is also reported.

#### 3.1.3 Physical Design Evaluation

To accurately capture overheads associated with implementing resilience techniques, it is crucial to have a means for running an entire physical design flow to properly evaluate the resulting designs. To that end, the Synopsys design tools (Design Compiler, IC compiler, PrimeTime, and PrimePower) with a commercial 28nm technology library (with corresponding SRAM compiler) are used to perform synthesis, place-and-route, and power analysis. Synthesis and place-and-route (SP&R) is run for all configurations of the design (before and after adding resilience techniques) to ensure all constraints of the original design (e.g., timing and physical design) are met for the resilient designs as well.

### 3.1.4 Resilience Library

For processor cores, ten error detection and correction techniques together with four hardware error recovery techniques are carefully chosen for analysis. In the context of soft error resilience, error detection and correction techniques include: Algorithm Based Fault Tolerance (ABFT) correction, ABFT detection, Software assertions, Control Flow Checking by Software Signatures (CFCSS), Error Detection by Duplicated Instructions (EDDI), Data Flow Checking (DFC), Monitor cores, Parity checking, flip-flop hardening using LEAP-DICE, and Error Detection Sequential (EDS). These techniques largely cover the space of existing soft error resilience technique when used as a standalone solution (e.g., an error detection/correction technique by itself or, optionally, in conjunction with a recovery technique) are presented in Table 1. Additionally, four micro-architectural recovery techniques are included: Instruction Replay (IR), Extended IR (EIR), flush, and Reorder Buffer (RoB) recovery. Refer to [7] for an in-depth discussion of specific techniques and their optimizations, including a detailed discussion of Table 1.

| ayer   | Layer Technique        |     | Area<br>cost | Power<br>cost | Energy<br>cost | Exec. time impact | Avg. SDC<br>improve          | Avg. DUE<br>improve          | False<br>positive | Detection<br>latency | ア    |

|--------|------------------------|-----|--------------|---------------|----------------|-------------------|------------------------------|------------------------------|-------------------|----------------------|------|

| ircuit | Circuit LEAP-DICE      | InO | 0-9.3%       | 0-22.4%       | 0-22.4%        | 0%0               | $1 \times -5000 \times$      | $1 \times -5000 \times$      | 0%0               | N/A                  | -    |

|        | (no additional         | 000 | 0-6.5%       | 0-9.4%        | 0-9.4%         |                   |                              |                              |                   |                      |      |

|        | recovery needed)       |     |              |               |                |                   |                              |                              |                   |                      |      |

|        | EDS (without           | InO | 0-10.7%      | 0-22.9%       | 0-22.9%        | 0%0               | $1 \times ->100,000 \times$  | $0.1 \times -1 \times$       | 0%0               | 1 cycle              | -    |

|        | recovery               | 000 | 0-12.2%      | 0-11.5%       | 0-11.5%        |                   |                              |                              |                   |                      |      |

|        | unconstrained)         |     |              |               |                |                   |                              |                              |                   |                      |      |

|        | EDS (with IR           | InO | 0-16.7%      | 0-43.9%       | 0-43.9%        | 0%0               | $1 \times -> 100,000 \times$ | $1 \times -> 100,000 \times$ | 0%0               | 1 cycle              | 1.4  |

|        | recovery)              | 000 | 0-12.3%      | 0-11.6%       | 0-11.6%        |                   |                              |                              |                   |                      | 1.06 |

| Logic  | Parity (without        | InO | 0-10.9%      | 0-23.1%       | 0-23.1%        | 0%0               | $1 \times ->100,000 \times$  | $0.1 \times -1 \times$       | 0%0               | 1 cycle              | -    |

|        | recovery               | 000 | 0-14.1%      | 0-13.6%       | 0-13.6%        |                   |                              |                              |                   |                      |      |

|        | unconstrained)         |     |              |               |                |                   |                              |                              |                   |                      |      |

|        | Parity (with           | InO | 0-26.9%      | 0-44%         | 0-44%          | 0%0               | $1 \times ->100,000 \times$  | $1 \times ->100,000 \times$  | 0%                | 1 cycle              | 1.4  |

|        | IR recovery)           | 000 | 0-14.2%      | 0-13.7%       | 0-13.7%        |                   |                              |                              |                   |                      | 1.06 |

| Arch.  | DFC (without           | InO | 3%           | 1%            | 7.3%           | 6.2%              | $1.2 \times$                 | $0.5 \times$                 | 0%0               | 15 cycles            | 1.28 |

|        | recovery               | 000 | 0.2%         | 0.1%          | 7.2%           | 7.1%              |                              |                              |                   |                      | 1.09 |

|        | unconstrained)         |     |              |               |                |                   |                              |                              |                   |                      |      |

|        | DFC (with              | InO | 37%          | 33%           | 41.2%          | 6.2%              | $1.2 \times$                 | 1.4×                         | 0%0               | 15 cycles            | 1.48 |

|        | EIR recovery)          | 000 | 0.4%         | 0.2%          | 7.3%           | 7.1%              |                              |                              |                   |                      | 1.14 |

|        | Monitor core           | 000 | 9%6          | 16.3%         | 16.3%          | 0%0               | 19×                          | 15×                          | 0%0               | 128 cycles           | 1.38 |

|        | (with ROD<br>recoverv) |     |              |               |                |                   |                              |                              |                   |                      |      |

| solutic      |

|--------------|

| standalone   |

| as a         |

| improvements |

| Ч            |

| costs and    |

| techniques:  |

| resilience   |

| Individual   |

| -            |

| Layer    | Technique                                                  |     | Area | Power<br>cost | Energy<br>cost | Exec. time impact | Avg. SDC<br>improve | Avg. DUE<br>improve |     | Detection<br>latency | 2    |

|----------|------------------------------------------------------------|-----|------|---------------|----------------|-------------------|---------------------|---------------------|-----|----------------------|------|

| Software | Software Software assertions<br>for general-               | Oul | %0   | %0            | 15.6%          | 15.6%             | $1.5 \times$        | 0.6×                |     | 9.3M<br>cycles       | 1.16 |

|          | purpose processors<br>(without recovery—<br>unconstrained) |     |      |               |                |                   |                     |                     |     |                      |      |

|          | CFCSS (without                                             | InO | 0%0  | 0%0           | 40.6%          | 40.6%             | $1.5 \times$        | $0.5 \times$        | 0%  | 6.2M                 | 1.41 |

|          | recovery—<br>unconstrained)                                |     |      |               |                |                   |                     |                     |     | cycles               |      |

|          | EDDI (without                                              | InO | 0%   | 0%0           | 110%           | 110%              | 37.8×               | $0.3 \times$        | 0%0 | 287K                 | 2.1  |

|          | recovery-                                                  |     |      |               |                |                   |                     |                     |     | cycles               |      |

|          | ulicolisu allicu )                                         |     |      |               |                |                   |                     |                     |     |                      |      |

| Alg.     | ABFT correction                                            | InO | 0%0  | 0%            | 1.4%           | 1.4%              | $4.3 \times$        | $1.2 \times$        | 0%  | N/A                  | 1.01 |

|          | (no additional                                             | 000 |      |               |                |                   |                     |                     |     |                      |      |

|          | recovery needed)                                           |     |      |               |                |                   |                     |                     |     |                      |      |

|          | ABFT detection                                             | InO | 0%0  | 0%            | 24%            | 1-56.9%           | $3.5 \times$        | $0.5 \times$        | 0%  | 9.6M                 | 1.24 |

|          | (without recovery                                          | 000 |      |               |                |                   |                     |                     |     | cycles               |      |

|          | unconstrained)                                             |     |      |               |                |                   |                     |                     |     |                      |      |

Table 1 (continued)

#### 3.1.5 Exploration

CLEAR approaches cross-layer exploration using a top-down approach: resilience techniques from upper layers of the resilience stack (e.g., algorithm-level techniques) are applied before incrementally moving to lower layers (e.g., circuit-level techniques). This approach helps generate cost-effective solutions that leverage effective interactions between techniques across layers. In particular, while resilience techniques from the algorithm, software, and architecture layers of the stack generally protect multiple flip-flops, a designer typically has little control over the specific subset of flip-flops that will be protected. Using multiple techniques from these layers can lead to a situation where a given flip-flop may be protected (sometimes unnecessarily) by multiple techniques. Conversely, resilience techniques at the logic and circuit layers offer fine-grained protection since these techniques can be applied selectively to individual flip-flops (i.e., flip-flops not (sufficiently) protected by higher-level techniques).

### 3.2 Resilience Exploration for Custom Accelerators

Domain-specific hardware accelerators will increasingly be integrated into digital systems due to their ability to provide more energy-efficient computation for specific kernels. As a result of their application-specific nature, hardware accelerators have the opportunity to leverage application space constraints when exploring cross-layer resilience (i.e., resilience improvement targets only need to hold over a limited subset of applications). Accelerators also benefit from the ability to create natural checkpoints for recovery by protecting the memory storing the accelerator inputs (e.g., using ECC), allowing for a simple means for re-execution on error detection. Therefore, the cross-layer solutions that provide cost-effective resilience may differ from those of processor cores and warrant further exploration.

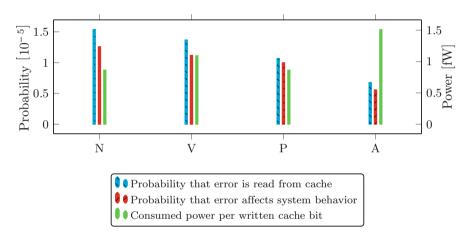

# 3.3 Cross-Layer Resilience for Exploration for SRAM Memories

In [28], a cross-layer approach for soft error resilience was applied to SRAM data caches. Again, a systematic exploration requires having a good evaluation of the cost and efficiency of the applied protection mechanisms. In this study, the available protection mechanisms were the following: at circuit level, either (1) the supply voltage could be raised by 10% or (2) the SRAM cells could be hardened by doubling the area. At the architectural level, (3) 1-bit parity could be introduced in the cache lines. The circuit-level hardening techniques require parameterizing the statistical MBU fault model introduced in Sect. 2.5 considering cell area, supply

voltage and temperature. For each configuration, the fault probabilities for MBU patterns need to be evaluated to obtain a good estimate of soft error probabilities. Additionally, the architecture and workload play a key role in the evaluation as not all soft errors are read from the cache. Here again, architectural-level simulation can be used to simulate the workload using fault injection into a bit-accurate cache model.

## 3.4 Towards Cross-Layer Resiliency for Cyber-Physical Systems (CPS)

In benchmark-type workloads, silent data corruption in a single program output commonly leads to a failure, e.g., an encryption algorithm fails if its encrypted data is corrupted such that it cannot be decrypted. Hence, cross-layer resiliency often targets reducing the rate of silent data corruption.

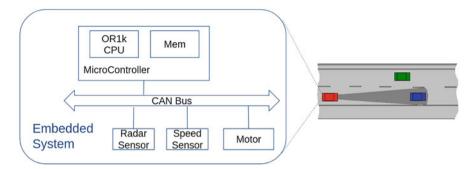

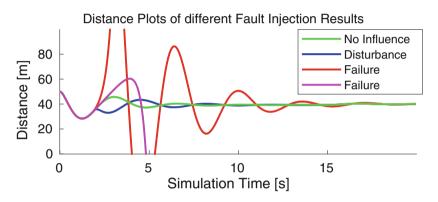

For cyber-physical systems (CPS), however, many workloads can tolerate deviations from the fault-free outcome, e.g., in an embedded control algorithm, noise, e.g., in sensors, is present and considered in the control design. It will treat silent data corruption as yet another noise source, that can, possibly, be tolerated for minor deviations from the correct value. Another effect is that CPS workloads are commonly scheduled as periodic tasks. Often, the outputs of one instance of a certain task are overwritten by the next instance of a task. Hence, a corruption of the output of a single task has an effect only for a certain duration in time. Subsequent task executions might mitigate the effect of silent data corruption before the system behavior becomes critical. For example for control applications, the sampling rate of the controller is often higher than demanded, such that a single corrupted actuation command will not lead to a failure within one control period. Following sensor readouts will show a deviation from the desired control behavior that is corrected by the controller in subsequent control periods.

In order to consider the inherent resilience of CPS workloads, a full system simulation is required. CPS usually form a closed loop with their environment, e.g., actuation will change the physical system behavior, which determines future sensor readouts. Extensive fault injection for obtaining a good resiliency evaluation is enabled by the fast simulation speed of ETISS-ML [38], while RTL level fault injection would be prohibitively slow to evaluate system behavior over a long system-level simulation scenario. ETISS-ML can be integrated into a full-system virtual prototype (VP) that models the system and its physical environment such that error impacts can be classified considering the inherent resilience of CPS workloads. For this, the physical behavior is traced to determine the impact of the error. A major question to be investigated is how this inherent application resilience can be exploited in an efficient way to reduce cost of protection techniques towards cross-layer resilience of CPS.

#### **4** Experimental Results

This section presents results for cross-layer exploration. First, we show results that support our claim that flip-flop level fault injection is required for soft errors in logic. Then we provide the results for cross-layer exploration with CLEAR and ETISS-ML for processors. Finally, we show the results for the cross-layer exploration of protection techniques for the data cache of a control system for a self-balancing robot.

### 4.1 Accuracy of FI at Different Abstraction Levels

For radiation-induced soft errors, flip-flop soft error injection is considered to be highly accurate. Radiation test results confirm that injection of single bit flips into flip-flops closely models soft error behaviors in actual systems [4, 43]. On the other hand, [9] has shown that naïve high-level error injections (e.g., injection of a single-bit error into an architecture register, software-visible register-file, or program variable) can be highly inaccurate.

Accurate fault-injection is crucial for cost-effective application of cross-layer resilience. Inaccurate reliability characterization may lead to over- or underprotection of the system. Overprotection results in wasted cost (e.g., area, power, energy, price) and underprotection may result in unmitigated system failures.

In order to observe the impact of soft errors in the data and control path of a OR1K processor sub-system, the error propagation was tracked to the architecturalvisible states in [38] for four test cases. In total 70k fault injection scenarios were run on each test case. The injection points were micro-architectural FFs in the RTL implementation such as pipeline and control path registers, that are not visible at the architectural level. First all soft errors were identified that had no impact on the architectural state since they were either being masked or latent. On average these were 67.51%.

On architectural level, we inject single bit flip fault scenarios as it is unclear what multi-bit fault scenarios could really happen in HW. These scenarios will cover all single bit flip soft errors in an architectural state as well as any soft error in a micro-architectural state that propagates and corrupts just a single bit of an architectural state. In this case it makes no difference whether we inject the single bit flip in the micro-architectural state or architectural state. Yet, the distribution could be different. We now observe the experimental results as given in Table 2: 25.09% of the micro-architectural faults corrupted a single bit in the architectural state for a single cycle. These faults would be covered by fault injection at architectural level. But 7.40% of the soft errors corrupted several bits of the architectural state or lead to several bit flips in subsequent cycles. Injecting single bit soft errors in architectural states at architectural evel will not cover these micro-architectural fault

| Test case | Masked or latent [%] | Single bit corruption [%] | Multi-bit corruption [%] |

|-----------|----------------------|---------------------------|--------------------------|

| JDCT      | 66.77                | 25.68                     | 7.55                     |

| AES       | 66.36                | 26.13                     | 7.51                     |

| IIR       | 68.88                | 23.83                     | 7.29                     |

| EDGE      | 68.02                | 24.73                     | 7.25                     |

| Average   | 67.51                | 25.09                     | 7.40                     |

Table 2 Impact of single bit flip in micro-arch FFs on architectural processor state

| Table 3         General-purpose processor core | e designs studied |

|------------------------------------------------|-------------------|

|------------------------------------------------|-------------------|

|     | Design     | Description                                                         | Clk. freq. | Error injections | Instructions per cycle |

|-----|------------|---------------------------------------------------------------------|------------|------------------|------------------------|

| InO | LEON3 [17] | Simple,<br>in-order<br>(1250<br>flip-flops)                         | 2.0 GHz    | 5.9 million      | 0.4                    |

| 000 | IVM [46]   | Complex,<br>super-scalar,<br>out-of-order<br>(13,819<br>flip-flops) | 600 MHz    | 3.5 million      | 1.3                    |

scenarios. Hence, one needs to look into RTL fault injection to obtain accurate results for these faults.

### 4.2 Cross-Layer Resilience Exploration with CLEAR

The CLEAR framework is first used to explore a total of 586 cross-layer combinations in the context of general-purpose processor cores. In particular, this extensive exploration consists of over 9 million flip-flop soft error injections into two diverse processor core architectures (Table 3): a simple, in-order SPARC LEON3 core (InO-core) and a complex superscalar out-of-order Alpha IVM core (OoO-core). Evaluation is performed across 18 application benchmarks from the SPECINT2000 [22] and DARPA PERFECT [2] suites.

Several insights resulted from this extensive exploration: accurate flip-flop level injection and layout (i.e., physical design) evaluation reveal many individual techniques provide minimal (less than  $1.5 \times$ ) SDC/DUE improvement (contrary to conclusions reported in the literature that were derived using inaccurate architecture- or software-level injection [20, 36]), have high costs, or both. The consequence of this revelation is that most cross-layer combinations have high cost.

Among the 586 cross-layer combinations explored using CLEAR, a highly promising approach combines selective circuit-level hardening using LEAP-DICE, logic parity, and micro-architectural recovery (flush recovery for InO-cores, reorder

buffer (RoB) recovery for OoO-cores). Thorough error injection using application benchmarks plays a critical role in selecting the flip-flops protected using these techniques.

From Table 4, to achieve a  $50 \times$  SDC improvement, the combination of LEAP-DICE, logic parity, and micro-architectural recovery provides  $1.5 \times$  and  $1.2 \times$  energy savings for the OoO- and InO-cores, respectively, compared to selective circuit hardening using LEAP-DICE. This scenario is shown under "bounded latency recovery." The relative benefits are consistent across benchmarks and over the range of SDC/DUE improvements.

If recovery hardware is not needed (i.e., there exist no recovery latency constraints and errors can be recovered using an external means once detected), minimal (<0.2% energy) savings can be achieved when targeting SDC improvement. This scenario is shown under "unconstrained recovery." However, without recovery hardware, DUEs increase since detected errors are now uncorrectable; thus, no DUE improvement is achievable.

Additional cross-layer combinations spanning circuit, logic, architecture, and software layers are presented in Table 4. In general, most cross-layer combinations are not cost-effective. For general-purpose processors, a cross-layer combination of LEAP-DICE, logic parity, and micro-architectural recovery provides the lowest cost solution for InO- and OoO-cores for all improvements.

#### 4.3 Resilience Exploration for Custom Accelerators

Utilizing a high-level synthesis (HLS) engine from UIUC [5], 12 accelerator designs derived from the PolyBench benchmark suite [42] were evaluated with protection using LEAP-DICE (circuit), logic parity (logic), modulo-3 shadow datapaths (architecture), EDDI (software), and ABFT (algorithm) techniques. Note that, software and algorithm techniques are converted into hardware checkers during high-level synthesis.

Consistent with processor core results, cost-effective resilience solutions for domain-specific hardware accelerators (Table 5) required the use of circuit-level techniques (e.g., a  $50 \times$  SDC improvement was achieved at less than 6% energy cost using a combination of application-guided selective LEAP-DICE and logic parity). However, even given the application-constrained context of accelerators, software-level (and algorithm-level) resilience techniques were unable to provide additional benefits.

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                            | ш        | sound | ed lat | Bounded latency recovery | recove   | ry |      |       |       |      |      | Unco | nstrai | ned re | Unconstrained recovery |      |          |          |       |      | Exec.  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------|----------|-------|--------|--------------------------|----------|----|------|-------|-------|------|------|------|--------|--------|------------------------|------|----------|----------|-------|------|--------|

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                            | <b>v</b> | DCi   | mprov  | vemen                    | t        |    | DUE  | impro | vemen | ţ    |      | SDC  | impro  | vemer  | t                      |      | 50       | E.       | prove | ment | time   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |                            | 0        |       |        |                          |          |    | 5    |       |       |      | Max  | 2    | 5      | 50     |                        | Max  |          |          |       | Max  | impact |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | InO | LEAP-DICE + logic parity   |          |       |        | -                        | m        |    | 0.6  |       |       |      | ~    | 0.7  | 1.6    | 2.4    | 2.8                    | 7.6  | <u> </u> | <u> </u> | 1     |      | 0%0    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | (+ flush recovery)         |          |       |        |                          | 6.7      |    |      |       |       |      | 17.9 | 1.9  | 3.8    | 5.9    | 6.5                    | 17.2 |          |          |       |      |        |

| origic         A         0.0         2.3         2.7         3.3         8.4         0.8         5.4         0.9         2.2         2.5         3.2         8.1         1         1           F         1.9         4.3         6.6         7.2         19.3         1.7         3.8         8.5         11         19.3         1.9         4.2         6.3         7.1         19           Bit         4         3.3         8.5         11         19.3         1.9         4.2         6.3         7.1         19         4.2         6.3         7.1         19         4.2         6.3         7.1         19         4.2         4.3         8.5         11         19.3         19         4.2         6.3         7.1         190         4.2         4.3         10         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4.3         4 |     | <u>.</u>                   |          |       |        |                          | <u> </u> |    |      |       |       | 10.4 | 17.9 | 1.9  | 3.8    | 5.9    | 6.5                    | 17.2 |          |          |       |      |        |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                            | K        |       |        |                          |          |    | 0.8  |       |       |      | 8.4  | 0.9  | 2.2    | 2.5    | 3.2                    | 8.1  |          |          | I     | 1    | 0%0    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | parity (+ flush recovery)  |          |       |        |                          |          |    |      |       |       |      | 19.3 | 1.9  | 4.2    | 6.3    | 7.1                    | 19   |          |          |       |      |        |

| opic         A         39.3         41.1         41.5         43.1         45         39.3         39.9         41.0         50.9         12.5         33.9         8.1         10         18.2 $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                            |          |       |        |                          |          |    |      |       |       |      | 19.3 | 1.9  | 4.2    | 6.3    | 7.1                    | 19   |          |          |       |      |        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | DFC + LEAP-DICE + logic    | A        | 9.3 4 |        | 41.5                     |          |    | 39.3 |       |       | 42.5 | 45   | 3.3  | 5.1    | 5.6    |                        | 10.6 |          |          | I     | 1    | 6.2%   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                            |          |       |        |                          |          |    |      |       |       |      | 50.9 | 1.4  | 4.8    | 8.1    | 10                     | 18.2 |          |          |       |      |        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                            |          | 4.2   | 56.7   | 60.2                     |          |    | 45.8 |       |       |      | 60.3 | 10.6 |        | 17.4   | 19.9                   | 25.5 |          |          |       |      |        |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | Assertions + LEAP-DICE +   |          |       |        |                          | 1        |    |      |       |       |      |      | 0.7  | 0.9    | _      | 1.1                    | 7.6  |          |          | I     | 1    | 15.6%  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | logic parity (no recovery) | Ь        |       |        |                          |          |    |      |       |       |      |      | 1.4  | 1.8    | 2.2    | 2.2                    | 17.2 |          |          |       |      |        |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                            | Щ        |       |        |                          |          |    |      |       |       |      |      | 17.1 | 17.5   | 18     |                        | 24.5 |          |          |       |      |        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | CFCSS + LEAP-DICE +        |          |       |        |                          | 1        | _  |      |       |       |      |      | 0.3  | 1      | 1.4    | 1.3                    | 7.6  |          |          | I     | I    | 40.6%  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | logic parity (no recovery) | Ь        |       |        |                          |          |    |      |       |       |      |      | 0.8  | 1.8    | 2.9    | 3.1                    | 17.2 |          |          |       |      |        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                            | Щ        |       |        |                          |          |    |      |       |       |      |      | 41.5 | 43     | 44.6   |                        | 146  |          |          |       |      |        |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | CFCSS + LEAP-DICE +        | <u> </u> |       |        |                          | 1        |    |      |       |       |      | 1    | 0.3  | 1      | 1.4    | 1.3                    | 7.6  |          |          | I     | I    | 40.6%  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | logic parity (no recovery) | Ь        |       |        |                          |          |    |      |       |       |      |      | 0.8  | 1.8    | 2.9    |                        | 17.2 |          |          |       |      |        |

| $ \frac{A}{P}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                            | Щ        |       |        |                          |          |    |      |       |       |      |      | 41.5 | 43     | 44.6   | 44.9                   | 146  |          |          |       |      |        |