#### **CHAPTER 4**

# **Platform Power Management**

Each CPU in a data center requires a large amount of support hardware. This support hardware, contained within the server chassis, is generally referred to as the *platform*. Over the years, more and more of the platform has been integrated into the CPU, such as memory controllers and PCIe connectivity. However, a large portion of the overall power in the data center is still consumed by the support infrastructure outside of the CPUs and memory. Storage (drives), networking, power delivery, and cooling all can contribute a significant amount to the overall cost of a data center. Some of these components (like the fans) have sophisticated algorithms that attempt to manage their power consumption, whereas others (like drives) tend to employ minimal power management techniques.

# **Platform Overview**

A *platform* is conceptually everything (including the CPU) required for a CPU to operate. It includes the power delivery (which converts electricity from the power grid into something usable by the different platform components), cooling (fans, heat sinks, etc.), as well as the memory, drives, and networking that are connected to the CPU sockets.

### **Common Platform Components**

A single platform is commonly referred to as a *node*, which generally incorporates from one to eight CPUs that are connected with coherency. A wide range of platform designs are possible and available. However, some standard building blocks go into just about any platform design (see Table 4-1). This chapter investigates some of the power management characteristics of these various platform components.

<sup>&</sup>lt;sup>1</sup>Coherency is a mechanism that allows different software threads running on different CPUs to share a large set of physical memory without requiring software management.

Table 4-1. Common Platform Components

| Component      | Description                                                                                                                                                                                                                                                                        |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU            | These processors provide the computation and execution of user workloads. See Chapter 2.                                                                                                                                                                                           |

| Memory         | Memory provides temporary storage for data being used by the CPUs. See Chapter 3.                                                                                                                                                                                                  |

| Storage        | Storage (drives) provides bulk storage of data. SAS (serial attached SCSI) and SATA (Serial ATA) are two common protocols for connecting drives to a storage controller.                                                                                                           |

| Networking     | Networking provides for communication between multiple nodes. Ethernet and InfiniBand (IB) are common networking interfaces. NICs (network interface cards) provide the connectivity between the CPU and the Ethernet/IB network.                                                  |

| Power delivery | Different components in the system require different voltages and types of current (AC/DC). VRs (voltage regulators) are DC to DC converters that take an input voltage and step it down to a lower operating voltage. PSUs (power supplies) take AC current and convert it to DC. |

| Cooling        | When servers consume power, it is turned into heat. Fans and other cooling devices are used to extract that heat from the platform to maintain a safe operating temperature.                                                                                                       |

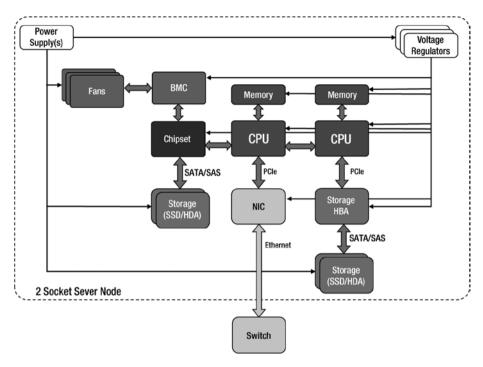

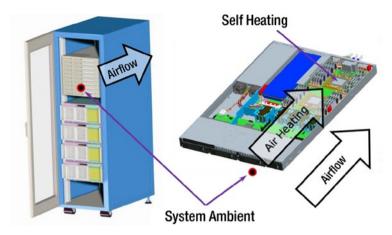

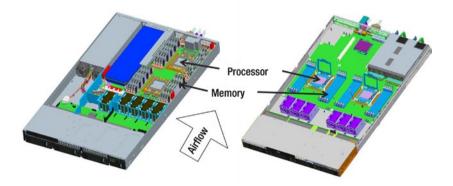

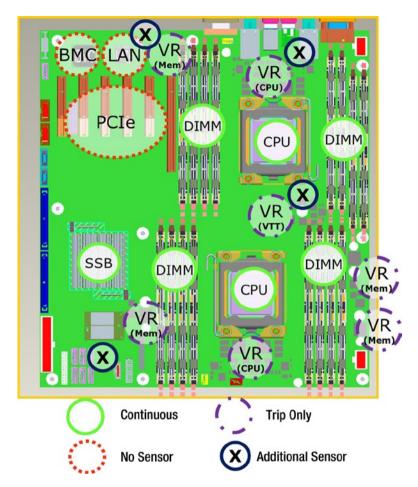

A wide range of platform designs are used in the industry. Some designs provide large amounts of data storage and connect a large number of drives. Others may be completely driveless and use the network to bring data into the node. Figure 4-1 provides an example of one potential platform node with two CPU sockets.

Figure 4-1. Two socket platform node example

#### Integration

As time has progressed, more pieces of the platform have been integrated into fewer discrete chips. This can save cost and power and even improve performance in some cases.

### **CPU Integration**

For many years, the sole role of the CPU die was to provide one (or a couple of) cores and a supporting cache hierarchy. These were then connected to some system bus (front-side bus (FSB) on Intel systems), which then connected them to a chipset. This chipset provided a memory controller and PCI connectivity for devices like drive and network controllers. These busses consumed power, limit bandwidth, and increased latencies. As a result, more and more of the chipset began to get integrated into the CPU itself, both to reduce platform power and to increase performance. Table 4-2 provides an overview of some of the key integration milestones over Xeon processor generations.

Table 4-2. Integration over Intel EP CPU Generations

| Generation                         | Integration                                                  |

|------------------------------------|--------------------------------------------------------------|

| Nehalem                            | Memory controllers                                           |

| Jasper Forest (Nehalem Derivative) | PCIe 2.0 (up to 16 lanes)                                    |

| Sandy Bridge                       | PCIe 3.0 (up to 40 lanes) that can share L3 cache with cores |

| Haswell                            | Voltage regulators                                           |

Although power can be saved (fewer platform busses and I/Os driving them) and performance can be improved (on-die busses provide higher bandwidth and lower latency compared to off-chip interconnects), this integration is not free. The area of the CPU must increase to accommodate the additional components. CPU packages may need to accommodate more pins (which increases cost). This integration also moves power that was previously consumed out in the platform into a much closer physical location to the traditional CPU components. This either requires that more power (and cooling) be provided to the CPU or that less power be made available to the cores.

CPUs are typically built on the latest manufacturing process technology that provides the best power efficiency. Other devices in the platform are usually manufactured on older technologies. When they are integrated into the CPU, these capabilities get an immediate upgrade in power efficiency due to the process technology improvement.

#### **Chipset Integration**

The CPU absorbed the memory controller and some of the PCIe connectivity away from the chipset in the Nehalem and Sandy Bridge generations. However, the chipset has started integrating other components of the platform. Storage and network controllers are now standard on server chipsets. PCIe is still provided, although it is generally lower performance than the CPU links and is focused on low-bandwidth connectivity. Chipsets are discussed in more detail later in this chapter.

### Microservers and Server SoCs

Server system on a chip (SoC) components are becoming more and more prevalent. In these designs, the chipset and CPU are integrated together into a single die or as a multi-chip package (MCP). The primary goal here is to reduce the costs of deploying a single CPU node. The concept of a microserver is where you target these lower-cost devices in mass quantities in a data center to provide adequate performance at reduced costs. Although microservers have received significant press in recent years, deploying these lower-cost, power efficient, highly integrated devices into embedded markets is arguably even more interesting.

### Platform Manageability

Running a large data center requires capabilities for monitoring and managing the various components that go into a data center. Controlling fans, rebooting nodes that have crashed, monitoring power, and many other tasks are all critical to managing a typical data center. These concepts will be discussed in Chapters 5 and 9. Rather than having software running on the CPU cores to provide these capabilities, many server platforms have traditionally deployed dedicated management chips. These are commonly called baseboard management controllers (BMCs).

Server BMCs are OEM-proprietary devices with a small microcontroller at their heart. They have tentacles throughout the platform in order to monitor and control the various subsystems. Platform Environment Control Interface (PECI) is a standard used for interactions between BMCs and CPUs. System Management Bus (SMBus) protocol is also commonly used for providing telemetry information from platform devices (power supplies, etc.) to the BMC. Intelligent Platform Management Interface (IPMI) is an interface used for software to interact with the BMC for extracting the wealth of information of which the BMC is aware (see Chapter 7 for examples). A single platform with N coherent CPU sockets is generally paired with a single BMC, but this is not strictly required.

BMCs themselves do not consume a significant amount of power but can have a notable impact on the overall power draw of the system since they control the fans associated with a given platform node. Thermal management is discussed later in this chapter. Servers without BMCs have been investigated in order to reduce power consumption and save on integration costs, but thus far, such designs have not taken off.

### **CPU Sockets**

Modern CPU nodes can support varied numbers of CPU sockets. Uni-processor (UP) and dual-processor (DP) servers make up the bulk of the server processor nodes sold today.

Multi-processor (MP) nodes commonly consist of four or eight processors, but other topologies are also possible. MP platforms have a higher procurement cost associated with them, and are frequently used in situations where large single-node performance or memory capacity is required. By moving to a larger number of CPU processors per node, the cost of some of the platform components can be amortized. For example, if each node requires a boot SSD and a network connection, one can potentially reduce the number of required SSDs and network connections by two times by going from a UP to a DP platform.

■ **Note** Due to the large procurement costs and usage models associated with MP systems, power efficiency and power savings are typically a lower priority for end users.

DP platforms provide an excellent cost/performance sweet spot. MP platforms have typically demanded a higher overall price per CPU, while UP platforms are not as effective at amortizing other platform costs (power and procurement). DP platforms also exhibit strong performance scaling for many workloads.

UP server systems have traditionally been relegated to situations that simply did not demand the performance of a DP or MP system. Rather than being deployed in a data center, they have been used in other lower-end server appliances such as small business NAS (network-attached storage). As single node performance continues to increase, UP systems cost amortization is improving. If a DP system requires two network connections in order to provide sufficient data to saturate the capabilities of the cores, then there is no additional savings by scaling to two sockets. Server SoCs (like microservers) that incorporate capabilities like networking also help reduce the power and procurement amortization benefits of multi-socket systems.

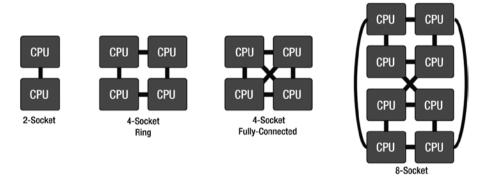

Platforms that directly connect two to eight processors coherently to each other are said to be *glueless*. A variety of glueless topologies have been developed over time. Figure 4-2 shows some examples from recent processor generations from Intel. Note that in each of these examples, every socket is either one or two "hops" from each other socket on the platform. It is possible to connect even more processors in a coherent network, but this generally requires special hardware (or glue) called node controllers. If all the processors are directly connected to each other through point to point links, the platform is said to be *fully connected*. Fully connected platforms generally have lower latencies, higher bandwidth, and better performance scaling than platforms that are not. There is a small power cost for the additional connectivity, but the return on investment (performance) is well worth the cost for most usage models.

Figure 4-2. Example glueless coherent platform topologies

#### Node Controllers

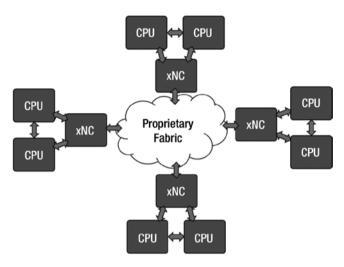

Although the majority of platforms limit the number of coherent CPUs to a maximum of eight, it is possible to build much larger coherent systems using *node controllers* (*xNC*). Node controllers are generally discrete chips that connect one, two, or four CPUs out to other node controllers through a proprietary fabric (see Figure 4-3). These systems are frequently used for building supercomputers and can connect hundreds of processors and thousands of cores into a single coherent domain running a single operating system.

Note that it is also possible to build large supercomputers without node controllers by connecting a large number of nodes non-coherently through a network. The differences between these designs are beyond the scope of this book.

Figure 4-3. Node controller example

# **Memory Risers and Memory Buffer Chips**

Certain high-end servers demand very large memory capacities. Databases are the most common example. Each CPU socket is generally limited in the amount of DDR memory to which it can directly attach. The number of DDR channels on a socket is constrained by packaging and die costs. The number of DIMMs on a channel is limited by electrical loading constraints. LR-DIMMs attempt to address some of these issues but can only go so far. In order to expand memory past the constraints imposed by the CPU socket, memory risers and memory buffer chips have been used on some high-end servers. Rather than connecting the CPU directly to memory, the CPU communicates with a discrete chip in the platform that is then able to communicate to the actual DDR memory. In these platforms, the memory is connected on separate riser cards, where a set of DIMMs is connected to a card, and then that card is connected into the motherboard. There have been various flavors of these technologies over the years. Intel has historically productized a memory buffer technology as part of its EX platforms (called Scalable Memory Buffer [SMB]), and other OEMs have deployed their own proprietary technologies to provide similar capabilities. These buffer chips do consume measurable power (usually a few watts), but they tend to be dwarfed by other power in such platforms (including the memory that they provide connectivity to).

# **Server Chipsets**

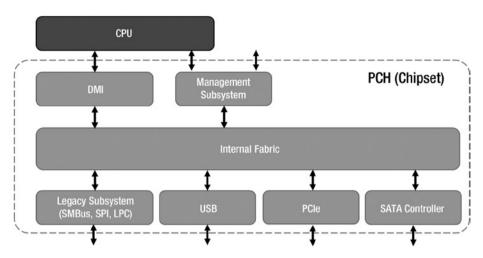

Many server platforms employ discrete chipsets that are connected to the CPUs. These devices provide key legacy capabilities required for booting the platform, capabilities for manageability, and also integration of many features that otherwise would require discrete controllers (such as storage, network, and USB controllers). Some SoCs integrate the chipset functionality into the package with an MCP, while others (like Avoton) integrate the entire chipset into the same die as the CPU. The discrete chipsets used in many Xeon server designs at Intel are called a PCH (Platform Controller Hub). The PCH attaches to the CPU via a proprietary DMI (Direct Media Interface) link, and provides boot, manageability, and I/O services to the platform.

The PCH has been the south bridge of the two-chip Xeon Intel Architecture since the Nehalem/Tylersburg generation and is a companion to the CPU. This architecture succeeds the Intel Hub Architecture, which was a three-chip solution. Successive generations of PCH have advanced the I/O capability of IA platforms, with Gen2 PCIe, Gen3 SATA, and Gen3 USB now available on Wellsburg. A microcontroller-based power management controller (PMC) and a Management Engine (ME) were added to the PCH to support traditional power management features, along with several extended features.

The chipset serves a variety of purposes in the platform. Table 4-3 provides a high-level summary of some of the key capabilities. Figure 4-4 shows an example block diagram of such a system. Table 4-4 enumerates some of the integrated functionality of modern PCHs.

Table 4-3. PCH High-Level Capabilities

| Capability                        | Description                                                                                                                                                                                                 |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| High-performance I/O connectivity | This includes PCIe, storage (SATA and/or SAS), networking, etc. These capabilities are only available when the CPU is active and the system is in the S0 state.                                             |  |  |

| Wake/boot                         | The PCH both detects wake events (like Wake on LAN) and sequences the platform to transition in and out of platform power states. The PCH also provides access to flash memory for BIOS.                    |  |  |

| Manageability                     | This provides interfaces for the data center to monitor and manage the node, such as reading temperatures.                                                                                                  |  |  |

| Real-time clock (RTC)             | This maintains the system clock that tracks clock time. If you unplug a desktop from the wall, your time and date is not lost since it is maintained on the RTC. The same capability exists in server PCHs. |  |  |

| Legacy I/O connectivity           | This provides connectivity to low-performance platform connectivity that is generally required for system operation.                                                                                        |  |  |

Figure 4-4. A typical server PCH architecture block diagram

Table 4-4. Primary PCH Components

| Component     | Description                                                                                                                                                                                                                                                             |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-die fabric | Interconnects exist on the PCH that are commonly called <i>on-die</i> or <i>on-chip</i> fabrics. These interconnects are conceptually similar to those in CPUs. These are not to be confused with fabrics that connect multiple CPUs together at the data center level. |

| DMI           | DMI provides a mechanism to connect the PCH and components connected downstream from the PCH to the CPU. It operates very similar to PCIe.                                                                                                                              |

| PCIe          | PCIe connectivity can be incorporated both into the CPU and the PCH and shares the same basic power management capabilities. The PCH is useful for high fanout, low bandwidth connectivity.                                                                             |

| SATA          | Storage connectivity is included on some PCHs and is discussed in the "Storage" section of this chapter.                                                                                                                                                                |

| USB           | USB is primarily targeted and consumer usage models but is also present in servers (particularly for debug usage models). It is discussed later in this chapter.                                                                                                        |

| Ethernet      | Ethernet integration is also incorporated into the PCH. Networking power management is discussed in the "Networking" section of this chapter.                                                                                                                           |

(continued)

Table 4-4. (continued)

| Component               | Description                                                                                                                                                                                                                 |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI/LPC<br>(legacy I/O) | Serial Peripheral Interface (SPI) and Low Pin Count Interface (LPC) provide connection points to platform boot devices that contain the BIOS/UEFI image, as well as firmware for other PCH components (e.g., ME, Ethernet). |

| ME                      | The Management Engine on the PCH provides platform management services, key management, and cryptographic services.                                                                                                         |

| SMBus                   | SMBus provides a legacy mechanism for communication with platform peripherals for system and power management-related tasks.                                                                                                |

The PCH has traditionally been the component that provides access to various high-speed I/Os (SATA, Ethernet, PCIe, USB), although these capabilities are increasingly being integrated into the CPU to create SoC components. The SATA/PCIe/Ethernet/USB interfaces provide access to external communication, including disk/solid-state storage, networking, USB ports, and manageability. Moving data with higher performance between two devices in a platform consumes non-trivial power, and integration is an effective way to significantly improve overall platform power consumption.

Internally, the PCH architecture is constructed with a mix of analog and digital components. Similar to the CPU uncore, analog design is used for designing the off-chip communication (e.g., PCIe/SATA/USB physical interface) and on-die memory (SRAM), while the bulk of the remaining system is built out of synchronous digital logic. Unlike traditional server CPUs, a large percentage of the chipset power is consumed by analog I/O circuitry (commonly called physical layer or PHY) and not the digital logic.

### PCH and Platform Power Management

The PCH orchestrates many of the platform power states introduced in Chapter 2. In addition to this task, it is responsible for managing its own power states. Table 4-5 provides an overview of the power management states in which the PCH participates.

Table 4-5. System States Supported by Server PCH

| State    | Description                                                                                                                                                                                        |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C-states | Low-power states for PCH I/Os                                                                                                                                                                      |

|          | See Chapter 2 for details on CPU C-states. PCH does not support all the traditional CPU C-states but places its I/Os in low-power states when the CPU is not active.                               |

|          | • C0 is an active state when the PCH logic and I/O are functional.                                                                                                                                 |

|          | <ul> <li>Cx is a clock/power-gated state, during which PCH I/Os are<br/>transitioned to a lower power-managed state.</li> </ul>                                                                    |

| S-states | Turning off the CPU package (sleep state)                                                                                                                                                          |

|          | See Chapter 2 for details on S-states. The PCH I/Os are turned off (except S0), but the PCH core logic remains active in all S-states.                                                             |

|          | PCH can wake the CPU up from S3/S4/S5 states based on platform signaling. Waking from an S3 state takes seconds, whereas waking from S5 requires a full system boot and can take multiple minutes. |

| M-states | Turning off the Management Engine                                                                                                                                                                  |

|          | These states are related to the Management Engine.                                                                                                                                                 |

|          | • M0: Active state, when platform is in S0 state.                                                                                                                                                  |

|          | <ul> <li>M3: Active state, when platform is in S3/S4/S5 state, used for<br/>out-of-band platform management and diagnostics.</li> </ul>                                                            |

|          | • MOff: Management engine is turned off in Sx.                                                                                                                                                     |

| G-states | Global states                                                                                                                                                                                      |

|          | See Chapter 2 for details. The PCH is active in G0 to G2 and is only off in the G3 state (mechanical off).                                                                                         |

Since the PCH controls the platform rails and clocks, it needs to remain powered on even in states where the CPU is powered off (G- and S-states). This is accomplished by using platform power rails that are successively powered off depending on the system state. The PCH provides a number of high-level capabilities that are successively disabled at lower power states. Table 4-4 provides an overview of these capabilities, and Table 4-6 shows how the capabilities are disabled in each power state.

| G-State | M-State | S-States | Power Rails                | Manageability | Wake Capability |

|---------|---------|----------|----------------------------|---------------|-----------------|

| G0      | M0      | S0       | All available              | Available     | N/A (awake)     |

| G0      | M3      | S3/S4/S5 | Wake + Manageability + RTC | Available     | Yes             |

| G2      | MOff    | S4/S5    | Wake + RTC                 | Disabled      | Yes             |

| G3      | MOff    | S4/S5    | RTC                        | Disabled      | None            |

Table 4-6. Example PCH Power States and Capabilities

Systems autonomously transition out of the G3 state and into the G2 state when power is supplied to the platform. From there, various wake events can be used to transition the state into a higher power operational mode as needed. As such, the G3 state is hidden from the user.

### **PCH Power Management**

The PCH consumes a small percentage of a node's overall power. Because the bulk of the power consumed by the PCH exists in the I/O PHYs, the typical power consumed under load is very dependent on the number of connected devices. The TDP power of Patsburg (the chipset used with Sandy Bridge and Ivy Bridge E5 processors) was 8 W to 12 W when all of the high-speed I/O ports were connected (fully populated). Wellsburg (paired with Haswell E5) consumed a TDP of 7 W when fully populated. Notable power can be saved if certain I/Os are not populated. Table 4-7 provides an overview of four different usage configurations of the PCH and the corresponding TDP power for those configurations.

| <b>Table 4-7.</b> PCH TDP Powe | r (W | () Consumption with Various I/O Port Configurations |

|--------------------------------|------|-----------------------------------------------------|

|--------------------------------|------|-----------------------------------------------------|

|             | Workstation | Server | Low Power     | Boot-Only |

|-------------|-------------|--------|---------------|-----------|

| USB2 Ports  | 14          | 6      | 2 (detection) | 0         |

| USB3 Ports  | 4           | 4      | 1 (detection) | 0         |

| SATA3 Ports | 8           | 5      | 2             | 0         |

| SATA2 Ports | 2           | 1      | 1             | 0         |

| PCIe Lanes  | 8           | 4      | 2             | 0         |

| TDP (W)     | 6.5         | 5      | 3.2           | 1         |

The Wellsburg PCH, which launched with the Haswell Server CPU, is built on a low-leakage process and does not implement techniques like voltage-frequency scaling or power gating to reduce the power consumed at runtime. Turbo is not available. In order to save power, clock gating is performed on logic features that are disabled or not currently in use. Since the PCH is I/O dominated, a sizable portion of the power is

consumed by the circuits that provide the physical interface to the platform. The voltage of these interfaces is generally static (as defined by industry standard specifications). Several power management states are defined for the links to opportunistically reduce power based on the operating state, as described in the following subsections.

If an entire section of logic is not being used, then the PLL (phase-locked loop) that drives that logic can be powered down. For example, if a user is building a compute node that lacks any local drives, the storage subsystem in the PCH can be completely powered down.

### **PCIe in Chipsets**

Prior to Sandy Bridge and Jasper Forest, chipsets provided the PCIe connectivity in the platform. When Sandy Bridge integrated PCIe into the CPU, the chipsets continued to provide this capability. Today in platforms with discrete PCH devices, PCIe connectivity is offered on both the CPU die and the PCH. PCIe in the PCH provides the same power-saving capabilities that are described in Chapter 3 (L1, DLW).

PCIe on the CPU provides high performance and (relatively) low latency connectivity at the expense of limitations in the fanout (devices smaller than x4 consume four lanes). The PCH, on the other hand, provides lower bandwidth and longer latencies, but can be bifurcated down to x1 making it an excellent choice for low bandwidth devices.

### **PCH Thermal Management**

The PCH contains thermal sensors in order to monitor the temperature and help guarantee that the PCH will not get to a dangerous temperature where reduced reliability or damage could occur. The PCH may throttle itself to stay under a target temperature or even initiate an immediate shutdown if temperature exceeds a catastrophic threshold. Like CPUs, PCHs are spec'd with a TDP rating that is used to design the thermal solution and an ICCMAX rating that is used to size the voltage regulators to power the voltage rails. They also contain similar thermal protection mechanisms such as shutting down the platform when catastrophic temperatures are detected. Platform thermal management is discussed in detail later in the chapter.

# Networking

Network interfaces—both the local LAN adapter as well as network infrastructure devices—are the gateway for the server platform to the rest of the world. Network activity demonstrates unpredictable distribution of packet arrival times at multiple scales. As a side effect, the network interfaces are never fully powered down. LAN adapters contribute ~5–10 W to the overall platform power. This power is not one of the primary power contributors in typical server platforms that deploy high-power CPUs and large amounts of memory. Although the LAN adapters themselves do not directly contribute a significant percentage of the platform power, their behavior and configuration can have a large impact on the power consumption of the CPU (and thus the platform).

■ **Note** Although network cards do not themselves contribute a significant percentage of the platform power consumption, their configuration and behavior can have significant impacts on CPU power (and thus platform power).

In typical usage, LAN component power is driven by five main factors. Table 4-8 provides a high-level summary of these factors (which are discussed in detail in the following pages.).

Table 4-8. Primary Factors in LAN Controller Power

| Factor                    | Description                                                                                                                                                                             |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ambient temperature       | LAN devices have traditionally been manufactured with high-leakage process technologies, resulting in a significant power increase at higher temperatures.                              |  |  |

| Attached media            | The type of connection (fiber optic, copper cable, etc.) can have a moderate impact on the power consumption.                                                                           |  |  |

| Configured speed          | LAN controllers can be configured by software to run at lower frequencies. This can save notable power.                                                                                 |  |  |

| Power management features | Various power management options are available that can trade off performance (latency) to save power.                                                                                  |  |  |

| Bandwidth                 | Packets per second have the biggest impact on NIC power (not raw bandwidth). However, on recent high-performance networking devices, there is not significant sensitivity to bandwidth. |  |  |

### Ambient Temperature, TDP, and Thermal Management

Many LAN vendors quote typical power numbers in their datasheets. However, there are no industry conventions as to what typical usage is, though many assume 25°C for ambient air temperature, and nominal voltage. An increase in temperature from 25°C to 70°C can increase the component power by 50% to 100% solely due to leakage (which itself is a function of the silicon process used to produce the device). As LAN controllers transition to lower leakage processes or are integrated into low-leakage SoC designs, the sensitivity to temperature will decrease.

Similar to CPU designs, the maximum quoted power of the LAN controller is measured assuming worst-case conditions, including high temperatures (~70°C ambient). The server platform thermal management—such as fan size and speed—is designed to cool to this maximum component thermal design point (TDP). LAN controllers are typically designed assuming passive cooling, and it is also common for these devices to exist in areas of limited airflow. Active cooling—such as fans—is discouraged because of server platform reliability concerns. The net result is, regardless of the functionality or media provided,

the server LAN component TDP must be 10 W or less (unless special design provisions are made at the platform level for additional fan cooling). Tables 4-9, 4-10, and 4-11 show some historical information about Intel LAN adapter TDP power.

Table 4-9. Historical TDP Power of Single-Port 1 Gbps Intel LAN Adapters

| Year | Device              | Ports/Speed | TDP (W)         | TDP (W) / Gbps |

|------|---------------------|-------------|-----------------|----------------|

| 2001 | Intel 82544EI PCI-X | 1x 1 Gbps   | 1.5 W           | 1.5 W          |

| 2004 | Intel 82541 PCI     | 1x 1 Gbps   | 1.0 W           | 1.0 W          |

| 2005 | Intel 82573 PCIe    | 1x 1 Gbps   | 1.3 W           | 1.3 W          |

| 2008 | Intel 82574 PCI     | 1x 1 Gbps   | 0.7 W           | 0.7 W          |

| 2012 | Intel I210 PCIe     | 1x 1 Gbps   | $0.7\mathrm{W}$ | 0.7 W          |

Table 4-10. Historical TDP Power of Multi-Port 1 GBps Intel LAN Adapters

| Year | Device           | Ports/Speed | TDP (W)         | TDP (W) / Gbps |

|------|------------------|-------------|-----------------|----------------|

| 2005 | Intel 82571 PCIe | 2x 1 Gbps   | 3.4 W           | 1.7 W          |

| 2009 | Intel 82576 PCIe | 2x 1 Gbps   | 2.8 W           | 1.4 W          |

| 2010 | Intel 82580 PCIe | 4x 1 Gbps   | 3.5 W           | 0.9 W          |

| 2011 | Intel I350 PCIe  | 2x 1 Gbps   | 2.8 W           | 1.4 W          |

| 2011 | Intel I350 PCIe  | 4x 1 Gbps   | $4.0\mathrm{W}$ | 1.0 W          |

Table 4-11. Historical TDP Power of 10 GBps Intel LAN Adapters

| Year | Device                               | Ports/Speed | TDP (W) | TDP (W) / Gbps |

|------|--------------------------------------|-------------|---------|----------------|

| 2001 | Intel 82597 PCI-X                    | 1x 10 Gbps  | 9.0 W   | 0.9 W          |

| 2007 | Intel 82598 PCIe                     | 2x 10 Gbps  | 6.5 W   | 0.3 W          |

| 2011 | Intel 82599 PCIe                     | 2x 10 Gbps  | 6.2 W   | 0.3 W          |

| 2012 | Intel X540 PCIe w/<br>10GBASE-T Phy² | 2x 10 Gbps  | 12.5 W  | 0.6 W          |

| 2014 | Intel X710 PCIe                      | 4x 10 Gbps  | 7.0 W   | 0.17 W         |

<sup>&</sup>lt;sup>2</sup>This device includes a 10GBASE-T attached media, increasing the TDP power. The other controllers listed must be paired with a separate attached media.

■ **Note** Typical power for NIC cards is well below their TDP specifications. NICs frequently operate at lower temperatures than their specifications, saving significant leakage power.

In typical usage, the LAN component does not operate at TDP. Some LAN devices include thermal sensor diodes, as well as management interfaces, to enable other platform components to query the component thermal state and adjust fan speed. In practice, many of these platform methods require additional calibration of the thermal sensors which, if not done, may limit the effectiveness of the fan speed algorithms.

#### Attached Media

Most LAN adapters can be paired with a variety of different interconnect types that provide the actual connectivity between the LAN adapter and network switches. These are called *attached media*.

Server LAN implementations have a greater variety of media types than those found on client systems. Whereas most equate Ethernet to the pervasive RJ-45 connector and 10BASE-T (10 Mbps), 100BASE-TX (Fast Ethernet, or 100 Mbps) and 1000BASE-T (1 Gbps Gigabit Ethernet), server platforms have employed several media types as summarized in Table 4-12.

Table 4-12. Types of Attached Media

| Туре                                    | Max Distance     | Power      | Latency                |

|-----------------------------------------|------------------|------------|------------------------|

| Multi-mode short reach (SR) fiber optic | ~400 m           | ~1 W       | Slight increase        |

| Single-mode long read (LR) fiber optic  | ~10 km           | ~1 W       | Slight increase        |

| KX/KX4/KR Backplane (copper)            | Server backplane | 100s of mW | Best                   |

| Direct Attach (DA)                      | 3-10 m           | 100s of mW | Best                   |

| BASE-T                                  | 100+ m           | 2-3 W      | Adds ~1<br>microsecond |

<sup>■</sup> **Note** Cost and distances are generally the deciding factors in attached media selection. Latency is important to a subset of customers.

Each of these media solutions have tradeoffs between cable cost, power, distance, and even propagation velocity (fiber is slightly slower than copper-based connections). Because of this diversity, many server LAN connections are shipped with an SFP or SFP+ cage, which accepts various media type pluggable modules.

### **LAN Power Management Features**

A number of common features are used for reducing power of both the LAN devices and the CPU. In addition to these, higher-end server LAN adapters implement multiple queues and methods to balance network traffic across multiple CPU cores. As a result, CPU cores can operate at a reduced frequency and save power.

### **Media Speed**

Some media types—such as BASE-T and backplane—support establishing a link at lower media rates than the maximum possible—such as a 1 Gbps adapter linked at 100 Mbps. Lowering the established link rate often reduces the component power, sometimes by as much as 50%. As the link speed drops, the internal synchronized media clock lowers in frequency, leading to a lower dynamic power. Another effect relates to effective packet rates, since LAN component power varies more as a function of packet rate than packet size. For each packet, the LAN controller performs various lookups on the packet headers. Reducing the media rate reduces the packet rates as well, again leading to lower dynamic power.

In practice, changing media speed is not applicable for most server usage models. The transition latency is slow, and the reduced speed results in significant peak throughput reductions and the potential for increased latencies. Although this can save notable power from the perspective of the LAN controller, it is generally not as significant as a percentage of the overall platform power.

### **Energy Efficient Ethernet**

BASE-T and backplane media also support Energy Efficient Ethernet³ (EEE). This is frequently called *triple-E* for short. EEE devices enter into a low power mode during idle periods, periodically sending idle sequences to keep the link active and sending a wakeup symbol to the peer when the link needs to be reactivated. Depending on the media, the link transitions from idle to active are less than about 16 microseconds. BASE-T devices can reduce their PHY idle power as much 400 mW with 1000BASE-T, and by 2 W with 10GBASE-T.

EEE is managed by the NIC driver and can be controlled at runtime. It is generally enabled by default. The latency cost of EEE is not noticeable in many usage models, but the power savings is also not particularly significant. Latency sensitive users may want to attempt to disable this capability.

<sup>&</sup>lt;sup>3</sup>EEE is decribed in detail in IEEE Std 802 3az-2010

#### Wake on LAN

*Wake on LAN* (WoL) is a common feature available on server LAN adapters. It is not a power-savings feature as much as a mechanism to wake the system from an S-state.

If the platform supports suspend or wake from soft-off modes, WoL allows remote administrators a simple method to remotely activate a server platform. Often, the LAN interface will reduce link speed automatically when entering this state to minimize power and await receipt of a wake pattern. A common pattern used is the *Magic Packet* pattern. Upon receipt, the LAN controller asserts a signal to the platform to bring the system out of the low-power state.

### **Active State Power Management (ASPM)**

Discrete LAN controllers are connected using PCIe. As such, PCIe Active State Power Management is available to manage power on LAN controllers. PCIe power management is discussed in Chapter 3.

NIC ASPM L1 is frequently disabled in server deployments. This can frequently be performed in the system BIOS. The latency implications are frequently not worth the low amount of power savings. One common issue with ASPM L1 is that it blocks communication between a driver (running on the CPU) and the NIC device. When communication is required, the core is then stalled. This ends up wasting CPU power, which eats into the already small savings from L1.

#### **Interrupt Moderation**

Interrupt moderation is another common feature of LAN controllers. It limits the rate at which interrupt signals are delivered to the host CPU. This often reduces the CPU utilization with little to no observable impact to bandwidth. Interrupt moderation has little impact on NIC power, but the decreased CPU utilizations can significantly improve CPU power consumption. It can also make additional CPU cycles available for other processes, improving the throughput of the node. By rate limiting interrupts, the CPU is notified less often, resulting in an increase in latency and response time. The amount of latency impact can be tuned inside the NIC driver and is commonly configured to levels on the order of 100–200 microseconds. This feature is typically enabled by default, and can be disabled (or configured) inside the NIC driver configuration.

Interrupt moderation can have a significant impact on power and latency in systems, and is frequently overlooked. Tuning this feature should be a priority for anyone who is concerned about latency and response times.

DMA coalescing is a related feature that attempts to queue up data transfers inside the NIC and burst them into the CPU. The intention of this feature was to allow the CPU to get into a low-power idle state between bursts of activity. In practice this feature has shown minimal effectiveness in server environments while also significantly increasing network latencies. It is not enabled by default.

### **USB**

USB connectivity is provided by server PCHs. Many large-scale data centers do not connect devices to USB under normal operation, but it is common for USB ports to be included on those platforms. "Crash cart" support is a common usage model, where USB is periodically used to connect a keyboard/mouse for local debug, or to connect a USB drive for similar purposes. USB can also be used in some low-end storage systems for connecting USB storage. Power management of USB can be very effective at saving power at minimal to no power cost due to these limited usage models.

#### **Link Power States**

The initial USB power management capabilities were very coarse grained. A *suspend/resume* scheme provided two levels—effectively "on" and "off." These take milliseconds for transitions, making them inadequate for many power-efficiency usage models. USB devices are common in consumer usage models where achieving very low idle power is critical to achieving long battery life. As a result, USB has been a focus for power optimization in these environments. Much of these capabilities are unnecessary in server usage models.

USB 2.0 originally only supported these two levels but later added support for L-states that complemented the suspend state. On USB 2.0, the state of the link is tied to the power state of the device. These states are summarized in Table 4-13. Suspend can still be used for states that have no latency sensitivity (such as S3/S4).

Table 4-13. USB 2.0 Power States

| State | Name             | Link Savings | Device Savings               | Exit Latency |

|-------|------------------|--------------|------------------------------|--------------|

| L0    | On               |              |                              |              |

| L1    | Sleep            | ~100 mW      | Device-specific              | microseconds |

| L2    | Suspend          | ~125 mW      | Device draws almost no power | milliseconds |

| L3    | Off/Disconnected | ~140 mW      | Device powered down          | milliseconds |

Note: Power savings are design dependent. These numbers provide a reference point.

On USB 3.0, the device power states were decoupled from the link power states. U-states were defined that control the power state of the link only. Table 4-14 provides an overview of the four USB 3.0 link power states.

Table 4-14. USB 3.0 Link Power States

| State | Name        | Link Savings     | Exit Latency |

|-------|-------------|------------------|--------------|

| U0    | Link active |                  |              |

| U1    | Link down   | ~100 mW per lane | Microseconds |

| U2    | Link down   | ~125 mW per lane | Milliseconds |

| U3    | Link off    | ~140 mW per lane | Milliseconds |

Note: Power savings are design dependent. These numbers provide a reference point.

### Link Frequency/Voltage

USB has gone through three generations. Each generation has a single frequency at which the device runs (see Table 4-15). Multiple voltage/frequency points are not supported. Newer generation devices support (by rule) backward compatibility to the prior generation frequencies.

Table 4-15. USB Generations

| Generation | Frequency | Duplex | Theoretical Bandwidth    |

|------------|-----------|--------|--------------------------|

| USB 1.x    | 12 MHz    | Half   | 1.5 MB/s                 |

| USB 2.0    | 480 MHz   | Half   | 35 MB/s                  |

| USB 3.0    | 5 GHz     | Full   | 500 MB/s (per direction) |

USB 3.0 moved to a full-duplex design, effectively providing separate communication channels for both directions, increasing the peak throughput when data are transferred in both directions simultaneously. This required the addition of two more differential pairs, and is similar to a single lane of PCIe or a SATA connection.

# **Storage**

Many modern data centers deploy storage in a variety of different ways. Some compute nodes have no local storage and depend entirely on the network to provide access to remote storage. It is also common to see compute nodes with a single drive (commonly an SSD) that provides for high-performance local storage. Other nodes can be targeted for storage and can provide access to a large number of drives. These nodes are connected to compute servers through high-performance interconnects to provide large pools of shared storage.

Traditionally, drives have been connected through PCIe-based controllers. Two standard interfaces exist for these controllers: SATA and SAS. Serial Advanced Technology Attachment (SATA) is the lower cost of the two, but it also provides lower peak performance. SATA can be used both in consumer and server usage models. Serial attached SCSI (SAS) is generally more expensive and higher performance and is targeted at enterprise usage models. SATA drives can be connected to a SAS infrastructure, but SAS drives cannot be connected to a SATA controller. SATA and SAS support both SSDs (solid state drives) and HDDs (hard disk drives). In addition to providing higher peak performance, SAS provides the ability to connect a large number of drives to a single controller, making it popular in very high capacity deployments.

In recent years, SSDs have begun to be directly connected on PCIe. Non-Volatile Memory Express (NVMe) is a specification for performing this direct connection. NVMe provides lower latency and higher performance than SAS and SATA. This is particularly well-suited for high performance compute nodes that require local storage. NVMe SSDs exhibit similar power characteristics to SATA and SAS SSDs. Their potential for higher performance also translates into higher power consumption.

Storage power consumption is generally not a significant component of the overall node power in traditional compute servers. However, the power consumption of the drives on a storage node can dwarf the other components on the node. Storage power is also more significant in low-power, low-performance servers where the drive power is not amortized across a high-power CPU node.

### Storage Servers and Power Management

In a typical storage server the CPU complex manages tens to thousands of drives. Storage servers can use a mix of SSDs and HDDs, and the mix is determined by the performance needs. SSDs have higher procurement costs but provide improved performance. A significant amount of power in storage servers is consumed by the drives. Cooling a dense storage complex can also consume non-trivial power.

It is increasingly critical to manage the power consumed by the storage devices, without adversely affecting performance. Various power management schemes can be used depending on the performance requirements of the application. In a cold storage system where a massive amount of data is maintained but accessed rarely with low performance and latency requirements, aggressive power management can be used to reduce costs. On the other hand, limited power savings is used in performance- and latency-critical storage deployments. Aggressive power savings in such environments can be detrimental to performance but can also reduce overall data center power efficiency by forcing compute nodes to wait longer for data (wasting power in the process).

Power savings opportunities exist both within the drives and in the communication layer between the drives and their controllers. Storage power management schemes have been developed for both server usage models as well as consumer usage models. In consumer usage models, very low idle power is critical for battery life, and capabilities have been developed to address these concerns. These same capabilities may be available in the server space but can provide poor tradeoffs. A few hundred milliwatts of power savings is commonly a poor tradeoff if it could result in milliseconds of response time increase.

#### HDDs and SDDs

SSDs generally provide higher bandwidth and lower latencies than HDDs; however, this has traditionally come at increased power and cost per capacity. Actual power consumption is drive dependent, and can range anywhere from a couple of watts to more than 10 watts.

Traditionally, 3.5" HDDs have been extensively used in data centers and other server applications. They can provide the best cost per GB due to the larger platters. 2.5" HDDs do tend to exhibit lower power draw than 3.5" drives of the same capacity, but this benefit tends to be overshadowed by their overall lower maximum capacity in the same technology generation.

The amount of traffic that an HDD is servicing has minimal impact on the amount of power that is consumed. Rather, the state of the drive (Is it spinning? Are the heads loaded?) is the predominant component of HDD power consumption. SSDs, on the other hand, exhibit significant power dynamic range as a function of bandwidth. The act of reading and writing the cells itself consumes a significant percentage of the drive power. SSDs' power consumption also appears to scale with capacity. This is not because the cells themselves consume significant power, but because peak performance of these higher capacity drives is frequently higher, providing more potential for power consumption.

Power consumption during spin-up of an HDD is often the highest power draw of all of the different operating states of an HDD. It can dwarf the power consumption of normal operation. In storage servers with a large number of HDDs, staggered spin-up can be employed to prevent the excessive power consumption of spin-up, which may result in a power shortage. Staggered spin-up starts one drive at a time, either waiting for the drive to signal that it is ready or waiting a predefined amount of time prior to starting the next drive. Many data center designers are concerned about the *provisioned power* of each node, rack, and so on. This is the amount of power that the system must be designed to provide and is generally less than the sum of the worst-case power of every individual subcomponent in the system. When spin-up is staggered, platform power delivery does not need to be designed for this high-peak power across many drives simultaneously, which means that both cost and the potential for compute density improve. However, this comes at the cost of additional potential latency when drives are spinning down for power efficiency reasons.

### SATA and SAS Drive Power Management

Power management of drives can be split into two categories: saving power on the actual drive and saving power on the interconnect (PHY). SAS and SATA have many similarities in their power management methodologies and terminology. Power management of the drive itself is significantly more important than the PHY.

SATA devices (drives) support four power states as shown in Table 4-16. These states can save significant power. The Sleep state is rarely used on servers. You would likely not want to use Standby with HDDs on a compute server when any activity is possible, but careful use is possible on large storage arrays.

| Table 4-16. | SATA Device Power Savings <sup>4</sup> |

|-------------|----------------------------------------|

|-------------|----------------------------------------|

| Action           | Description                                                                               | Receives<br>Commands | HDD       | Wake Latency  |

|------------------|-------------------------------------------------------------------------------------------|----------------------|-----------|---------------|

| Working (active) | Normal operation.<br>Fully powered.                                                       | Yes                  | Spun up   | N/A           |

| Idle             | Active power savings.  May take longer to respond to commands.                            | Yes                  | Spun up   | Milliseconds  |

| Standby          | Device still responds to<br>typical commands, but<br>response time may be<br>significant. | Yes                  | Spun down | <= 30 seconds |

| Sleep            | Device is put to sleep.<br>Must be explicitly<br>woken up.                                | No                   | Spun down | <= 30 seconds |

SAS power management is conceptually very similar to that of SATA. The PHY supports both Partial and Slumber states with the same characteristics. In the T10 SAS standard, additional states are defined. Although the ATA8-ACS SATA standard only calls for the four states enumerated in Table 4-16, SATA drives may also support similar states to SAS. Table 4-17 provides a summary of these states with ballpark power savings estimates. Note that significant HDD power savings is only possible when significant exit latency costs are accepted. As a result, these power savings modes are typically only deployed after significant idle periods (if at all).

Table 4-17. SAS/SATA HDD Power Savings Modes

| State           | Spinning      | Heads    | Power Savings | Exit Latency |

|-----------------|---------------|----------|---------------|--------------|

| Active          | Full speed    | Loaded   | Baseline      | N/A          |

| Idle A          | Full speed    | Loaded   | ~10%          | ~100 ms      |

| Idle B          | Full speed    | Unloaded | ~20%          | ~200-400 ms  |

| Idle C          | Reduced speed | Unloaded | ~50%          | Seconds      |

| Standby Y (SAS) | Spun down     | Unloaded | ~90%          | Seconds      |

| Standby Z (SAS) | Spun down     | Unloaded | ~90%          | Seconds      |

| Standby (SATA)  |               |          |               |              |

<sup>4</sup>ATA8-ACS Standard. www.sata-io.org/sites/default/files/images/SATAPowerManagement\_ articleFINAL\_4-3-12\_1.pdf.

For the PHY, both SAS and SATA supports two low-power modes; Partial and Slumber (see Table 4-18). After some predetermined period of inactivity, either the host or the device can signal the PHY to enter its reduced power state. PHY power management has moderately long wakeup latencies, limiting the ability for fine-grained power savings. Slumber has quite long wake latencies, which preclude them from being used in some server usage models. Partial also achieves idle power on the order of  $\sim 100$  mW, so further power savings at the expense of latency can be counter-productive at the platform level outside of deep idle platform states. DevSleep is predominantly a consumer device power state.

Table 4-18. PHY Power States<sup>5</sup>

| Action           | Wake Latency  |

|------------------|---------------|

|                  | Wake Laterioy |

| Active (SAS)     | N/A           |

| PHY Ready (SATA) |               |

| Partial          | <10 μs        |

| Slumber          | <10 ms        |

| DevSleep (SATA)  | ~1 s          |

SSD drives are common in both consumer and enterprise environments. However, these drives have different characteristics and optimization points. Low-power operation and idle power optimization is critical in the consumer space, and the drives have been optimized for those cases. On the other hand, this has been less of a focus in many enterprise drives. Unlike with HDDs, enterprise SSDs may consume only 25% (or less) of their peak read bandwidth power while running in an Active Idle state (and maintaining fast response times). Traditionally, enterprise SSD procurement costs have dwarfed power costs, and users were not likely to deploy SSDs into areas that would be exposed to significant idle periods. As time progresses, the cost per GB of SSDs is decreasing. This will enable SSDs to compete in usage models traditionally reserved for HDDs and is expected to make power management more of a focus.

### Frequency/Voltage

SATA and SAS both have evolved over time by increasing frequencies to provide higher bandwidth. Table 4-19 illustrates how these generations have evolved. Newer generation devices support (by rule) backward compatibility to the prior generation frequencies, and the operating voltage has been held constant.

<sup>%</sup>www.sata-io.org/sites/default/files/documents/SATADevSleep-and-RTD3-WP-037-20120102-2 final.pdf

| SATA Generation | SAS Generation | Link Frequency | Theoretical Peak Bandwidth |

|-----------------|----------------|----------------|----------------------------|

| SATA 1.x        | SAS 1.0        | 1.5 GHz        | 150 MB/s                   |

| SATA 2.x        | SAS 1.0        | 3 GHz          | 300 MB/s                   |

| SATA 3.x        | SAS 2.0        | 6 GHz          | 600 MB/s                   |

| -               | SAS 3.0        | 12 GHz         | 1200 MB/s                  |

Table 4-19. SATA and SAS Generations

SATA and SAS traditionally transfer data serially (1 bit of data at a time) and use  $8b/10b^6$  encoding, which consumes 20% of the data in order to support the high-speed transmission.

80% \* (1.5 GHz / 8 bits per byte) = 150 MB/s

SATA 3.2 includes support for PCIe connected devices, which can leverage the parallel nature of PCIe to achieve even higher throughput. It includes the SATA 3 capabilities for traditional SATA connectivity (at the same bandwidth).

### **NVMe Drive Power Management**

NVMe provides power management capabilities that allow the power to be scaled down at the cost of lower throughput and higher latency. Seven different states are defined (numbered 0 to 6) as shown in Table 4-20.

| <i>Table 4-20.</i> | NVMe | Power | States |

|--------------------|------|-------|--------|

|--------------------|------|-------|--------|

| State  | Operational | Exit Latency | Performance                                                  |

|--------|-------------|--------------|--------------------------------------------------------------|

| 0      | Yes         |              | Peak                                                         |

| 1 to 4 | Yes         | Microseconds | Degraded throughput and latency with increasing exit latency |

| 5      | No          | ~50 ms       |                                                              |

| 6      | No          | ~500 ms      |                                                              |

NVMe allows the host to manage power statically or dynamically to complement autonomous power management performed by the NVMe drives. When power is managed statically, the host predetermines the power allocated to the NVMe drives and sets the NVMe power state of each drive. When the host manages power dynamically, the NVMe power state of each device is updated periodically to accommodate changing performance and power requirements of the host.

<sup>&</sup>lt;sup>6</sup>8b/10b is an encoding scheme that takes 8 bits of data and transfers it using 10 bits. It is used to transmit data over some high-speed interfaces.

■ **Note** NVMe is frequently used in compute servers that demand peak performance. As a result, aggressive power management, particularly with states 5 and 6, may not be a good match.

NVMe is a relatively new technology. Power management of enterprise-class NVMe drives has not been a priority for many users or designs. Many of the initial enterprise offerings do not implement these power management states.

## **Power Delivery**

There are a large number of components within a server platform, and each of them requires power to provide their necessary function. Different components in the system have different requirements for the type of power that they receive. Some need high voltages, others low. Some are very sensitive to operating at a very specific voltage, whereas others are able to tolerate a range of voltages.

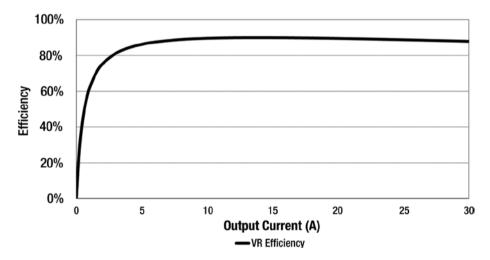

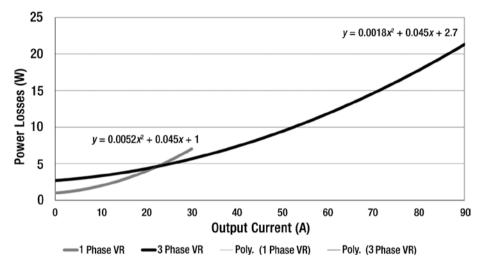

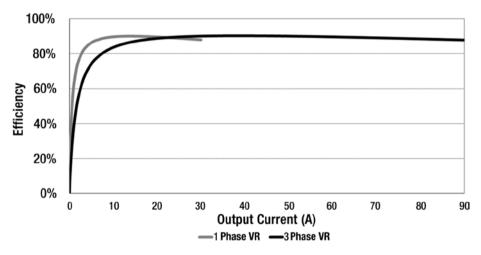

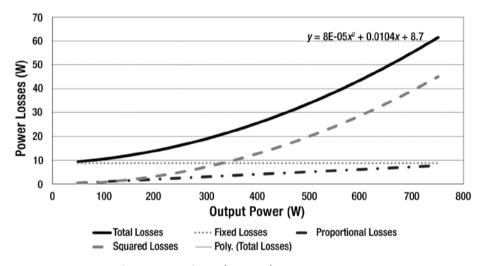

Since the type of power provided to a server system is similar to the power you get from your home's wall outlet, the system has many power converters to convert this AC (alternating current) voltage to the many specific DC (direct current) voltages needed by all its components. The conversion of this AC voltage to the required DC voltages consumes power, referred to as *losses* in the converter. The typical measure of these losses in the power converters is expressed as an *efficiency*. Efficiency is expressed as the ratio of the output power to the input power. Since the input power equals the output power plus the power losses of the converter, the efficiency can be expressed as the following equation:

$$\label{eq:efficiency} \begin{split} \textit{Efficiency} = & \frac{\textit{Output Power}}{\textit{InputPower}} = \frac{\textit{Output Power}}{\textit{Output Power} + \textit{Converter Power Losses}} \end{split}$$

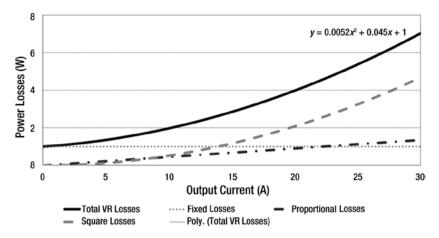

How efficiently these power converters convert power from higher voltages to the lower voltages that are required by the loads is critical to the overall efficiency of the system. Even in systems with the best converter efficiency, these losses can make up 10%–20% of the power in the system. At low system utilizations, they can contribute an even higher percentage of the power. This section provides an overview of these power converter losses, basics of the different type of power converters used in the system, the various elements of the power conversions that contribute to their losses, and special features to help reduce losses in these power converters.

### Overview of Power Delivery

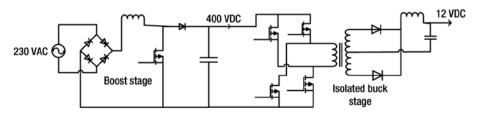

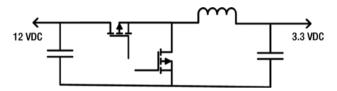

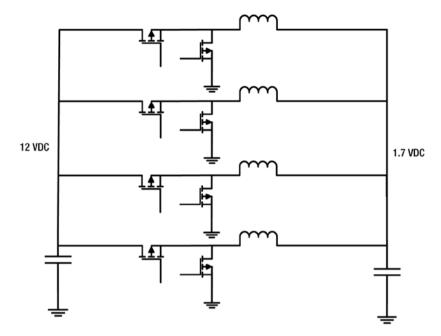

Figure 4-5 illustrates an example power converter block diagram for a standard dual processor system. Block diagrams like this are commonly found in motherboard schematics.

Figure 4-5. Dual socket power conversion block diagram

Power is first processed by a power supply and converted from AC to DC (see Table 4-21). The output DC power from the power supply is then converted to the various DC voltage levels required by different platform components (see Table 4-22). Power budgets must be determined for each component in the system so that sizing can be done at each stage of the power delivery network (see Table 4-23).

Table 4-21. Components in a Power Supply

| Component               | Туре                                                      | Typical Efficiency | Description                                                                                                                                                                                                                                    |

|-------------------------|-----------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power factor correction | Power converter<br>in system AC/DC<br>power supply        | ~98%               | This is a power conversion stage inside the system power supply whose primary function is to provide power factor correction. This is the first stage converter. It provides a 400 VDC output voltage to the second stage in the power supply. |

| Isolated DC/DC stage    | Power converter<br>in the system<br>AC/DC power<br>supply | ~97%               | This is a power conversion stage inside the system power supply whose primary functions are to provide safety isolation for the AC input and provide a regulated DC output voltage that can be used by the system.                             |

Table 4-22.

Types of DC/DC Power Converters

| Component           | Туре                                                                                | Typical Efficiency              | Description                                                                                                                                                                                                   |

|---------------------|-------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multi-phase<br>buck | DC/DC switching<br>power converter<br>on the<br>motherboard                         | 80-90%                          | Power converter used to provide high currents at low voltages. Frequently converts 12 V to 1–2 V.                                                                                                             |

| Buck regulator      | Simple DC/DC<br>switching power<br>converter on the<br>motherboard                  | ~90%                            | Simple converters used to power lower power devices on the motherboard. Typical inputs of 12 V/5 V/3.3 V converting to outputs of 5 V to <1 V.                                                                |

| Linear regulator    | Power converter<br>used to power<br>very low power<br>devices on the<br>motherboard | Output Voltage<br>Input Voltage | Very simple and low-cost converter that provides poor efficiency and therefore is used only for very low-power loads. Their efficiency is determined by the ratio of the output voltage to the input voltage. |

| <b>Table 4-23.</b> Pou | er Block Diagran | n—Loads |

|------------------------|------------------|---------|

|------------------------|------------------|---------|

| Component            | Description                                                                                                                                               |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cores, uncore, DIMMs | These loads in the system are the primary power consumers and provide the core computing capabilities of the system.                                      |

| LAN, PCH, USB, PCIe  | These are lower power loads in the system that provide input and output to the system compute capabilities.                                               |

| HDD                  | These are medium power loads that provide storage capabilities.                                                                                           |

| Active cooling       | These are medium power loads that are primarily axial fans<br>in the system. Other types of exotic cooling, such as liquid<br>cooling, are also possible. |

The block diagram contains switching power converters, linear regulators, and the loads. Almost all of the system power passes through three to four stages of power conversion to get from the 230 VAC input to the points of load. There are multiple reasons why the power passes through these series stages:

- The first step converts from AC to DC to provide power factor correction. Most digital circuits require DC power for operation.

- It is more efficient to transmit higher voltages over longer distances.

This is why power is kept at higher voltages as long as possible.

- Low-power loads are powered by linear regulators. While these

regulators are less efficient than more complex voltage regulators,

they also have lower cost due to their simple design and small

number of components. The loss in efficiency is small in the

overall power consumption.

- The easily accessible portions of the platform must not expose technicians to dangerous sources of electricity (such as the AC input).

**Note** Transmitting power using higher voltages is more efficient. Wires used for transmitting power have resistance in them. Power is consumed because of this resistance and is proportional to the square of the current (Watts =  $I^2R$ ). By increasing voltage at a fixed power, current is reduced, thus reducing these quadratic losses (Power =  $I^*R$ ).

It's not uncommon to see a system with a total of 25–30 power converters in the system and on the motherboard. There are a few reasons for these many converters:

- Power efficiency can be improved by adding more regulators in order to reduce I<sup>2</sup>R losses.

- Certain legacy functions and capabilities require specific voltage levels.

- System standard components (USB, HDD, PCIe adapters) require industry standard voltages that cannot be changed.

- Customized voltages are required for processors and other silicon devices in order to achieve high performance and power efficient designs.

#### **Power Converter Basics**

As discussed earlier, the system contains different types of power converters. Each of these has tradeoffs that can have a significant impact on the overall power efficiency of the platform.

First, energy can be transmitted either as AC (alternating current) or DC (direct current). Digital circuits require DC power to operate. AC power is commonly used to transmit power from power plants across the electrical grid because it is relatively easy (and inexpensive) to change AC voltages using transformers. AC power is used to distribute power within data centers as well, but it must be converted into DC power at some point in order to drive digital circuits.

AC/DC power conversion provides this mechanism. Different components in a platform require different voltages. DC/DC power converters change the voltage of DC power to match the requirements for each component. The main types of power converters used in standard server systems are boost converters, isolated buck converters, single and multiphase buck converters, and linear regulators.

### System AC/DC Power Supply

The first components in the node power delivery network, the boost converter and the isolated buck converter, are integrated into the power supply. The basic schematic for these converters are shown in Figure 4-6. It is important to understand the basic functions of these converters to grasp the tradeoffs between efficiency and features.

Figure 4-6. Example AC/DC power supply schematic

■ **Note** It is not a requirement that AC voltage be used as an input to a platform node and power supply. Other input voltages such as 380 VDC and 240 VDC are being used to help improve facility power distribution efficiency and availability. In these cases, the AC to DC conversion stage is not required and can be removed from the power supply to improve efficiency.

Both converters in the system AC/DC power supply are switching converters, which means MOSFETs are used to chop the input voltage into a square wave, and then they are filtered again to obtain a DC voltage. There is a PWM (pulse width modulation) controller that controls the duty cycle to maintain the required output voltage.

#### PSUs and the Boost Stage

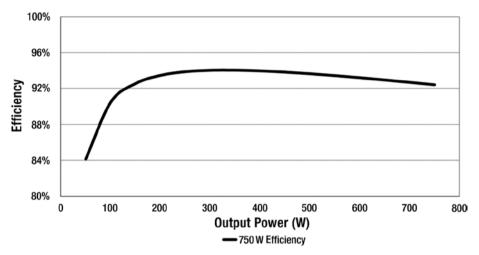

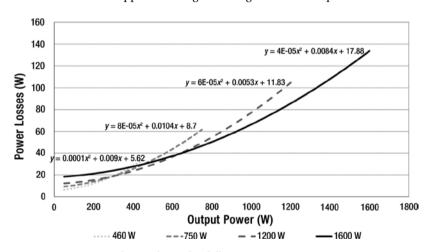

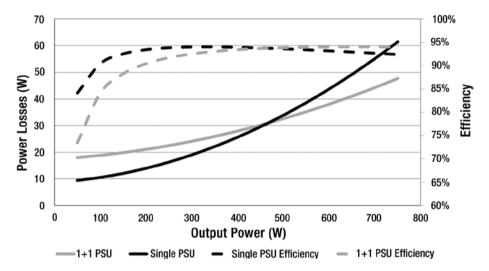

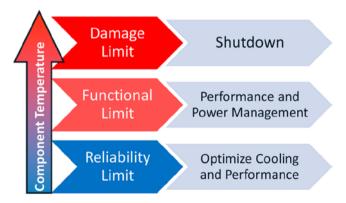

The boost converter in the power supply maintains a regulated voltage to the isolated buck stage of the power supply. The boost's main purpose is to wave-shape the input current to provide power factor (PF) correction and lower current harmonic distortion (ITHD), resulting in improved power efficiency. Good power supplies achieve PF > 0.99 and ITHD < 5%. Since a boost converter requires that the output voltage always be greater than the input voltage, you typically see a boost output voltage of ~400 VDC ( >  $110\% * 240 VAC * \sqrt{2} = 373 Vpeak$  ).