# A Low Power CMOS Micromixer for GHz Wireless Applications

Yue Wu<sup>1,2</sup>, Shenggao Li<sup>1</sup>, Mohammed Ismail<sup>1,2</sup>, Håkan Olsson<sup>2</sup>

<sup>1</sup>Analog VLSI Lab, The Ohio State University

205 Dreese Lab, 2015 Neil Ave.

Columbus, OH 43210, USA

<sup>2</sup> Radio Electronics Lab, Royal Institute of Technology,

Electrum 229, S-164 40 Kista, Sweden

hakan@ele.kth.se

Abstract

This paper presents a CMOS RF mixer with low power consumption and high linearity. The low power and high linearity is achieved with a class-AB input stage. Detailed analysis of the circuit has been given. The mixer is working at 2.44GHz for WCDMA system, with a power consumption less than 3 mW, it achieved 7.5 dB conversion gain, 4.6 dBm IIP3 and 13dB NF. Simulation results performed on HPADS has been presented, HP0.5 $\mu$  m CMOS process is used.

Keywords:

Down-Conversion Mixer, Class-AB mode, Conversion Gain, Intermodulation, Noise Figure, WCDMA, Wireless Systems

#### 1. INTRODUCTION

wuy, lisg, ismail@ee.eng.ohio-state.edu

In wireless communication systems, downconversion mixer plays an important role because it converts the radio frequency (RF) signal down to intermediate frequency (IF) or baseband frequency. The reason to convert signal down to lower frequency is that it is difficult to design high Q channel filter at RF frequency with reasonable low noise and power consumption. Because of the low  $g_m/I$  ratio inherent to MOS transistors, it is difficult to design low power MOS mixer with high gain, high linearity and good noise performance([1],[2],[3]). In [4], a new mixer structure called micromixer has been proposed for BJT, this topology is also very suitable for low power MOS mixer design. In this paper, a very low power MOS mixer is designed and simulated. The circuit

The original version of this chapter was revised: The copyright line was incorrect. This has been corrected. The Erratum to this chapter is available at DOI: 10.1007/978-0-387-35498-9\_57

L. M. Silveira et al. (eds.), VLSI: Systems on a Chip

<sup>©</sup> IFIP International Federation for Information Processing 2000

uses HP0.5 $\mu$ m technology, it can achieve 7.5 dB conversion gain, 4.6dBm IIP3 and 13dB Noise Figure with power consumpsion of only 3mW. Section 2 introduces mixer topology and performance parameters, followed by a detailed analysis of the class-AB input stage in section 3. In section 4, the design of the mixer and simulation results are presented, finally conclusion is summarized in section 5.

# 2. MIXER STRUCTURE AND PERFORMANCE PARAMETERS

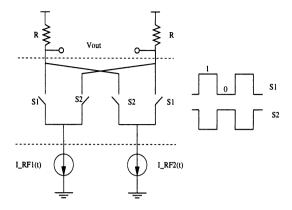

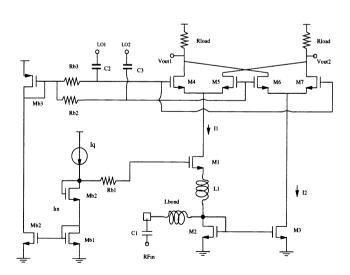

A commutating mixer can be divided into three stages as shown in Fig.1, i.e. the input stage, the switching stage and the load stage. The input stage is a transconductance stage that converts the input voltage to a current. For the downconversion mixer case, this part is working at RF frequency, so this stage must have enough transconductance at high frequency to translate the RF voltage signal efficiently to RF current signal. The second stage is the switching stage, which really performs the frequency translation through the commuting action of a NMOS common-source differential pair. The load stage is a transimpedance stage, it converts the switched current back into voltage.

The mixer shown in Fig.1 is a double-balanced commutating mixer. In the input stage, RF input voltage has been translated into currents which are represented by current sources  $I_{RF1}$  and  $I_{RF2}$ . If we assume ideal switch at the commutating stage, which means the switching activity will not affect the work of the input stage, and there is no current loss when the switch is on, then it is easy to get the output voltage as

$$V_{out}(t) = R[I_{RF1}(t) - I_{RF2}(t)][S_1(t) - S_2(t)]$$

(1.1)

where R is the load impedance of the output stage. After the Fourier Series Expansion of the last item of previous equation, we have

$$V_{out}(t) = Rg_m v_{rf}(t) \frac{4}{\pi} cos(\omega_{LO}t) - Rg_m v_{rf}(t) \frac{4}{3\pi} cos(3\omega_{LO}t) + (1.2)$$

The first item in the previous equation is the desired downconverted signal at the output of the mixer, higher order items will be greatly attenuated by the low pass characteristic of the circuits or by the following filters. For a single-side band downconversion mixer, the conversion gain is

$$Gain = \frac{2}{\pi} Rg_m \tag{1.3}$$

Note that in this equation, the conversion gain is not related to LO amplitute, this is because we assume ideal switch for the switching stage. In real design,

when LO is too small, the transistors can not be cut off completely, there will be gain loss and high noise. LO signal can not be too large either, when it is the case, it may force the input stage into triode region and will cause gain loss too.

In the above derivation, we assume that the differential currents are linear to the input voltage, i.e.  $I_{RF1}(t)-I_{RF2}(t)=g_mv_{rf}(t)$ . Unfortunately, in most cases this is only an approximation which is valid when input signal is small. When input signal is strong or there exists large interference signals, we have to consider the nonlinear effects of the input stage, this is what IP3(third order intercept point) accounts for. If the input signal is a two tone signal,  $v_{rf}(t)=A(cos(\omega_1 t)+cos(\omega_2 t))$ , and the differential current is as following

$$I_{RF1}(t) - I_{RF2}(t) = \alpha_1 v_{rf}(t) + \alpha_2 v_{rf}^2(t) + \alpha_3 v_{rf}^3(t) + \cdots$$

(1.4)

we can get the amplitute of frequency component at  $2\omega_1-\omega_2$  and  $2\omega_2-\omega_1$ , which are the result of third order intermodulation, to be equal to  $\frac{3}{4}|\alpha_3|A^3$ . If we set it equal to the fundamental frequency output, then the IIP3( 3rd order Input Intercept Point) will be  $A_{IP3}^2=4\alpha_1/3\alpha_3$ [5]. Since mixer is the stage following the LNA, the input signal from antenna has been amplified, so the linearity requirement of mixer is much higher than LNA, normally it will be about -5dBm.

A third important parameter is the Noise Figure(NF). Even though the effect of mixer noise can be attenuated by the gain of LNA, it is desirable to have low noise mixer to relax the design of LNA. The calculation of mixer NF is complex because the input and output noise are in different frquency domain, a systematic analysis can be found in [6]. If the switch is fast enough, the noise will be dominated by the input stage.

From the above introduction, it is clear that the input stage plays an important role in that it can determine the gain, linearity and noise performance of a mixer. There always exist tradeoffs in RF circuit design among those parameters, the following section will introduce a new input stage which can achieve low power, high linearity and high gain simultaneously.

#### 3. CLASS-AB INPUT STAGE

Recently, a new input stage has been proposed([4]) for bipolar mixer, and mixer with this kind of input is named as Micromixer according to the author of that paper. The key point of this structure is the class-AB behavior of the input stage which uses a common emitter transistor and a common base transistor to generate the differential input current. This idea can be used in CMOS mixer design, following is the analysis and design of the CMOS Micromixer.

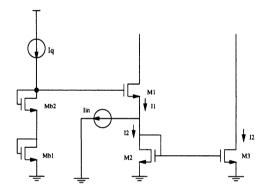

Fig.2 shows the input stage of the Micromixer, it is composed of the biasing transistor Mb1, Mb2 and M2, the common gate transistor M1 and common source stage M3. If we assume that the two biasing transistors have the same

size, M1-M3 also have the same size, with biasing current is  $I_q$ , then according to Fig.2, there exists a translinear loop Mb1, Mb2, M1 and M2, so we have

$$V_{gs,1} + V_{gs,2} = V_{gs,b1} + V_{gs,b2} (1.5)$$

If all these four transistors are working in saturation region, and we assume that all the transistors have the same threshold voltages,  $V_t$ , then we have

$$\sqrt{I_1} + \sqrt{I_2} = 2\sqrt{\frac{k_1}{k_0}}\sqrt{I_q} \tag{1.6}$$

where  $k=\frac{1}{2}\mu C_{ox}\frac{W}{L}$ . Since we also have  $I_2$ - $I_1$ = $I_{in}$ , so it is easy to derive currents  $I_1$  and  $I_2$  as following

$$I_1 = \lambda (1 - \frac{I_{in}}{4\lambda})^2, I_2 = \lambda (1 + \frac{I_{in}}{4\lambda})^2$$

(1.7)

where  $\lambda = (k_1/k_0)I_q$  is a constant determined by the size ratio of the input to biasing transistors and quiescent current.

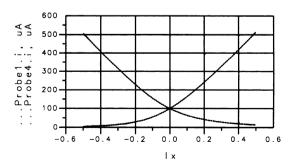

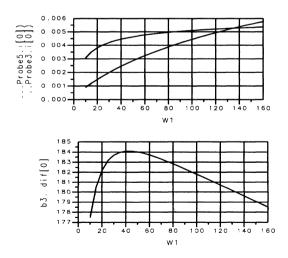

From the above equation, when  $I_{in}=0$ ,  $I_1$  and  $I_2$  will have the same value  $(k_1/k_0)I_q$ . When  $I_{in}$  increase, then  $I_1$  will decrease and  $I_2$  will rise or vice versa. The current relationship is shown in Fig.3, it is clear that this stage is working at class-AB status and will have low power consumption compared with differential pair.

Even though neither current is linear with the input current  $I_{in}$ , the difference between  $I_1$  and  $I_2$  is still equal to  $I_{in}$ . Note that the above equations are valid only when the input current  $I_{in}$  is smaller than  $4(k_1/k_0)I_q$ . Otherwise, according to the equations, one of the input transistor will cut off (i.e.  $I_1$  or  $I_2$  will be zero) and the derivation is no longer valid.

According to equation(3), it is important to determine the transconductance of the input stage because it determines the conversion gain of the mixer. Since we have

$$V_{RF} = V_{gs,1} = V_q + \frac{\sqrt{k_0}}{4k_1\sqrt{I_q}}I_{in}$$

(1.8)

where  $V_q = V_t + \sqrt{I_q/k_0}$  is the DC voltage of biasing transistors, the large signal transconductance  $g_m$  will be

$$g_m = \frac{1}{R_{in}} = \frac{1}{\frac{\partial V_{RF}}{\partial I_{in}}} = \frac{4k_1\sqrt{I_q}}{\sqrt{k_0}}$$

(1.9)

It turns out that the large signal input impedance is a constant value which is determined by the size ratio and biasing current, or in other words, the input current difference (i.e.  $I_{in} = I_1 - I_2$ ) is a linear function to the input voltage

(i.e.  $V_{RF}$ ) as long as  $I_{in}$  is less than  $4(k_1/k_0)I_q$ . This is very important characteristic of this input stage, compared with the result of [4], the large signal input current of bipolar Micromixer is not a really linear function to the input voltage, so we can expect higher linearity from the CMOS Micromixer.

When we compare the transconductance with the common source differencial pair, which is the input stage of Gilbert mixer, we can also find the advantage in both linearity and gain. A differential pair with biasing current  $I_q$  and input voltage  $V_{RF}$ , the differential current will be[7]:

$$I_{in} = I_1 - I_2 = kV_{RF}\sqrt{\frac{2I_q}{K} - V_{RF}^2}$$

(1.10)

This equation is valid if  $V_{RF}$  is smaller than  $\sqrt{I_q/k}$ . The transconductance of the differential pair is not linear even when the input signal is small as

$$g_{m} = \frac{\partial I_{in}}{\partial V_{RF}} = \frac{2I_{q} - 2kV_{RF}^{2}}{\sqrt{\frac{2I_{q}}{k} - V_{RF}^{2}}}$$

(1.11)

From the above equation, it is clear that the transconductance of the common source differential pair is a function of the input voltage signal, this means the degradation of linearity. Fig.4 shows the simulation result of the normalized large signal transconductance of both class-AB input stage and the differential pair, it can be seen the transconductance of class-AB input stage keep almost the same till the input signal is very large, while the transconductance of differential pair keeps on decreasing when input signal increases. The highest transconductance of differential pair is achieved at the point when input voltage is zero, which is  $g_{m,max} = \sqrt{2kI_q}$ . If we set  $k_1 = k_0 = k$  in equation(13), then the transconductance of the class-AB input stage is  $g_m = 4\sqrt{kI_q}$ . So with the same biasing current and transistor sizes, the micromixer will have  $2\sqrt{2}$  or about 9dB gain increase over the differential pair.

It is complex to calculate the noise figure of mixer, but in order to gain some insight of the noise performance, we can just calculate the noise of the input stage because Micromixer's other stages are the same as Gilbert mixer. The input stage's noise is determined by the three transistors M1, M2, and M3. The noise from biasing circuit can be attenuated through large resistance as shown is Fig.5. Then we have the noise current PSD(Power Spectrum Density) of each transistor  $\overline{I_n^2} = 4kT\gamma g_m$ , when we mirror them back at the input stage, it should be divided by the square of the transconductance from input to that transistor. So we have the equivalent noise voltage at the input

$$\overline{V_{n,add}^2} = \overline{V_{n,1}^2} + \overline{V_{n,2}^2} + \overline{V_{n,3}^2} = \frac{12kT\gamma}{q_m}$$

(1.12)

where we assume three transistors have the same transconductance. The noise figure of the input stage can be

$$NF = 1 + \frac{\overline{V_{n,add}^2}}{4kTR_s} = 1 + \frac{3\gamma}{g_m R_s}$$

(1.13)

while for differencial pair, the noise figure can be  $NF=1+2\gamma/g_mR_s$ , so there is some degradation of noise performance for the class-AB input stage. From the above equation, it can be found that large transistor transconducance will be desired for noise performance, but it will require more power or generate large parasitic capcitance.

## 4. IMPLEMENTATION OF A CMOS MICROMIXER

A CMOS micromixer using HP0.5 $\mu$ m technology has been designed, the circuit is shown in Fig.5. This mixer is designed to work at 2.44GHz in a direct downconversion system. The quiescent current of the input stage is about  $450\mu$ A with 3V supply, the total power consumpsion is less than 3mW. As shown in the figure, Mb1, Mb2, and M1-M3 is the class-AB input stage, M4-M7 is the switching transistors. The biasing of switching transistors is provided by Mb2 and Mb3. Rb1-Rb3 is large resistor about 3 KOhm, the purpose of these resistors is to attenuate the noise of biasing circuit appearing at the RF and LO input. L1 is a spiral inductor, it is modeled as [8]. Lbond is bondwire inductor, it is provided by package model. Rload is the output load impedance, its value will determine the conversion gain, higher value will have higher gain. But since it also determine the DC level of the output, it can not be too large because it may force M1-M3 work in triode region. The size of M1-M3 is determined by conversion gain requirement and power consumption. From the above analysis, the higher the biasing current, the higher the gain and linearity, but once the power consumption is set, there exist some optimum point for the biasing and sizes of M1-M3. RF and LO signals are AC coupled through capacitors C1-C3. The RF input matching is very simple, taken the package model into account, we only need one series capacitor C1 to tune the matching, simulation result show the S11 can be as less than -20 dB. Differential LO signal comes from the LO buffer which can provide at least -10 dBm input power for good performance.

It is important to make the quiescent current in the two branches equal, this is because any mismatch in the quiescent currents will directly translated into LO leakage to the IF output. According to equation(1), if there exists mismatch  $\Delta I_q$ , the output voltage will be

$$V_{out}(t) = R[I_{RF1}(t) - I_{RF2}(t)][S_1(t) - S_2(t)]$$

=  $R\Delta I_q[S_1(t) - S_2(t)] + Rg_m v_{rf}(t)[S_1(t) - S_2(t)]$  (1.14)

the first item is the LO leakage to the output of the mixer. Because of the substrate effect, we should tune the size ratio of M1,M2,M3 to eliminate the current mismatch.

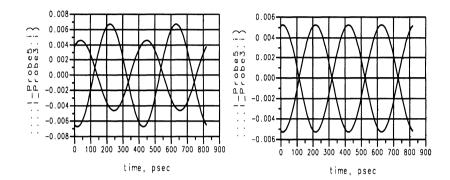

Inductor  $L_1$  is a spiral inductor with value of about 2nH, the purpose of this inductor is to adjust the phase difference of the two differential branches. Since from the input point to the two output points of the input stage, the parasitic capacitance will cause different phase shift of the two RF currents, the phase difference is more than 180 degree as shown in Fig.6(it also cause different transconductance). This will cause gain loss because of the following

$$sin(\omega t - \varphi) - sin(\omega t + \pi) = (1 + cos\varphi)sin(\omega t) - sin\varphi cos(\omega t).15$$

the gain loss will be

$$Loss = 10log(\frac{2}{1 + cos\varphi}) = 3 - 10log(1 + cos\varphi)dB \qquad (1.16)$$

With the inductor adjustment, we can add some phase delay to one branch so that it is possible to adjust phase difference to be 180 degree. The method is to change the size of M1 as shown in Fig.7, we find when W1 is about  $135\mu m$ , the two branches will have 180 degree phase difference and equal amplitute.

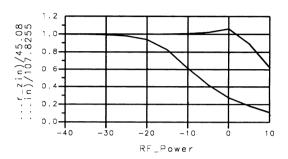

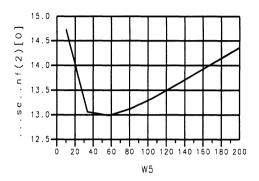

According to [5], there exists an optimum size of the switching transistor for the noise performance. Sweeping the size in HPADS simulation, we get the optimum size is about  $60\mu$ m which can achieve 13dB Noise Figure as shown in Fig.8. Fig.9 shows the conversion gain and IIP3 to be 7.5dB and 4.6 dBm respectively. It also shows the variation of NF with LO input power. When LO input power is low, both switching transistor will on and the noise from these transistors will dominate the noise figure. When LO input is large enough, the input stage will dominate, so the decrease of NF becomes much slower as shown in the figure. In order to achieve acceptable noise performance, the LO input must be at least -10dBm.

# 5. CONCLUSION

Through analysis of a class-AB input stage, it is clear that it is very suitable for high linearity low power MOS mixer design. Simulation of a CMOS micromixer can achieve 4.6dBm IIP3 and 7.5dB conversion gain consuming less than 3mW. The circuit has been layout and will be fabricated, the measurement result will come out soon.

## 6. REFERENCES

[1]A. Vauhkonen, K.J. Grahn"A 12-mW Wide Dynamic Range CMOS Front-End for a Portable GPS Receiver" *Ananlog Integrated Circuits and Signal Processing*, pp. 33-42, March, 1998.

| Specifications     | Results |

|--------------------|---------|

| Power Dissipation  | <3mW    |

| RF frequency       | 2.44GHz |

| RF input power     | -50dBm  |

| LO input frequency | 2.44GHz |

| LO input power     | -5dBm   |

| Conversion Gain    | 7.5dB   |

| IIP3               | 4.6 dBm |

| SSB NF             | 13dB    |

Table 1 Performance Summary

- [2]F. Piazza, Q. Huang, "A 1.57-GHz RF Front-End for Triple Conversion GPS Receiver", *IEEE J. of Solid State Circuit*, vol. 33, no. 2, pp. 202-209, Feb., 1998.

- [3]K. L. Fong and R. G. Meyer, "A Class AB Monolithic Mixer for 900Mhz Applications," *IEEE J. of Solid State Circuits*, vol. 32, no. 8, pp. 1166-1172, August, 1997.

- [4]B. Gilbert, "The Micromixer: a highly linear variant of the Gilbert mixer using a bisymmetric class-AB input stage" *IEEE J. of Solid State Circuits*, vol. 32, no. 9, pp. 1412-1423, September, 1997.

- [5]B. Razavi, "RF microelectronics," Prentice-Hall, New Jersey, 1998

- [6] C.D. Hull and R. G. Meyer, "A systematic approach to the analysis of noise in mixer," *IEEE Trans. CAS*, vol. 40, no. 12, pp. 909-919, December, 1993.

- [7] M. Ismail and T. Fiez, "Analog Integrated Circuit and Signal Processing," McGraw-Hill, New York, 1993

- [8]N. Nguyen, R. Meyer"Si IC-Compatible Inductors and LC Passive Filters" *IEEE J. of Solid State Circuits*, vol. 25, no. 4, pp. 1028-1031, August, 1990.

Figure 1 Commuting Mixer Structure and Switching Signal

Figure 2 The Class-AB input stage

Figure 5 Low power high linearity CMOS Micromixer

Figure 9 Conversion gain, IIP3 and Noise performance