# A 3 V 110 $\mu$ W 3.1 ppm/°C curvature-compensated CMOS bandgap reference

Xiaokang Guan  $\cdot$  Xin Wang  $\cdot$  Albert Wang  $\cdot$  Bin Zhao

Received: 10 December 2008/Revised: 8 June 2009/Accepted: 12 June 2009/Published online: 26 June 2009 © The Author(s) 2009. This article is published with open access at Springerlink.com

**Abstract** This paper presents design of a high-precision curvature-compensated bandgap reference (BGR) circuit implemented in a 0.35  $\mu m$  CMOS technology. The circuit delivers an output voltage of 1.09 V and achieves the lowest reported temperature coefficient of  $\sim 3.1$  ppm/°C over a wide temperature range of [ $-20^{\circ}\text{C}/+100^{\circ}\text{C}$ ] after trimming, a power supply rejection ratio of -80 dB at 1 kHz and an output noise level of 1.43  $\mu V$   $\sqrt{Hz}$  at 1 kHz. The BGR circuit consumes a very low current of 37  $\mu$ A at 3 V and works for a power supply down to 1.5 V. The BGR circuit has a die size of 980  $\mu$ m  $\times$  830  $\mu$ m.

**Keywords** Bandgap reference · CMOS · Temperature coefficient · Power supply rejection ratio

#### 1 Introduction

Bandgap Reference (BGR) circuits are basic functional circuit blocks widely used in many integrated circuit (IC) chips, such as, power management, temperature sensors, data converters, voltage regulators and memories, because of its excellent temperature stability and insensitivity to supply voltage. Since introduced in 1970s, BGR has been the most popular solution for precision reference source

nearly temperature-independent output voltage. Typical output voltage of BGR is about 1.2 V at room temperature, which is close to the bandgap voltage of silicon. However, for conventional BGR circuits, the higher-order temperature dependency in  $V_{\rm EB}$  still exists in output voltage. In order to further lower the temperature coefficient (TC), several curvature compensation schemes [1–4] have been reported to compensate the higher-order temperature dependency and to reduce the output voltage variation over the temperature.

This paper presents design of a current-mode curvature-compensated BGR fabricated in a commercial 0.35  $\mu$ m CMOS technology. Several design issues were carefully

circuits. The basic idea of BGR in CMOS technology is to

add a proportional to absolute temperature (PTAT) voltage

to the emitter-base voltage  $(V_{EB})$  of a parasitic pnp tran-

sistor, so that the first-order temperature dependency in

$V_{\rm EB}$  is compensated by the PTAT voltage, resulting in a

This paper presents design of a current-mode curvature-compensated BGR fabricated in a commercial 0.35 µm CMOS technology. Several design issues were carefully studied to optimize the critical BGR specifications, such as temperature coefficient, power supply rejection ratio (PSRR) and power consumption. Section 2 explains the design details. Section 3 discusses the experimental results flowed by conclusions in Sect. 4.

### 2 BGR circuit design

### 2.1 Current mode BGR with curvature compensation

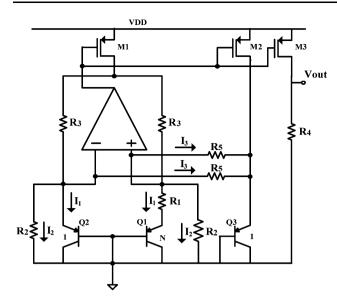

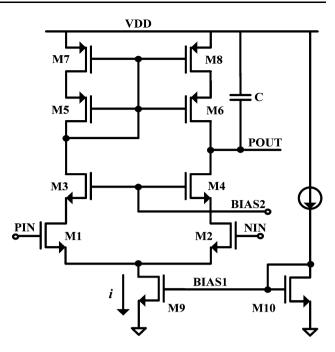

Current mode BGR [5] was originally introduced to implement a voltage reference circuit when power supply is <1.2 V. Figure 1 shows a simplified curvature-compensated circuitry based upon the current mode scheme that is capable of further reducing the BGR output voltage variation against temperature [6]. By connecting a resistor

X. Guan · B. Zhao Freescale Semiconductors, Inc., Irvine, CA, USA

X. Guan  $\cdot$  X. Wang  $\cdot$  A. Wang ( $\boxtimes$ ) Department of Electrical Engineering, University of California, Riverside, CA 92521, USA

e-mail: aw@ee.ucr.edu URL: http://lics.ee.ucr.edu

Fig. 1 Simplified schematic of current mode BGR with curvature compensation, where parasitic pnp transistors in CMOS are used

between the emitter and base of BJT transistor Q2, an extra current of  $I_2 = \frac{V_{\rm EB_{Q2}}}{R_2}$  is obtained, which is added to the PTAT current,  $I_1 = \frac{V_{\rm EB_{Q2}} - V_{\rm EB_{Q1}}}{R_1}$ , to generate a current with low sensitivity to the temperature variation.

From Fig. 1, given  $\left(\frac{W}{L}\right)_{M1} = 2\left(\frac{W}{L}\right)_{M3}$ , the  $V_{\text{out}}$  can be derived as:

$$\begin{split} V_{\text{out}} &= (I_1 + I_2 + I_3)R_4 \\ &= \left(\frac{V_{\text{EB}_{Q2}} - V_{\text{EB}_{Q1}}}{R_1} + \frac{V_{\text{EB}_{Q2}}}{R_2} + \frac{V_{\text{EB}_{Q2}} - V_{\text{EB}_{Q3}}}{R_5}\right)R_4 \\ &= \left(\frac{V_T \ln N}{R_1} + \frac{V_{\text{EB}_{Q2}}}{R_2} + \frac{V_{\text{EB}_{Q2}} - V_{\text{EB}_{Q3}}}{R_5}\right)R_4 \end{split} \tag{1}$$

where  $V_T = \text{KT}/q$  and N is emitter area ratio of the BJT transistor Q1 and Q2. In (1),  $I_1 = \frac{V_{\text{EB}_{Q2}} - V_{\text{EB}_{Q1}}}{R_1} = \frac{V_T \ln(N)}{R_1}$  is the PTAT current, which can compensate the first-order temperature dependence in  $I_2$ . Therefore, sum of  $I_1$  and  $I_2$  is almost constant over the temperature. Furthermore, the nonlinear relationship between  $V_{\text{EB}}$  and temperature can be expressed as [7]:

$$V_{\text{EB}}(T) = V_{\text{G}}(T) - \left[V_{\text{G}}(T_{\text{r}}) - V_{\text{EB}}(T_{\text{r}})\right] \frac{T}{T_{\text{r}}}$$

$$- (\eta - m)V_{T} \ln\left(\frac{T}{T_{\text{r}}}\right) \tag{2}$$

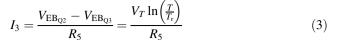

where  $V_G(T)$  is the bandgap voltage of Si as a function of temperature,  $T_r$  is the reference temperature,  $\eta$  is a temperature constant dependent on technology and m is the order of the temperature dependence of the collector current. Since the emitter currents of Q2 and Q3 are PTAT and temperature-independent, respectively, the third current term in (1) can be expressed as:

where the term of  $\frac{V_T \ln(T/T_t)}{R_5}$  can provide corrective current to compensate the higher-order temperature dependency in  $I_2$ . The value of  $R_5$  is properly chosen for optimum curvature compensation as:

$$R_5 = \frac{R_2}{(\eta - 1)} \tag{4}$$

Theoretically, by properly adjusting the ratios of  $R_1/R_2$  and  $R_5/R_2$ , one can obtain a simplified expression of the  $V_{\text{out}}$  as:

$$V_{\text{out}} = V_{\text{G}}(T) \frac{R_4}{R_2} \tag{5}$$

It is readily observed from (5) that the variation of  $V_{\rm out}$  against the temperature originates from the bandgap voltage  $V_{\rm G}(T)$  only. Hence, further reduction the output voltage variation against temperature requires an accurate measurement and expression of  $V_{\rm G}(T)$ .

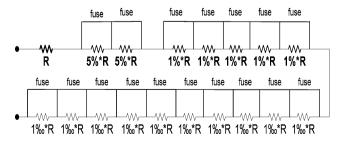

# 2.2 Resistor trimming network and trimming methodology

Due to inevitable process variation and inaccuracy in device model of the parasitic pnp transistors, a fine resistor trimming network is necessary to achieve optimal temperature performance. Implementation of an accurate trimming network for  $R_1$ ,  $R_2$  and  $R_5$  in this design is shown in Fig. 2.

In Fig. 2, the value for *R* is selected by circuit simulation. It is clearly observed that the resistor value can be increased by 16% with step of 1‰ of *R* by cutting off the fuses. Such trimming resolution is high enough to achieve the optimal temperature performance. It is noted that MOS switch might replace fuse for trimming purpose in general, which, however, has significant turn-on resistance that adversely affects the tuning accuracy desired for high-performance BGR.

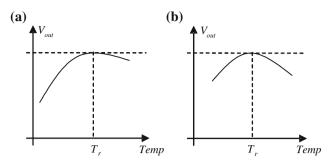

The proper resistor network trimming method is given below using the output voltage versus temperature curves

Fig. 2 An accurate resistor trimming network for  $R_1$ ,  $R_2$  and  $R_5$

**Fig. 3** a  $V_{\text{out}}(T)$  curve after  $R_1$  and  $R_2$  trimming; **b**  $V_{\text{out}}(T)$  curve after  $R_5$  trimming

obtained from a two-step trimming procedure illustrated in Fig. 3.

In the first step trimming, the ratio of  $R_1$  and  $R_2$  is finetuned to compensate the first-order temperature dependency in  $V_{\rm EB_{Q2}}$  and to make the highest output voltage point occur around the reference temperature  $T_{\rm r}$ , as shown in Fig. 3(a). In the second step trimming, accurate trimming of  $R_5$  is conducted for higher-order compensation with the goal of achieving a symmetrical bell shape  $V_{\rm out}(T)$  curve around the  $T_{\rm r}$ , which is desired to achieve the lowest temperature coefficient, as illustrated in Fig. 3(b).

#### 2.3 Power supply rejection ratio (PSRR)

For the BGR circuit shown in Fig. 1, the power supply rejection ratio (PSRR) can be derived as:

$$PSRR = \left| \frac{v_{\text{out}}}{v_{\text{dd}}} \right| \approx \left| c \frac{1 - A_{\text{dd}}}{A} \right| \tag{6}$$

where c is a constant dependent on the values of  $R_1$ – $R_4$  and transconductance of Q1 and Q2 that is given as:

$$c = R_4 \frac{2R_3 + (1/g_{\text{mQ2}})//R_2 + (R_1 + 1/g_{\text{mQ1}})//R_2}{R_3[(R_1 + 1/g_{\text{mO1}})//R_2 - (1/g_{\text{mO2}})//R_2]}$$

(7)

$A_{\rm dd}$  and A in (6) are power gain and open-loop gain of the operational amplifier, respectively, and  $A_{\rm dd}$  is expressed as:

$$A_{\rm dd} = \frac{\nu_{\rm output \, of \, Op-Amp}}{\nu_{\rm dd}} \tag{8}$$

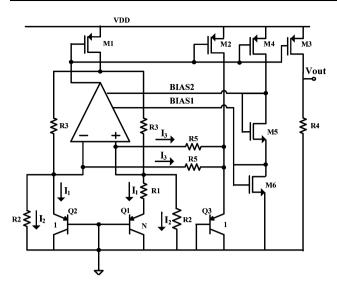

Equation 6 clearly suggests that a large open-loop gain of the Op Amp will improve PSRR performance of BGR circuit. However, large A may also cause stability problem. Alternatively, one may choose to make the power gain  $A_{\rm dd}$  as close to unity as possible without increasing the open-loop gain to achieve lower PSRR, which is a unique design technique introduced in this work where a large capacitance is placed between the output node of Op-Amp and the power supply to ensure a unity  $A_{\rm dd}$ ,

Fig. 4 New unity-A<sub>dd</sub> Op-Amp schematic used in the BGR circuit

especially at high frequency, hence achieve the lowest PSRR ratio. This novel design concept can be understood using the Op-Amp schematic shown in Fig. 4.

Assume that the bias current does not vary with  $v_{\rm dd}$ , the power gain  $A_{\rm dd}$  would be close to unity around DC. However, the  $A_{\rm dd}$  starts to roll off as frequency increases when the equivalent impedance of  $C_{\rm gdM6}$  of M6 is comparable to the DC resistance seen between VDD and POUT. Adding the capacitor C solves this problem. The power gain of the Op-Amp at high frequency region can be derived as:

$$A_{\rm dd}(\omega) = \frac{g_{\rm mM4} R_{\rm oM4} R_{\rm oM2}}{g_{\rm mM4} R_{\rm oM4} R_{\rm oM2} + \frac{1}{j_{\omega}(C + C_{\rm edM6})}}$$

(9)

where  $g_{\rm mM4}$  is transconductance of transistor M4; and  $R_{\rm oM4}$  and  $R_{\rm oM2}$  are output resistance of M4 and M2, respectively. From (9), it is readily observed that a large C value is desired to ensure magnitude of  $A_{\rm dd}$  close to unity. The capacitor C is also used to achieve the required frequency compensation for the Op-Amp circuit block. The Op-Amp performance can be further improved by eliminating the negative impact depicted in (10), which is associated with the non-ideal current source in practical circuit:

$$A_{\rm dd} = 1 - \frac{i/2}{v_{\rm dd}g_{\rm mM7}} \tag{10}$$

where i is ripple in the tail current source due to  $v_{\rm dd}$ . Equation 10 clearly indicates that the fluctuation in the

Fig. 5 BGR self-biased Op-Amp circuit in this design

Table 1 Op-Amp performance summary

| Parameter              | Value    |

|------------------------|----------|

| DC gain                | 103 dB   |

| Gain-bandwidth product | 1.07 MHz |

| Phase margin           | 102°     |

| Current consumption    | 2.4 μΑ   |

non-ideal tail current would drive the  $A_{\rm dd}$  away from its preferred unity value. In order to suppress the undesired i variation effect, the curvature-compensated current generated by BGR circuit itself is used to bias the Op-Amp block in this design, as shown in Fig. 5. Careful design of the telescopic Op-Amp results in the optimal performance as summarized in Table 1. Simulation study shows that using self-biasing scheme, the PSRR can be reduced by 20 dB, compared to the BGR circuit with the Op-Amp biased traditionally.

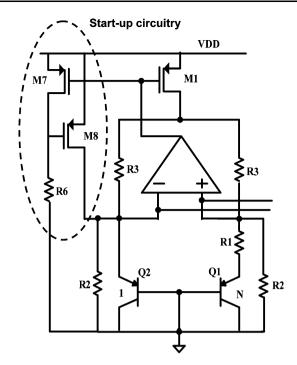

# 2.4 Start-up circuit

The Star-up circuit used in this design is shown in Fig. 6. The start-up circuit operates as following: if the current in Q2 and  $R_2$  is zero, the p-channel current sources (M1 and M7) are off. The gate of M8 is then pulled down to ground, hence injecting a significant current into Q2 and  $R_2$ . Once the circuit starts up, current in M7 and  $R_6$  will cause the gate potential of M8 to increase and approach VDD, which, in turn, turns off the startup circuit. The same start-up scheme is also used for the Op-Amp biasing circuit.

Fig. 6 Start-up circuit for the BGR in this work

# 3 Start-up circuitry

# 3.1 Experimental verification

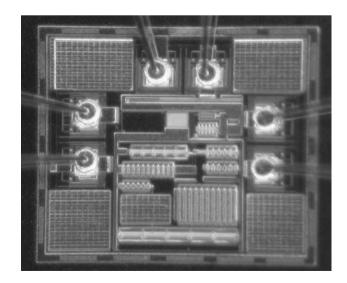

This curvature-compensated BGR circuit is designed and fabricated in a commercial 0.35  $\mu m$  CMOS technology. Extreme care was excised to ensure minimized resistor mismatching and Op-Amp offset voltage. Figure 7 shows the die photo of the BGR circuit with bonding pads and wires. The die size of the BGR circuit is 980  $\mu m \times 830~\mu m$  including bonding pads.

Fig. 7 Die photo of the BGR circuit in this work

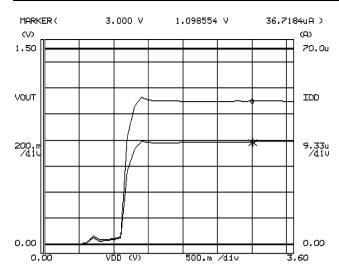

Fig. 8 Measured  $V_{\rm out}$  and total current consumption for the BGR circuit

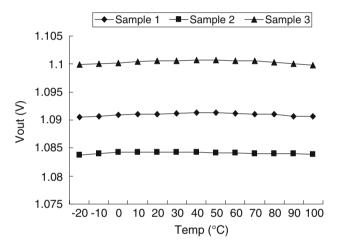

Fig. 9 Measured temperature variation for three BGR circuit samples

Testing results of packaged samples in ceramic DIP with removable lid are presented below. Die testing was somewhat affected by parasitic probing resistance. Full measurement was conducted for this BGR circuit over a wide temperature range from -20 to  $+100^{\circ}$ C. Figure 8 gives the measured output voltage  $V_{\rm out}$  and total current consumption, showing an output voltage of around 1.09 V and a very low current of only 37  $\mu$ A at a supply of  $V_{\rm DD}=3$  V, respectively. The lowest working supply voltage for this BGR circuit is 1.5 V. Figure 9 shows measured  $V_{\rm out}$  variation over wide temperature range of  $[-20^{\circ}\text{C/}+100^{\circ}\text{C}]$ . The maximum measured variation of  $V_{\rm out}$  is merely 0.4 mV over the full  $[-20 + 100^{\circ}\text{C}]$  temperature range after trimming, which translates into a very low TC of  $\sim 3.1$  ppm/°C in the worst case.

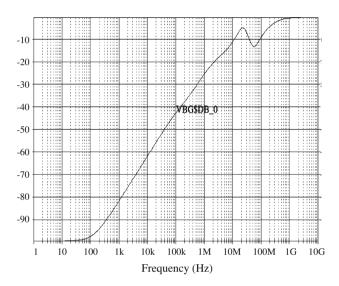

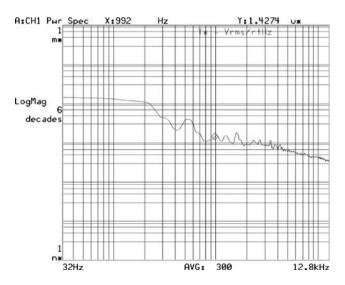

Figure 10 shows measured PSRR results of the BGR circuit that achieves a low PSRR of less than -80 dB at 1 kHz. Figure 11 shows the measured noise performance for the BGR circuit, which achieves a low output noise of about 1.43  $\mu$ V  $\sqrt{\text{Hz}}$  at 1 kHz that is mainly attributed to the Flicker noise generated by the MOS transistors in the circuit (e.g., M1 and M3 in Fig. 1; M1, M2, M7 and M8 in Fig. 6). The measured performance of the new BGR circuit is summarized in Table 2 for comparison with the state-of-art designs, which indicates that this design achieves the lowest worst case TC compared with reported works in similar CMOS technologies across similarly wide temperature ranges.

Fig. 10 Measured PSRR results for the BGR circuit

Fig. 11 Measured noise output of the BGR circuit

Table 2 Comparison of curvature-compensated Bandgap reference circuits

|                        | This work        | Reference [8] | Reference [9]    | Reference [10] |

|------------------------|------------------|---------------|------------------|----------------|

| Technology (µm CMOS)   | 0.35             | 2             | 0.6              | 0.35           |

| $V_{\text{out}}$ (V)   | 1.09             | 0.595         | 1.142            | 1.112          |

| $VDD_{min}(V)$         | 1.5              | 1.1           | 2                | 1.5            |

| DC Current (µA)        | 36.7             | 15            | 22               | 55             |

| Temperature Range (°C) | -20/+100         | -15/+90       | 0/+100           | +25/+100       |

| TC (ppm/°C)            | 3.1              | 20            | 5.3              | 10             |

| PSRR                   | -80  dB at 1 kHz | N/A           | -20  dB at 1 kHz | N/A            |

#### 4 Conclusion

This paper reports design and implementation of a current mode curvature-compensated BGR in a 0.35  $\mu m$  CMOS technology. The circuit features BGR self-biased Op-Amp, unity power gain technique to achieve low PSRR and resistor trimming for low temperature coefficient. Measurement results show that the BGR circuit delivers an output voltage of 1.09 V, achieves the lowest reported worst case TC of 3.1 ppm/°C over a wide temperature range of [-20°C/+100°C] and power consumption of 37  $\mu A$  at 3.3 V, a low PSSR of less than -80 dB at 1 kHz, and a low output noise of 1.43  $\mu V$   $\sqrt{Hz}$  at 1 kHz. The BGR circuit has a die size of 980  $\mu m$   $\times$  830  $\mu m$  and works for a power supply down to 1.5 V.

**Acknowledgments** The authors thank AKM for project sponsorship and design fabrication.

**Open Access** This article is distributed under the terms of the Creative Commons Attribution Noncommercial License which permits any noncommercial use, distribution, and reproduction in any medium, provided the original author(s) and source are credited.

#### References

- Song, B. S., & Gary, P. R. (1983). A precision curvature-compensated CMOS bandgap reference. *IEEE Journal of Solid-State Circuits*, 18, 634–643.

- Gunawan, M., Meijer, G. C. M., Fonderie, J., & Huijsing, J. H. (1993). A curvature-corrected low-voltage bandgap reference. *IEEE Journal of Solid-State Circuits*, 28, 667–670.

- Lee, I., Kim, G., & Kim, W. (1994). Exponential curvature-compensated BiCMOS bandgap references. *IEEE Journal of Solid-State Circuits*, 29, 1396–1403.

- Leung, C. Y., Leung, K. N., & Mok, P. K. T. (2004). Design of a 1.5-V high-order curvature-compensated CMOS bandgap reference. In *Proceedings of 2004 IEEE International Symposium on Circuits and Systems*, Vancouver, Canada, 23–26 May, 2004.

- Banba, H., Shiga, H., Umezawa, A., Miyaba, T., Tanzawa, T., Atsumi, S., et al. (1999). A CMOS bandgap reference circuit with sub-1-V operation. *IEEE Journal of Solid-State Circuits*, 34, 670– 674.

- Malcovati, P., Maloberti, F., Fiocchi, C., & Pruzzi, M. (2001). Curvature-compensated BiCMOS bandgap with 1-V supply voltage. *IEEE Journal of Solid-State Circuits*, 36, 1076–1081.

- Tsividis, Y. P. (1980). Accurate analysis of temperature effects in I<sub>C</sub>-V<sub>BE</sub> characteristics with application to bandgap reference sources. *IEEE Journal of Solid-State Circuits*, 15, 1076–1084.

- 8. Rincon-Mora, G., & Allen, P. E. (1998). A 1.1-V current-mode and piecewise-linear curvature-corrected bandgap reference. *IEEE Journal of Solid-State Circuits*, *33*, 1551–1554.

- Leung, K. N., Mok, P. K. T., & Leung, C. Y. (2003). A 2-V 23μA 5.3-ppm/°C curvature-compensated CMOS bandgap reference. *IEEE Journal of Solid-State Circuits*, 38, 561–564.

- Hsiao, S.-W., Huang, Y.-C., Liang, D., Chen, H.-W. K., & Chen, H.-S. (2006). A 1.5-V 10-ppm/°C 2nd-order curvature-compensated CMOS bandgap reference with trimming. In *Proceedings of 2006 IEEE International Symposium on Circuits and Systems*, Island of Kos, Greece, 21–24 May, 2006.

Xiaokang Guan received his BSEE and MSEE degree in Electrical Engineering from Tianjin University, PR China, in 1997 and 2000, respectively. He received PhD degree from Department of Electrical and Computer Engineering, Illinois Institute of Technology, in 2007. He is currently a Mixed-Signal IC Design Engineer at Freescale Semiconductor, Inc., Irvine, CA, USA, His research interests are mixed-signal, RF IC design, ESD protection

design and multimedia signal processing.

Xin Wang received his BS degree from Beijing University of Posts & Telecommunications, Beijing, China, in 2005 and MS degree from Department of Electrical and Computer Engineering, Illinois Institute of Technology, Chicago, USA in 2007. He is currently a PhD candidate at the Department of Electrical Engineering. University of California, Riverside, CA, USA. His research interests are on UWB RF transceiver and mixed-signal

IC design and on-chip ESD protection design.

Albert Wang received the BSEE degree from the Tsinghua University, China, and the PhD EE degree from The State University of New York at Buffalo in 1985 and 1996, respectively. From 1995 to 1998, he was a Staff Engineer at National Semiconductor Corporation. From 1998 to 2007, He was Assistant and Associate Professor at the Department of Electrical and Computer Engineering, the Illinois Institute of Technology, USA, where he directed the

Integrated Electronics Laboratory. He is currently a Professor of Electrical and Computer Engineering and Director for the Laboratory for Integrated Circuits and Systems at the University of California, Riverside, USA. His research interests focus on Analog/Mixed-Signal/ RF ICs, Advanced on-Chip ESD Protection, IC CAD and Modelling, SoC, and Nano Devices, etc. Wang received the CAREER Award from the National Science Foundation in 2002. He is the author for the book "On-Chip ESD Protection for Integrated Circuits" (Kluwer 2002) and 130+ peer-reviewed papers in the field, and holds six US patents. Wang is Editor for the IEEE Electron Device Letters and Guest Editor for IEEE Transactions on Microwave Theory and Techniques. He was Associate Editor for the IEEE Transactions on Circuits and Systems I, Associate Editor for the IEEE Transactions on Circuits and Systems II, Guest Editor for the IEEE Journal of Solid-State Circuits and Guest Editor-in-Chief for the IEEE Transactions on Electron Devices. He is IEEE Distinguished Lecturer for the Electron Devices Society and served as IEEE Distinguished Lecturer for the Solid-State Circuits Society. He currently serves as Vice President for IEEE Electron Devices Society. He is committee member for the SIA International Technology Roadmap for Semiconductor (ITRS), the IEEE EDS VLSI Technology and Circuits Committee and the IEEE CAS Analog Signal Processing Technical Committee. He has been serving as Program co-Chair, Organization co-Chair, Steering Committee Member, TPC Member, Subcommittee Chair and Session Chair for numerous IEEE conferences. He speaks frequently at various industrial/academic/ international forums and is a frequent consultant to the IC industry. He is elected as Fellow of IEEE for contributions to design-for-reliability and system-on-chip.

Bin Zhao received the B.S.E.E. degree from Tsinghua University, Beijing, China, in 1985, and the M.S. and the Ph.D. degrees from the California Institute of Technology, Pasadena, CA, in 1988 and 1993, respectively. He has been with SEMATECH, Austin, TX, Rockwell International Corporation, Newport Beach, CA, Conexant Systems, Newport Beach, CA, Skyworks Solutions, Irvine, CA, and Freescale Semiconductor, Irvine, CA. His

past work and experience have been involved with both VLSI technology development and analog/mixed-signal/RF IC design. In 1997,

he fabricated the industry first Cu/low-k (k < 3) dual-damascene interconnect by developing a successful fabrication process for the Cu/SiOCH low-k dual-damascene interconnect which has been widely used in today's high performance ICs. In his tenure with Conexant and Skyworks, he led and managed the design of analog/ mixed-signal/power-management ICs and RF transceiver ICs for cellular mobile handsets. Currently he is the Director of Southern California Development Center, Freescale Semiconductor, Irvine, CA, where he leads the IC design and product development for consumer electronics and wireless communications. He has authored and co-authored more than 200 journal publications and conference presentations, has written three book chapters, and holds 45 issued US patents. Dr Zhao has served on various IEEE conference committees including International Electron Device Meeting (IEDM), IEEE Symposium on VLSI Technology, IEEE Symposium on VLSI Circuits, International Conference on Solid-State and IC Technology (ICSICT), and International Conference on ASIC (ASICON). He has served as Chairman, Symposium on Advances in Interconnect and Packaging Materials, TMS 2000; Chair, Subcommittee of Integrated Circuits and Manufacturing, IEDM 2001; Co-Chair, ICSICT Organizing Committee, 2001-2008; Co-Chair, ASICON Technical Program Committee, 2007-2009; Guest Editor, IEEE/TMS Journal of Electronic Materials; Guest Editor, IEEE Transactions on Electron Devices; Associate Editor, IEEE Transactions on Circuits and Systems-I and II, respectively; Co-Chair, Technical Working Group of RF and Analog/Mixed-Signal IC Technologies for Wireless Communications, the International Technology Roadmap for Semiconductors, 2003-2007; Chair, IEEE Johnson Technology Award Committee, 2007-2008; and Chair, IEEE/EDS VLSI Technology and Circuits Committee. He is an IEEE Fellow and an IEEE Distinguished Lecturer. He is a recipient of the ECE Reader Award (2008), the Hearst Semiconductor Applications Award (2008), and the EDN Innovation Award (2009).