Abstract

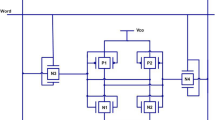

The data stability issues in SRAM cells become more prominent with the decreasing of feature sizes in CMOS technology. The focus of memory manufacturers always remains on reducing power consumption and stability improvements of the SRAM cells. In this work, the critical parameters of FinFET and CMOS transistors based on SRAM cells are compared. This paper focuses on the simulation of 10T SRAM cell topologies design using sleep transistor, drowsy cache, and self-controllable voltage technique (SVL) techniques and their comparison. Among all these techniques, SVL shows the best results by consuming 4768 nw power for FinFET technology and 15.8383 n W power for CMOS technology. Evaluated results show 40%, 26%, and 10% improvement in HSNM, RSNM, and WSNM, respectively, and 80.93% reduction in leakage power. FinFET design SRAM cells result in higher RSNM, HSNM, and WSNM. For simulation, the HSPICE tool is used at 32 nm PTM CMOS and FinFET transistor with a supply voltage of 900 mV and 25 °C temperature.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Vittoz E, Fellrath J (1977) CMOS analog integrated circuits based on weak inversion operation. IEEE J Solid-State Circ 12(3):224–231

Chandrakasan AP, Sheng S, Brodersen RW (1992) Low-power CMOS digital design. IEEE J Solid-State Circ 27(4):473–484

Mutoh S, Douseki T, Matsuya Y, Aoki T, Shigematsu S, Yamada J(1995) 1-V power supply high-speed digital circuit technology with multi-threshold-voltage CMOS. IEEE J Solid-State Circ 847–854

Verma N, Chandrakasan AP (2007) A 65 nm 8T Sub-Vt SRAM employing sense-amplifier redundancy. In: Proceedings of IEEE ISSCC digest of technical papers, pp 328–606

Kim TH, Liu J, Keane J, Kim CH (2007) A high-density subthreshold SRAM with data-independent bitline leakage and virtual-ground replica scheme. In: Proceedings of IEEE ISSCC digest of technical papers, pp 330–606

Bhavnagarwala AJ, Kosonocky S, Radens C, Chan Y, Stawiasz K, Srinivasan U, Kowalczyk SP, Ziegler MM (2008) A sub-600 mV, fluctuation tolerant 65-nm CMOS SRAM array with dynamic cell biasing. IEEE J Solid-State Circ 43(4):946–955

Carlson AE (2008) Device and circuit techniques for reducing variation in nanoscale SRAM. Ph.D. dissertation, University California Berkeley, Berkeley, CA

Vaddi R, Dasgupta S, Agarwal RP (2010) Device and circuit co-design robustness studies in the subthreshold logic for ultralow-power applications for 32 nm CMOS. IEEE Trans. Electron Devices 57(3):654–664

Islam A, Hasan M (2012) Leakage characterization of 10T SRAM cell. IEEE Trans Electron Devices 59(3):631–638

Priya MG, Baskaran K, Krishnaveni D (2012) Leakage power reduction techniques in deep submicron technologies for VLSI applications 1163–1170

Sathishkumar A, Saravanan S (2014) Analysis and design of low power high speed dynamic latch comparator using CMOS. Int J Sci Eng Res 5(5):173–177

Pal S, Bhattacharya A, Islam A (2014) Comparative study of CMOS- and FinFET-based10T SRAM cell in subthreshold regime. In: IEEE international conference on advanced communication control and computing technologies (ICACCCT)

Gupta V, Khandelwal S, Raj B, Gupta RD (2015) Leakage current reduction in FinFET based 6T SRAM cell for minimizing power dissipation in nanoscale memories. In: 2015 IEEE Nirma University international conference on engineering

Sneha G, Krishna BH, Kumar CA (2017) Design of 7T FinFET based SRAM cell design for nanometer regime. In: International conference on inventive systems and control

Hosseini-Salekdeh SR (2016) A comparative analysis of 6T and 10T SRAM cells for sub-threshold operation in 65nm CMOS technology. M.Sc thesis, Waterloo, Ontario, Canada

Venugopal K, Babu PS (2015) Low power SRAM cell of leakage current and leakage power reduction. Int J Sci Eng Technol Res (IJSETR) 4(8)

VR Member, Saravanakumar M (2016) Design and analysis of SRAM cells for power reduction using low power techniques. In: IEEE region 10 conference (TENCON), proceedings of the international conference

Ruhil S, Shukla NK (2017) Leakage current optimization in 9T SRAM bit-cell with sleep transistor at 45nm CMOS technology. In: International conference on computing and communication technologies for smart nation (IC3TSN)

Mishra JK, Srivastava H (2018) A 40nm low power high stable SRAM cell using separate read port and sleep transistor methodology. In: IEEE international symposium on smart electronic systems

Madhumalini M, Iyshvarya R (2019) Design of low power SRAM cell using 10transistors. J VLSI Design Sign Process 37–44

Maute JM, Puebla VK, Nericua RT, Gerasta OJ, Hora JA (2018) Design implementation of 10T static random access memory cell using stacked transistors for power dissipation reduction. IEEE

Badran MS, Issa HH, Eisa SM, Ragai HF (2018) Low power 7 nm FinFET based 6T-SRAM design. J Adv Res Appl Mech

Jaiswal K, Saxena S (2017) A review on FinFET based SRAM design for low power applications. Int J Technol Res Manage

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Sharma, D., Birla, S. (2021). Comparative Study of CMOS and FinFET-Based SRAM Cell Using SVL Technique. In: Sharma, D.K., Son, L.H., Sharma, R., Cengiz, K. (eds) Micro-Electronics and Telecommunication Engineering. Lecture Notes in Networks and Systems, vol 179. Springer, Singapore. https://doi.org/10.1007/978-981-33-4687-1_2

Download citation

DOI: https://doi.org/10.1007/978-981-33-4687-1_2

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-33-4686-4

Online ISBN: 978-981-33-4687-1

eBook Packages: EngineeringEngineering (R0)