Abstract

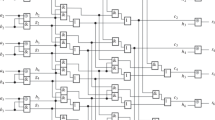

For performing efficient modular arithmetic operations, several cryptographic and pseudorandom bit generator (PRBG) algorithms utilize a 3-operand binary adder as the primary functional unit. The Carry Save Adder is the most common adder used for performing the three-operand extension (CS3A). On the other hand, the ripple-carry step of CS3A results in a significant delay while transmitting the output signals. Due to the lengthy delay, it influences the performance of MDCLG architecture. For performing three-operand addition, two-operand adders, such as Kooge Stone (KSA), can be used. This will decrease the critical route latency, delay, and area compared to other parallel prefix adders. The proposed high-speed and space-efficient adder architecture for performing three-operand binary operations includes carry-prefix computation logic after performing the pre-compute bitwise addition. The proposed adder design reduces the adder latency while consuming less area and power. A Kogge–Stone parallel prefix adder has been used to develop a novel architecture for the proposed 8-bit, 16-bit, and 32-bit three-operand adders. The proposed architecture is implemented by using Verilog coding, and further, the power and delay extraction has been performed by using a Xilinx tool. The proposed architecture has been developed by using the MDCLCG method with the three-operand adder, and further, the proposed architecture is proven with respect to delay as well as area and power.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Panda AK, Palisetty R, Ray KC (2020) High-speed area-efficient VLSI architecture of three-operand binary adder. IEEE Trans Circ Syst I Regul Pap 67(11):3944–3953. https://doi.org/10.1109/TCSI.2020.3016275

Mahalakshmi R, Sasilatha T (2013) A power efficient carry save adder and modified carry save adder using CMOS technology. In: 2013 IEEE international conference on computational intelligence and computing research, pp 1–5. https://doi.org/10.1109/ICCIC.2013.6724189

Daphni S, Vijula Grace KS (2021) Design an area efficient Kogge stone adder using pass transistor logic. In: 2021 Third international conference on intelligent communication technologies and virtual mobile networks (ICICV), pp 614–618. https://doi.org/10.1109/ICICV50876.2021.9388489

Padmanabhan TR, Bala Tripura Sundari B (2004) Introduction to Verilog. In: Design through Verilog HDL. IEEE, pp 11–29. https://doi.org/10.1002/0471723002.ch2

Panda AK, Ray KC (2020) A coupled variable input LCG method and its VLSI architecture for pseudorandom bit generation. In: IEEE transactions on instrumentation and measurement, vol 69, no 4, pp 1011–1019. https://doi.org/10.1109/TIM.2019.2909248

Simson A, Deepak S (2021) Design and implementation of high speed hybrid carry select adder. In: 2021 International conference on advances in electrical, computing, communication and sustainable technologies (ICAECT), pp 1–6. https://doi.org/10.1109/ICAECT49130.2021.9392452

Koyada B, Meghana N, Jaleel MO, Jeripotula PR (2017) A comparative study on adders. In: 2017 international conference on wireless communications, signal processing and networking (WiSPNET), pp 2226–2230. https://doi.org/10.1109/WiSPNET.2017.8300155

Han T, Carlson DA (1987) Fast area-efficient VLSI adders. In: 1987 IEEE 8th symposium on computer arithmetic (ARITH), pp 49–56. https://doi.org/10.1109/ARITH.1987.6158699

Tapasvi B, Sinduri KB, Lakshmi BGSSB, Kumar NU (2015) Implementation of 64-bit Kogge Stone carry select adder with ZFC for efficient area. In: 2015 IEEE international conference on electrical, computer and communication technologies (ICECCT), pp 1–6. https://doi.org/10.1109/ICECCT.2015.7226154

Abhiram T, Ashwin T, Sivaprasad B, Aakash S, Anita JP (2017) Modified carry select adder for power and area reduction. In: 2017 International conference on circuit, power and computing technologies (ICCPCT), pp 1–8. https://doi.org/10.1109/ICCPCT.2017.8074371

Anahita G, Krishnapriya KPM, Shiva R, Mohan N (2018) HD-sign: hardware based digital signature generation using true random number generator. Int J Eng Technol 7:147. https://doi.org/10.14419/ijet.v7i3.8.16850

Ramapragada KST, Netla AKR, Chattada PK, Manickam B (2021) Design and FPGA implementation of high-speed area and power efficient 64-bit modified dual CLCG based pseudo random bit generator. In: 2021 IEEE international symposium on smart electronic systems (iSES), pp 93–98. https://doi.org/10.1109/iSES52644.2021.00032

Mohan K, Devi A, Nirmala Sethumadhavan M, Santhya R (2018) A selective generation of hybrid random numbers via Android smart phones. Int J Pure Appl Math 118:311–316

Katti RS, Srinivasan SK (2009) Efficient hardware implementation of a new pseudo-random bit sequence generator. In: 2009 IEEE international symposium on circuits and systems, pp 1393–1396. https://doi.org/10.1109/ISCAS.2009.5118025

Karuppusamy P (2019) Design and analysis of low-power. High-speed Baugh Wooley multiplier. J Electron 1(02):60–70

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Rajesh, M., Bala Tripura Sundari, B. (2023). FPGA Implementation of Efficient 32-Bit 3-Operand Addition Using Kogge–Stone (KS) Parallel Prefix Adder. In: Bindhu, V., Tavares, J.M.R.S., Vuppalapati, C. (eds) Proceedings of Fourth International Conference on Communication, Computing and Electronics Systems . Lecture Notes in Electrical Engineering, vol 977. Springer, Singapore. https://doi.org/10.1007/978-981-19-7753-4_22

Download citation

DOI: https://doi.org/10.1007/978-981-19-7753-4_22

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-19-7752-7

Online ISBN: 978-981-19-7753-4

eBook Packages: EngineeringEngineering (R0)