Abstract

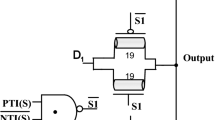

The future of the electronic industry is the nanotechnology which witnessed a tremendous change in the world of electronics. To increase the performance of the silicon-based industry, there are promising alternatives which shown a greater superiority like carbon nanotube field-effect transistors (CNTFET). Multi-valued circuits (MVL) act as novel gadgets for optimizing the power. When the Ternary circuits are built with CNTFET’s, we can achieve the advantages of reduction in power dissipation and increase in the speed. This paper talks much about the implementation of various logic gates, combinational circuits and sequential circuits using CNTFETs and multi-valued circuits. The proposed designs aim at decreasing the power delay product (PDP). The intended designs include ternary inverter, ternary NAND, ternary decoder, ternary half adder, ternary multiplier, ternary multiplexer and ternary full adder. We optimize the power at the basic gate level which would in turn help to reduce the power at any complex circuit we use.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Oseily H, Haidar AM (2015) Hexadecimal to binary conversion using multi-input floating gate complementary metal oxide semiconductors. In: International conference on applied research in computer science and engineering (ICAR), Beirut, Lebanon, pp 1–6 (2015)

Patil M, Mahesh RK (2015) Power efficient parallel adder design using CNTFET. Int J Ethics Eng Manag Educ (IJEEE) 2(4)

Supriya SJ, Narkhede S (2015) Design of ternary D latch using carbon nanotube field effect transistors. In: Proceedings of 2nd international conference on electronics and communication systems (ICECS), pp 1–9, June 2015

Sharifi F, Moaiyeri MH, Navi K, Bagherzadeh N (2015) Quaternary full adder cells based on carbon nanotube FETs. J Comput Electron 14(3), 762–772

Muglikar M, Sahoo R, Sahoo SK (2016) High performance ternary adder using CNTFET. In: 3rd international conference on devices, circuits and systems (ICDCS), Coimbatore, India

Jyoti K, Narkhede S (2016) An approach to ternary logic gates using FinFET. In: Proceedings of the international conference on advances in information communication technology & computing (AICTC 2016), Bikaner, India

Jane V, Tembhurne S (2016) Design Low Power Quaternary Adder Using Multi-Value Logic. Int J Adv Eng Technol Manag Appl Sci (IJAETMAS) 03(07):181–187

Samadi H, Shahhoseini A, Aghaei-liavali F (2017) A new method on designing and simulating CNTFET-based ternary gates and arithmetic circuits. Microelectron J 63:41–48. https://doi.org/10.1016/j.mejo.2017.02.018

Moaiyeri MH, Rahi A, Sharifi F, Navi K (2017) Design and evaluation of energy-efficient carbon nanotube FET based quaternary minimum and maximum circuits. J Appl Res Technol 15(3):233–241

Irfan M, Ullah Z (2017) G-AETCAM: gate-based area-efficient ternary content-addressable memory on FPGA. IEEE Access 5:20785–20790. https://doi.org/10.1109/ACCESS.2017.2756702

Miller D, Soeken M (2018) A spectral algorithm for ternary function classification. In: IEEE 48th international symposium on multiple-valued logic (ISMVL), Linz, Austria

Saleh N, Kassem A, Haidar AM (2018) Energy-efficient architecture for wireless sensor networks in healthcare applications. IEEE Access 6:6478–6486. https://doi.org/10.1109/ACCESS.2018.2789918

Hills G, Bardon MG, Doornbos G, Yakimets D, Schuddinck P, Baert R, Jang D, Mattii L, Sherazi SY, Rodopoulos D, Ritzenthaler R, Lee C-S, Thean A, Radu I, Spessot A, Debacker P, Catthoor F, Raghavan P, Shulaker M, Philip Wong H-S, Mitra S (2018) Understanding energy efficiency benefits of carbon nanotube field-effect transistors for digital VLSI. IEEE Trans Nanotechnol 17(6):1259–1269. https://doi.org/10.1109/TNANO.2018.2871841.

Khezeli MR, Moaiyeri MH, Jalali A (2019) Comparative analysis of simultaneous switching noise effects in MWCNT bundle and Cu power interconnects in CNTFET-based ternary circuits. IEEE Transact Very Large Scale Integr (VLSI) Syst 27(1):37–46. https://doi.org/10.1109/TVLSI.2018.286976.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Vejendla, N., Jamanchipalli, P., Bontha, S., Dendeti, J., Bolloju, B., Kuppili, K.K. (2021). Design of Low PDP Ternary Circuits Utilizing Carbon Nanotube Field-Effect Transistors. In: Sekhar, G.C., Behera, H.S., Nayak, J., Naik, B., Pelusi, D. (eds) Intelligent Computing in Control and Communication. Lecture Notes in Electrical Engineering, vol 702. Springer, Singapore. https://doi.org/10.1007/978-981-15-8439-8_21

Download citation

DOI: https://doi.org/10.1007/978-981-15-8439-8_21

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-8438-1

Online ISBN: 978-981-15-8439-8

eBook Packages: Computer ScienceComputer Science (R0)