Abstract

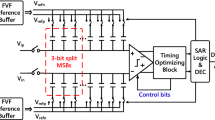

The design of a 6-bit, 100 MHz successive approximation register (SAR) analog to digital converter (ADC) is presented in this paper. The implemented SAR ADC is realized by using SAR logic, a 6-bit DAC, a sample and hold circuit and a comparator circuit. The fully realized system is measured under different input frequencies with a sampling rate of 100 MHz and it consumes 36.7 µW from a 1.8 V power supply. The ADC implemented in 130 nm CMOS technology exhibits signal-to-noise plus distortion ration SNDR of 64.2 dB and occupies a die area of 0.14 mm2.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Lai, W.C., Huang, J.F., Hsieh, C.G., Kao, F.T.: An 8-bit 2 MS/s successive approximation register analog-to-digital converter for bioinformatics and computational biology application. In: 2015 IEEE 12th International Conference on Networking, Sensing and Control, Taipei, pp. 576–579 (2015)

Yan, F., Libing, Z., Liyuan, L., Dongmei, L.: A 2GSPS 6-bit two-channel-interleaved successive approximation ADC design in 65 nm CMOS. In: 2013 International Conference on Computational and Information Sciences, Shiyang, pp. 1640–1643 (2013)

Zhu, Y., et al.: A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circ. 45(6), 1111–1121 (2010)

Kull, L., et al.: A 3.1 mW 8b 1.2 GS/s single-channel asynchronous SAR ADC with alternate comparators for enhanced speed in 32 nm digital SOI CMOS. IEEE J. Solid-State Circ. 48(12), 3049–3058 (2013)

Kuo, H.L., Lu, C.W., Lin, S.G., Chang, D.C.: A 10-bit 10 MS/s SAR ADC with the reduced capacitance DAC. In: 2016 5th International Symposium on Next-Generation Electronics (ISNE), Hsinchu, pp. 1–2 (2016)

Yang, J., Naing, T.L., Brodersen, R.W.: A 1 GS/s 6 bit 6.7 mW successive approximation ADC using asynchronous processing. IEEE J. Solid-State Circ. 45(8), 1469–1478 (2010)

Lee, S.Y., Cheng, C.J., Wang, C.P., Lee, S.C.: A 1-V 8-bit 0.95 mW successive approximation ADC for biosignal acquisition systems. In: 2009 IEEE International Symposium on Circuits and Systems, Taipei, pp. 649–652 (2009)

Krishna, K.L., Ramashri, T.: VLSI design of 12-Bit ADC with 1 GSPS in 180 nm CMOS integrating with SAR and two-step flash ADC. J. Theor. Appl. Inf. Technol. 68(1), 27–35 (2014)

Baker, R.J.: CMOS Circuit Design, Layout and Simulation, 3rd edn. Wiley-IEEE Press, Hoboken (2010)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Krishna, K.L., Anuradha, K., Murshed, A.M. (2019). A 6-Bit Low Power SAR ADC. In: Verma, S., Tomar, R., Chaurasia, B., Singh, V., Abawajy, J. (eds) Communication, Networks and Computing. CNC 2018. Communications in Computer and Information Science, vol 839. Springer, Singapore. https://doi.org/10.1007/978-981-13-2372-0_57

Download citation

DOI: https://doi.org/10.1007/978-981-13-2372-0_57

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-13-2371-3

Online ISBN: 978-981-13-2372-0

eBook Packages: Computer ScienceComputer Science (R0)