Abstract

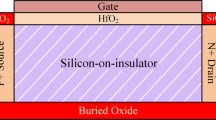

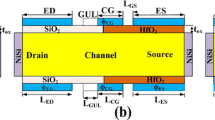

In this work, a novel approach has been investigated to overcome one of the major issue faced by Tunnel FETs i.e. its low drive current or On-current. The approach employed in the present work makes use of a non-rectangular tapered gate electrode geometry which helps in concentrating the electric field lines emanating from gate electrode towards the source/channel tunneling junction which results in enhancement in the band-to-band tunneling current.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Seabaugh, A.C., Zhang, Q.: Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98, 2095–2110 (2010)

Lu, H., Seabaugh, A.: Tunnel field-effect transistors: state-of-the-art. IEEE J. Electron Dev. Soc. 2(4), 44–49 (2014)

Avci, U.E., Morris, D.H., Young, I.A.: Tunnel field-effect transistors: prospects and challenges. IEEE J. Electron Dev. Soc. 3(3), 88–95 (2015)

Virani, H.G., Adari, R.B.R., Kottantharayil, A.: Dual-spacer device architecture for the improvement of performance of silicon n-channel tunnel FETs. IEEE Trans. Electron Dev. 57, 2410–2417 (2010)

Lee, G., Jang, J.-S., Choi, W.Y.: Dual-dielectric-constant spacer hetero-gate-dielectric tunneling field-effect transistors. Semicond. Sci. Technol. 28, 052001 (2013)

Schlosser, M., Bhuwalka, K.K., Sauter, M., Zilbauer, T., Sulima, T., Eisele, I.: Fringing-induced drain current improvement in the tunnel field-effect transistor with high-k gate dielectrics. IEEE Trans. Electron Dev. 56, 100–108 (2009)

Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373), 329–337 (2011)

Biswas, A.: Tunnel field effect transistors: from steep-slope electronic switches to energy efficient logic applications. Ph.D. dissertation, École Polytechnique Fédérale De Lausanne (2015)

Biswas, A., Alper, C., Michielis, L.D., Ionescu, A.M.: New tunnel-FET architecture with enhanced I ON and improved Miller Effect for energy efficient switching. In: Proceedings of 70th Annual Device Research Conference (DRC), Pennsylvania, USA, pp. 131–132 (2012)

Datta, S., Liu, H., Narayanan, V.: Tunnel FET technology: a reliability perspective. Microelectron. Reliab. 54, 861–874 (2014)

Chang, C.P., Pai, C.S., Vuong, T.H.H.: MOSFET with tapered gate and method of manufacturing it. European Patent, EP1091414 A2 (2001)

Oh, H.S., Cha, S.J.: Field effect transistors having tapered gate electrodes for providing high breakdown voltage capability and methods of forming same. US Patent, US6046474 A (2000)

Kuroi, T., Itoh, Y., Horita, K., Shiozawa, K.: Semiconductor device including inversely tapered gate electrode and manufacturing method thereof. US Patent, US6661066 B2 (2003)

Ichikawa, H., Makabe, I., Kouchi, T., Nakata, K., Inoue, K.: InAlN/GaN HEMTs with over 100-GHz fT using an improved Y-gate process by an i-line stepper. In: Proceedings of International Conference on Compound Semiconductor Manufacturing Technology, Arizona, USA, pp. 225–228 (2015)

Ichikawa, H., Mizue, C., Makabe, I., Tateno, Y., Nakata, K., Inoue, K.: AlGaN/GaN HEMTs versus InAlN/GaN HEMTs fabricated by 150-nm Y-gate process. In: Proceedings of Asia Pacific Microwave Conference (APMC), Japan, pp. 780–782 (2014)

Nagavarapu, V., Jhaveri, R., Woo, J.C.S.: The tunnel source (PNPN) n-MOSFET: a novel high performance transistor. IEEE Trans. Electron Devices 55(4), 103–1019 (2008)

Han, G., Yee, Y.S., Guo, P., Yang, Y., Fan, L., Zhan, C., Yeo, Y.-C.: Enhancement of TFET performance using dopant profile-steepening implant and source dopant concentration engineering at tunneling junction. In: Proceedings of Silicon Nanoelectronics Workshop, pp. 1–2 (2010)

Atlas User’s Manual, “Device simulation software,” SILVACO International Inc., 5.16.3.R

Acknowledgment

Authors would like to thank Council of Scientific & Industrial Research (CSIR), India (File No. 22(0724)/17/EMR-II)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Narang, R., Gupta, M., Saxena, M. (2017). Improved Gate Modulation in Tunnel Field Effect Transistors with Non-rectangular Tapered Y-Gate Geometry. In: Kaushik, B., Dasgupta, S., Singh, V. (eds) VLSI Design and Test. VDAT 2017. Communications in Computer and Information Science, vol 711. Springer, Singapore. https://doi.org/10.1007/978-981-10-7470-7_46

Download citation

DOI: https://doi.org/10.1007/978-981-10-7470-7_46

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-7469-1

Online ISBN: 978-981-10-7470-7

eBook Packages: Computer ScienceComputer Science (R0)