Abstract

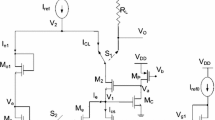

High resolution DACs require large transistors to obtain the desired accuracy according to the Pelgrom model [1], which increases the area drastically. To overcome this area accuracy trade off, several calibration techniques were investigated. This paper presents a modified self calibration technique for current-steering (CS) digital-to-analog converters (DACs). In the digital calibration technique calibrating DACs (CALDACs) are connected across each bit, which requires calibration. High resolution CALDAC increases the accuracy at a cost of increment in the area. To overcome this problem, this technique is slightly modified. Instead of using CALDAC of 6 or 8 bits across each bit, here a single CALDAC is used to calibrate each bit, and its equivalent calibrated value in terms of analog voltage is stored across the capacitor (instead of within SRAM memory in digital form), which is connected in the place of CALDAC by using an extra-auxiliary transistor. MOSFET as a switch is used for simultaneous switching and to hold the correct voltage after turning off switches, injection nulling switch type track and hold circuit is used. To demonstrate this technique, a 10-bit binary-weighted CS DAC is implemented in a 0.18 \(\upmu \)m CMOS process. With worst-case process parameter variations, simulated integral and differential nonlinearities of the calibrated DAC are less than 0.32 LSB.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Kinget, P.R.: Device mismatch and tradeoffs in the design of analog circuits. IEEE J. Solid-State Circ. 40(6), 1212–1224 (2005)

Bechthum, E., Radulov, G., van Roermund, A.: A novel temperature and disturbance insensitive DAC calibration method. In: IEEE International Symposium on Circuits and Systems (ISCAS) (2011)

Cong, Y., Randall, L.G.: TA 1.5 V 14 b 100 MS/s self-calibrated DAC International Solid-State Circuits Conference, (ISSCC) (2003)

Tiilikainen, M.P.: 14-bit 1.8V 20-mW 1 mm\(^2\) CMOS DAC. IEEE J. Solid-State Circ. 36(7), 1144–1147 (2001)

Dongmei, Z., Dongbing, F., Jiangang, S., Kaicheng, L.: Digital static calibration technology used for 16-bit DAC. In: 8th International Conference on ASIC, pp. 1081–1084 (2009)

Tsai, J.H., Chen, Y., Lai, Y., Shen, M., Huang, P.: A 14-bit 200MS/s current-steering DAC achieving over 82 dB SFDR with digitally-assisted calibration and dynamic matching techniques. In: International Symposium on VLSI DAT (2012)

Chi, J., Chu, S., Tsai, T.: A 1.8 V 12-bit 250-MS/s 25-mW self-calibrated DAC. In: Proceedings of the ESSCIRC, pp. 222–225 (2010)

Maunu, J., Pankaala, M., Marku, J., Poikonen, J., Laiho, M., Paasio, A.: Current source calibration by combination selection of minimum sized devices. In: International Symposium on Circuits and Systems, ISCAS (2006)

Virtanen, K., Maunu, J., Poikonen, J., Paasio, A.: A 12-bit current-steering DAC with calibration by combination selection. In: International Symposium on Circuits and Systems, ISCAS, pp. 1469–1472 (2007)

Ikeda, Y., Frey, M., Matsuzawa, A.: A 14-bit 100 MS/s digitally calibrated binary-weighted current-steering CMOS DAC without calibration ADC. In: IEEE Asian Solid-State Circuits Conference, pp. 356–359 (2007)

Traff, H.: Novel approach to high speed CMOS current comparators. Electron. Lett. 28(3), 310–311 (1992)

Wayne, K.: Current-mode CMOS multiple-valued logic circuits. IEEE J. Solid-State Circ. 29(2), 95–107 (1994)

Freitas, D., Wayne, K.: CMOS current comparator circuit. Electron. Lett. 19(17), 695–697 (1983)

Anderson, T.: Optimum control logic for successive approximation analog-to-digital converters. Deep Space Netw. Progr. Rep. 13, 168–176 (1972)

Behzad, R.: Design of Analog CMOS Integrated Circuits. Tata McGraw Hill, New Delhi (reprint), original (New York) (2002)

Dai, L., Harjani, R.: CMOS switched-Op-amp-based sample-and-hold circuit. IEEE J. Solid-State Circ. 35(1), 109–113 (2000)

John, D., Martin, K.: Analog integrated circuit design. Wiley, New York (2008)

Baptista, A.J.G.: Novel techniques for the design and practical realization of switched-capacitor circuits in deep-submicron CMOS technologies. Thesis report (2009)

Lee, W., Chan, P.: An injection-nulling switch for switched-capacitor circuit applications. IEEE Trans. Instrum. Meas. 54(6), 2416–2426 (2005)

Engelhardt, M.: LTSpice/SwitcherCAD IV. Linear Technology Corporation (2011)

Christine, T.: MOSIS-A gateway to silicon. IEEE Circ. Devices Mag. 4(2), 22–23 (1988)

Wong, L., Hossain, S., Andrew, T., Jorgen, E., Dominic, H., Hans, N.: A very low-power CMOS mixed-signal IC for implantable pacemaker applications. IEEE J. Solid-State Circ. 39(12), 2446–2456 (2004)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Darji, P., Parikh, C. (2017). A Calibration Technique for Current Steering DACs - Self Calibration with Capacitor Storage. In: Kaushik, B., Dasgupta, S., Singh, V. (eds) VLSI Design and Test. VDAT 2017. Communications in Computer and Information Science, vol 711. Springer, Singapore. https://doi.org/10.1007/978-981-10-7470-7_12

Download citation

DOI: https://doi.org/10.1007/978-981-10-7470-7_12

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-7469-1

Online ISBN: 978-981-10-7470-7

eBook Packages: Computer ScienceComputer Science (R0)