Abstract

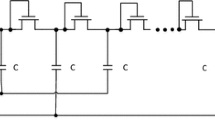

Conventional charge pump circuit based on dynamic charge transfer switch (CTS) is limited by its efficiency due to the threshold voltage of MOS transistor. This paper proposes an improved dynamic CTS based charge pump circuit by modifying the conventional circuit architecture at the output stage by a PMOS transistor with appropriate control signals. A four-stage dynamic CTS based charge pump circuit with pumping capacitance of 50 pF, clock frequency of 20 MHz and load current of 100 µA is designed and simulated in Cadence environment using UMC 0.18 µm CMOS technology. As compared to conventional architecture, this modification has reduced the voltage loss at the output to 1.3% as compared to 9% for 1 V input and 6% as compared to 20% for 0.3 V input voltage. The core dimension of the layout is 750 µm × 530 µm.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Aaltonen, L., Halonen, K.: Pseudo-continuous-time readout circuit for a 300 0/s capacitive 2-axis micro-gyroscope. IEEE J. Solid-State Circ. 44(12), 3609–3620 (2009)

Yinl, H., Pengl, X., Wangl, J., Weil, Z., Gonf, N.: Analysis and design of CMOS charge pump for EEPROM. In: 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Guilin, China, pp. 28–31 (2014)

Rahman, L.F., Reaz, M.B.I., Ali, M.A.M.: A Low-voltage charge pump circuit for RFID tag EEPROM. In: Fourth International Conference on Emerging Trends in Engineering & Technology, pp. 244–246 (2011)

Huang, H.Y., Yen, S.Z., Chen, J.H., Hong, H.C., Cheng, K.H.: Low-voltage indoor energy harvesting using photovoltaic cell. In: 2016 IEEE 19th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), Kosice, Slovakia, pp. 1–4 (2016)

Zhou, J., Huang, M., Zhang, Y., Zhang, H., and Yoshihara, T.: A novel charge sharing charge pump for energy harvesting application. In: IEEE International SoC Design Conference, Jeju, South Korea, pp. 373–376 (2011)

Dickson, J.: On-chip high-voltage generation in NMOS integrated circuits using an improved voltage multiplier technique. IEEE J. Solid-State Circ. 11(6), 374–378 (1976)

Wu, J.T., Chang, K.L.: MOS charge pump for low-voltage operation. IEEE J. Solid-State Circ. 33(4), 592–597 (1998)

Pylarinous, L.: Charge pumps: an overview. In: Proceedings of the IEEE International Symposium on Circuits and Systems, Bangkok Thailand, pp. 1–7 (2003)

Shabana, S., Thej, C., Sankar, H., Pandava, R., Dutta, A., Singh, S.G.: Design of highly efficient charge pump for energy harvesting RFID application. In: Asia Pacific Conference on Postgraduate Research in Microelectronic & Electronics, Hyderabad India, pp. 46–50 (2012)

Razavi, B.: Design of Analog CMOS Integrated Circuits, International Edn. Tata McGraw-Hill (2001)

Palumbo, G., Pappalardo, D.: Charge pump circuits: an overview on design strategies and topologies. IEEE Circ. Syst. Mag. 10, 31–45 (2010)

Mohammadi, B., Rodrigues, J.: Ultra low energy and area efficient charge pump with automatic clock controller in 65 nm CMOS. In: IEEE Asian Solid-State Circuits Conference, Xiamen, Fujjan, China, pp. 1–4 (2015)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Kumar, N., Gudlavalleti, R.H., Bose, S.C. (2017). An Improved Highly Efficient Low Input Voltage Charge Pump Circuit. In: Kaushik, B., Dasgupta, S., Singh, V. (eds) VLSI Design and Test. VDAT 2017. Communications in Computer and Information Science, vol 711. Springer, Singapore. https://doi.org/10.1007/978-981-10-7470-7_11

Download citation

DOI: https://doi.org/10.1007/978-981-10-7470-7_11

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-7469-1

Online ISBN: 978-981-10-7470-7

eBook Packages: Computer ScienceComputer Science (R0)