Abstract

Interconnects are integral part in the chip design which are responsible for the flow of signal from input to output. Due to the presence of parasitic such as resistance, capacitance components, and intermediate devices, the signal integrity problems may occur. Nowadays, because of technological advances, the effects of parasitic are increasing, which are causing adverse effect on the circuit performance in terms of delay and power. So interconnects have become a major problem. In this paper an endeavor has been made to simulate and examine the effect of interconnects due to variation of line parasitic on the circuit performance parameters in various DSM technologies. Here the values of R and C have been estimated for copper interconnects in different technologies with variable lengths and developed a simple RC interconnect simulation model with a driver and load concepts. For the simulated interconnect model with different interconnect structures and variable lengths, delay and PDP values are estimated. Within the same technology, the simulation results of performance metrics indicate 10% variations for variable lengths of interconnects, 5% variation with different interconnect structures, and more than 50% variation in different technologies.

Similar content being viewed by others

Keywords

1 Introduction

VLSI is a method of making integrated circuits by combining countless transistors in an exceedingly single chip. In today’s era as the technology gets more advances, the number of devices organized on chips increased, leading to more number of interconnects [1]. These interconnect now not behave as simple resistors but can also have related parasitic consisting of capacitance and inductance, which leads to signal degradations. With growing need of transportable systems, low propagation delay and power dissipation are the major challenges for researchers. As the interconnect length increases linearly, the parasitic interconnect capacitance (C) and interconnect resistance (R) also increase linearly which in turn increase the RC product thereby increasing the propagation delay [2]. This is due to the linear increase in both the interconnect resistance and capacitance with increase of interconnect length. In the same way in deep submicron technologies also the propagation delay increases with increase in the parasitic and interconnects length.

Frequency of operation in the global interconnects is characterized by capacitive, resistive, and inductive properties which have more effect on the circuit performance [2]. In this paper, an attempt is to study the effects of these parasitic on circuit design parameters such as power, delay, and energy by considering different interconnect structures such as single interconnect and coupled interconnects for copper wire with simple CMOS driver and load. Different technologies along with different lengths of interconnects have been considered and calculated the propagation delay, power, and energy. It has been reported that interconnects in any VLSI system account for more than 60% of signal delay [3, 4]. The paper has been prepared in the following way.

Section 2 explains the types of interconnects. Section 3 describes the interconnect models and parameters. Simulation results have been presented and discussed in Sect. 4. The conclusions have been presented in Sect. 5. This brief is organized as follows. Section 2 describes the VCO types. Section 3 describes the proposed ring VCO design. The simulation results are given in Sect. 4 and the conclusion is given in Sect. 5.

2 Interconnect Types

Interconnect or wiring is used in any system or circuit to propagate the clock and other signals which give data, power, or ground to all the circuits in a system. This interconnect is classified based on its length, namely (i) local, (ii) semi global, and (iii) global [5, 6]. Local interconnect offers less parasitic due to the smaller size, does not travel very long distances, and cover smaller distance only in a chip. Semi global interconnect gives parasitic because of wider and taller than local interconnects. This interconnect provides the interconnection between substantial modules and I/O circuitry. Global interconnects have more parasitic because of larger size than others [7, 8]. These are used to provide clock, power, and long distance communication between functional blocks. These occupy the top layers in a chip. These interconnect parasitic introduce noise sources, increase the propagation delay and power dissipation, and thereby increase the power delay product, which have more effect on circuit performance and reliability. There are different simulation interconnect models which have been considered over the past several decades to calculate these parasitic accurately. Single interconnect is used for circuit-level estimation and parallel interconnect structures are used for bus structures [9,10,11]. In this paper both structures are have been considered for simulation and analysis using spice tool.

3 Interconnect Model

To study the behavior of on-chip interconnect as function of its parameters, electrical models are required. An interconnect can be modeled as R, RC, LC, RLC, or RLGC networks. Generally, signal and clock interconnects are used to model as RC or RLC. These can be represented either in lumped or distributed model [12].

The interconnect parasitic are generally disbursed along its length. They are not lumped into a solitary position. But for fast observation of the effects of RLC parameters, it is frequently helpful to lump the distinctive parts into a solitary circuit element. In view of low switching frequency, only resistance and capacitance will be considered and neglecting inductance. For low frequencies, it is possible to lump parasitic parameters into a single RC model by neglecting the L. There are different configurations of RC Interconnect models namely L, T, and pi [2, 6]. Any model may be considered to calculate propagation delay. But in lower technologies, lumped models are not considered because of inaccuracy. For a RC interconnect a distributed RC model is more accurate. Because the simulation results of a distributed model match more accurate than the lumped model, for computer-aided analysis distributed RC interconnect can be approximated by a lumped multistage RC ladder network. An Elmore delay model has been considered in this paper for analysis purpose which is shown in Fig. 1. This model has linear relation between length and delay [12].

Delay of a RC network is given by

3.1 Interconnect Characteristics

All the wires’ resistance, capacitance, and inductance values are extracted from interconnect geometry structures. Resistance relates to current I to voltage V (carrier flow) [13]. For any current-carrying conductor having some resistance, the resistance is given by Eq. 2:

where ρ represents the resistivity, l is the length, W is the width, and H is the thickness of the interconnect [14]. Generally, capacitance relates charge Q to voltage V (electric energy). Interconnect capacitance consists of two components namely (i) ground capacitance Cg (capacitance between metallic layers and substrate) and (ii) coupling capacitance Cc (capacitance between neighboring interconnects). The coupling capacitance is dominating Cg in the lower technologies because of increasing aspect ratio and decreasing wire spacing. The analytical expressions given in Eqs. 3 and 4 are used to calculate the ground capacitance Cg and coupling capacitance Cc for copper interconnects, which are given below [15]:

Similarly, inductance relates current I to flux H (magnetic energy), and when compared to other parameters, inductance is difficult to extract from the interconnect structures. In case of high-frequency transmission, global interconnects will higher inductance than local interconnects. In this paper, only RC interconnect model has been considered and analyzed for the delay variations in DSM technology.

4 Simulation Results and Discussion

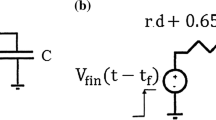

In this paper an attempt has been made to simulate CMOS inverter as driver, consisting interconnect with equivalent R and C derived from analytical expressions and load CL and the circuit is shown in Fig. 2.

The simulation has been carried out in three different ways, namely (i) single interconnect with CMOS driver and load as shown in Fig. 2; (ii) two parallel interconnects with coupling capacitance operating in same switching; and (iii) two parallel interconnects with opposite switching. The technologies considered in this simulation as case 1 are 180, 130, and 65 nm. The lengths of copper wires considered for these technologies are 2, 5, and 10 mm.

In case 2, the technologies considered are as 45, 32, and 22 nm with copper wire lengths of 1, 50, and 100 µm. At lower technologies the lengths of interconnects will be smaller. The simulation results are presented in Tables 1 and 2 and in Figs. 3, 4, 5, and 6. Around 10% variations in delay and PDP values have been observed irrespective of technologies employed with different interconnect lengths, whereas around 5% variation has been observed in delay and PDP values for different interconnect patterns (single, parallel with different switchings) in the same technology with different interconnect lengths. With technology scale down (45, 32, and 22 nm), it is observed that variations in the delay and PDP values are more than 50%. All the simulations were carried out using BSIM4 model files in LT spice simulation tool for above-mentioned technologies.

5 Conclusions

In this paper, an attempt has been made to simulate different copper interconnect structures (single and parallel with different switching events), with a CMOS inverter as driver and load CL and analyzed the effect of interconnect parasitic on circuit performance metrics such as delay and power delay product. It is observed around 10% variation with different interconnect lengths, 5% variation with different interconnect structures when technology is remains constant in the values of delay and PDP. On the other hand, with variations in technology, around 50% variation has been observed in the values of delay and PDP.

References

B. K. Kaushik and S. Sarkar, “Crosstalk Analysis for a CMOS- Gate- Driven Coupled Interconnects” IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, vol. 27, no. 6, pp. 1150–1154, Jun. 2008.

K. G. Verma, Raghuvir Singh, B. K. Kaushik and Manoj Kumar Majumder “Propagation Delay Deviations due to Process Induced Line Parasitic Variations in Global VLSI Interconnects” IEEE Conference on Recent Advances in Intelligent Computational Systems (RAICS), 2011.

C. Venkataiah, M. Tejaswi “A Comparative Study of Interconnect Circuit Techniques for Energy Efficient on-Chip Interconnects” International Journal of Computer Applications (0975 – 8887) Volume 109 – No. 4, January 2015.

International Technology Roadmap for Semiconductors, 2013. [Online] Available: http://public.itrs.net/.

S. Borkar, T. Kamik, S. Narendra, J. Tschanz, A. Keshavarzi and V. De, “Parameter variations and impact on circuits and micro architecture,” in Proc. Design Automation Conference (DAC), pp. 338–342, 2003.

Sandeep Saini “A Novel Approach to Reduce Delay and Power in VLSI Interconnects” M.S. Thesis, Department of Electronics and communication Engineering, Centre for VLSI and Embedded System Technologies, International Institute of Information Technology, Hyderabad, INDIA, May, 2010.

Naeemi and J. D. Meindl, “Design and performance modeling for single-walled carbon nanotubes as local, semiglobal, and global interconnects in gigascale integrated systems,” IEEE Trans. Electron Devices, vol. 54, no. 1, pp. 26–37, Jan. 2007.

Gargi Khanna, Rajeevan Chandel, Ashwani Kumar Chandel and Sankar Sarkar “Analysis of non-ideal effects in coupled VLSI interconnects with active and passive load variations” Microelectronics International, Vol. 26 Iss 1 pp. 3–9(2009).

Sandeep Saini, A. Mahesh Kumar, Sreehari Veeramachaneni, M.B. Srinivas, “Alternative approach to Buffer Insertion for Delay and Power eduction in VLSI Interconnects”, VLSI design 2010, 3rd to 7th January 2010, Banglore, pages 411–416.

Kaushik, B.K., Sarkar, S., Agarwal, R.P. and Joshi, R.C. (2006b), “Cross-talk analysis and repeater insertion in interconnects”, Microelectronics International, Vol. 23 No. 3, pp. 55–63.

J. M. Rabaey, A. Chandrakasan, and B. Nikolic, “Digital Integrated Circuits” Prentice Hall, New Delhi, 2nd Edition, 2006.

S. M. Kang and Yusuf Leblebici, “CMOS Digital Integrated Circuits (Analysis and Design)”, 3rd ed. McGraw-Hill 2013.

Joshi, A., Soni, G “A comparative analysis of copper and carbon nanotubes based global interconnects.” Int. J. Eng. Manag. Sci. (Alied Journals-IJEMS) ISSN-2348–3733, 2(5), (2015).

Das, D., Rahaman, H “Analysis of crosstalk in single- and multiwall carbon nanotube interconnects and its impact on gate oxide reliability.” IEEE Trans. Nanotechnol. 10(6), 1362, 1370 (2011).

V. Ramesh Kumar, A. Alam, B. K. Kaushik, A. Patnaik (2015) “An unconditionally stable FDTD model for crosstalk analysis of VLSI interconnects,” IEEE Transaction components, packaging and Manufacturing Technology, 5(12), 1810–1817.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2018 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Venkataiah, C., Satyaprasad, K., Jaya Chandra Prasad, T. (2018). Effect of Line Parasitic Variations on Delay and Energy of Global On-Chip VLSI Interconnects in DSM Technology. In: Satapathy, S., Bhateja, V., Chowdary, P., Chakravarthy, V., Anguera, J. (eds) Proceedings of 2nd International Conference on Micro-Electronics, Electromagnetics and Telecommunications. Lecture Notes in Electrical Engineering, vol 434. Springer, Singapore. https://doi.org/10.1007/978-981-10-4280-5_23

Download citation

DOI: https://doi.org/10.1007/978-981-10-4280-5_23

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-4279-9

Online ISBN: 978-981-10-4280-5

eBook Packages: EngineeringEngineering (R0)