Abstract

Placement is a critical step in the modern backend design flow for integrated circuits (ICs). It needs to determine the locations of millions of instances and meanwhile optimizes for multiple objectives such as wirelength, routability, timing, and so on. These objectives cannot be accurately evaluated until routing and other succeeding stages are performed. As a result, modern placement algorithm follows an iterative procedure for these cross-layer objectives, which is time-consuming. Recent advances in machine learning and its acceleration bring opportunities to speed up placement algorithms from perspectives of both hardware acceleration and cross-layer modeling. This book chapter will survey recent studies on leveraging deep learning frameworks to accelerate kernel placement solvers as well as integrating machine learning models to speed up cross-layer optimization. We hope this line of studies can broaden the applications of machine learning techniques in IC design automation and stimulate more researches in related fields.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Markov, I.L., Hu, J., Kim, M.C.: Progress and challenges in VLSI placement research. Proc. IEEE 103(11), 1985–2003 (2015)

Viswanathan, N., Chu, C.C.: Fastplace: Efficient analytical placement using cell shifting, iterative local refinement, and a hybrid net model. IEEE TCAD 24(5), 722–733 (2005)

Viswanathan, N., Pan, M., Chu, C.: FastPlace 3.0: a fast multilevel quadratic placement algorithm with placement congestion control. In: IEEE/ACM Asia and South Pacific Design Automation Conference (ASPDAC), pp. 135–140. IEEE, Piscataway (2007)

Kim, M.C., Lee, D.J., Markov, I.L.: Simpl: An effective placement algorithm. IEEE TCAD 31(1), 50–60 (2012)

He, X., Huang, T., Xiao, L., Tian, H., Young, E.F.Y.: Ripple: a robust and effective routability-driven placer. IEEE TCAD 32(10), 1546–1556 (2013)

Lin, T., Chu, C., Shinnerl, J.R., Bustany, I., Nedelchev, I.: POLAR: a high performance mixed-size wirelengh-driven placer with density constraints. IEEE TCAD 34(3), 447–459 (2015)

Kahng, A.B., Reda, S., Wang, Q.: Architecture and details of a high quality, large-scale analytical placer. In: ICCAD, pp. 891–898. IEEE, Piscataway (2005)

Kahng, A.B., Wang, Q.: A faster implementation of APlace. In: ISPD, pp. 218–220. ACM, New York (2006)

Chan, T., Cong, J., Sze, K.: Multilevel generalized force-directed method for circuit placement. In: ISPD, pp. 185–192. ACM (2005)

Chan, T.F., Sze, K., Shinnerl, J.R., Xie, M.: mPL6: Enhanced multilevel mixed-size placement with congestion control. In: Modern Circuit Placement. Springer, Berlin (2007)

Chen, T.C., Jiang, Z.W., Hsu, T.C., Chen, H.C., Chang, Y.W.: Ntuplace3: an analytical placer for large-scale mixed-size designs with preplaced blocks and density constraints. IEEE TCAD 27(7), 1228–1240 (2008)

Huang, C., Lee, H., Lin, B., Yang, S., Chang, C., Chen, S., Chang, Y., Chen, T., Bustany, I.: NTUplace4dr: a detailed-routing-driven placer for mixed-size circuit designs with technology and region constraints. IEEE TCAD 37(3), 669–681 (2018)

Lu, J., Zhuang, H., Chen, P., Chang, H., Chang, C.C., Wong, Y.C., Sha, L., Huang, D., Luo, Y., Teng, C.C., et al.: ePlace-MS: electrostatics-based placement for mixed-size circuits. IEEE TCAD 34(5), 685–698 (2015)

Cheng, C.K., Kahng, A.B., Kang, I., Wang, L.: RePlAce: Advancing solution quality and routability validation in global placement. IEEE TCAD (2018)

Cadence Innovus. http://www.cadence.com

Synopsys IC Compiler. http://www.synopsys.com

Ludwin, A., Betz, V., Padalia, K.: High-quality, deterministic parallel placement for FPGAs on commodity hardware. In: FPGA, pp. 14–23. ACM, New York (2008)

Lin, T., Chu, C., Wu, G.: Polar 3.0: An ultrafast global placement engine. In: ICCAD, pp. 520–527 (2015)

Li, W., Li, M., Wang, J., Pan, D.Z.: Utplacef 3.0: a parallelization framework for modern FPGA global placement. In: ICCAD, pp. 908–914 (2017)

Goodfellow, I., Bengio, Y., Courville, A.: Deep Learning. MIT Press, Cambridge (2016)

Lin, Y., Jiang, Z., Gu, J., Li, W., Dhar, S., Ren, H., Khailany, B., Pan, D.Z.: Dreamplace: deep learning toolkit-enabled GPU acceleration for modern VLSI placement. IEEE TCAD (2020)

Paszke, A., Gross, S., Massa, F., Lerer, A., Bradbury, J., Chanan, G., Killeen, T., Lin, Z., Gimelshein, N., Antiga, L., et al.: PyTorch: an imperative style, high-performance deep learning library. In: Conference on Neural Information Processing Systems (NIPS), pp. 8024–8035. Curran Associates (2019)

Lin, Y., Li, W., Gu, J., Ren, H., Khailany, B., Pan, D.Z.: Abcdplace: accelerated batch-based concurrent detailed placement on multithreaded cpus and GPUs. IEEE Trans. Comput.-Aided Design Integr. Circuits Syst. 39(12), 5083–5096 (2020)

Lin, Y., Pan, D.Z., Ren, H., Khailany, B.: Dreamplace 2.0: Open-source GPU-accelerated global and detailed placement for large-scale VLSI designs. In: 2020 China Semiconductor Technology International Conference (CSTIC), pp. 1–4 (2020)

Gu, J., Jiang, Z., Lin, Y., Pan, D.Z.: Dreamplace 3.0: multi-electrostatics based robust VLSI placement with region constraints. In: 2020 IEEE/ACM International Conference On Computer Aided Design (ICCAD), pp. 1–9 (2020)

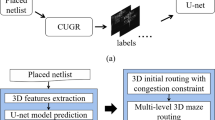

Liu, S., Sun, Q., Liao, P., Lin, Y., Yu, B.: Global placement with deep learning-enabled explicit routability optimization. In: DATE. Virtual Conference (2021)

Guo, Z., Mai, J., Lin, Y.: Ultrafast CPU/GPU kernels for density accumulation in placement. In: DAC. San Francisco (2021)

Lin, Y.: GPU acceleration in VLSI back-end design: overview and case studies. In: Proceedings of the 39th International Conference on Computer-Aided Design, ICCAD ’20. Association for Computing Machinery, New York (2020)

Spindler, P., Schlichtmann, U., Johannes, F.M.: Abacus: Fast legalization of standard cell circuits with minimal movement. In: ISPD, ISPD ’08, pp. 47–53. Association for Computing Machinery, New York (2008)

Pan, M., Viswanathan, N., Chu, C.: An efficient and effective detailed placement algorithm. In: ICCAD, pp. 48–55 (2005)

Kingma, D.P., Ba, J.: Adam: A method for stochastic optimization. In: ICLR (Poster) (2015)

Cheng, C.K., Kahng, A.B., Kang, I., Wang, L.: Replace: advancing solution quality and routability validation in global placement. IEEE TCAD (2018)

Hsu, M.K., Chang, Y.W., Balabanov, V.: TSV-aware analytical placement for 3D IC designs. In: DAC, pp. 664–669. ACM, New York (2011)

Hsu, M.K., Balabanov, V., Chang, Y.W.: TSV-aware analytical placement for 3-D IC designs based on a novel weighted-average wirelength model. DAC 32(4), 497–509 (2013)

Lu, J., Chen, P., Chang, C.C., Sha, L., Huang, D.J.H., Teng, C.C., Cheng, C.K.: ePlace: Electrostatics-based placement using fast fourier transform and Nesterov’s method. ACM TODAES 20(2), 17 (2015)

Lin, C.X., Wong, M.D.: Accelerate analytical placement with GPU: a generic approach. In: DATE, pp. 1345–1350. IEEE, Piscataway (2018)

Gessler, F., Brisk, P., Stojilovič, M.: A shared-memory parallel implementation of the replace global cell placer. In: International Conference on VLSI Design, pp. 78–83. IEEE, Piscataway (2020)

Crow, F.C.: Summed-area tables for texture mapping. In: SIGGRAPH ’84, pp. 207–212. ACM, New York (1984)

Makhoul, J.: A fast cosine transform in one and two dimensions. IEEE Trans. Signal Process. 28(1), 27–34 (1980)

Bustany, I.S., Chinnery, D., Shinnerl, J.R., Yutsis, V.: ISPD 2015 benchmarks with fence regions and routing blockages for detailed-routing-driven placement. In: ISPD, pp. 157–164 (2015)

Darav, N.K., Kennings, A., Tabrizi, A.F., Westwick, D., Behjat, L.: Eh?Placer: a high-performance modern technology-driven placer. ACM TODAES 21(3), 1–27 (2016)

Chow, W., Kuang, J., Tu, P., Young, E.F.Y.: Fence-aware detailed-routability driven placement. In: ACM Workshop on System Level Interconnect Prediction (SLIP), pp. 1–7 (2017)

Birgin, E.G., Martínez, J.M.: Practical augmented Lagrangian methods for constrained optimization. SIAM (2014)

Jin, C., Ge, R., Netrapalli, P., Kakade, S.M., Jordan, M.I.: How to escape saddle points efficiently. In: International Conference on Machine Learning (ICML), pp. 1724–1732. PMLR (2017)

Liu, W.H., Li, Y.L., Koh, C.K.: A fast maze-free routing congestion estimator with hybrid unilateral monotonic routing. In: ICCAD, pp. 713–719 (2012)

Viswanathan, N., Alpert, C., Sze, C., Li, Z., Wei, Y.: The DAC 2012 routability-driven placement contest and benchmark suite. In: DAC, pp. 774–782. ACM, New York (2012)

Xie, Z., Huang, Y.H., Fang, G.Q., Ren, H., Fang, S.Y., Chen, Y., Hu, J.: Routenet: routability prediction for mixed-size designs using convolutional neural network. In: 2018 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pp. 1–8. IEEE, Piscataway (2018)

Kirby, R., Godil, S., Roy, R., Catanzaro, B.: Congestionnet: routing congestion prediction using deep graph neural networks. In: 2019 IFIP/IEEE 27th International Conference on Very Large Scale Integration (VLSI-SoC), pp. 217–222. IEEE, Piscataway (2019)

Alawieh, M.B., Li, W., Lin, Y., Singhal, L., Iyer, M.A., Pan, D.Z.: High-definition routing congestion prediction for large-scale FPGAs. In: 2020 25th Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 26–31. IEEE, Piscataway (2020)

Liang, R., Xiang, H., Pandey, D., Reddy, L., Ramji, S., Nam, G.J., Hu, J.: DRC hotspot prediction at sub-10 nm process nodes using customized convolutional network. In: Proceedings of the 2020 International Symposium on Physical Design, pp. 135–142 (2020)

Spindler, P., Johannes, F.M.: Fast and accurate routing demand estimation for efficient routability-driven placement. In: DATE, pp. 1226–1231 (2007)

Meng, Y., Li, W., Lin, Y., Pan, D.Z.: elfPlace: electrostatics-based placement for large-scale heterogeneous FPGAs. IEEE TCAD (2021)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this chapter

Cite this chapter

Lin, Y., Guo, Z., Mai, J. (2022). Deep Learning Framework for Placement. In: Ren, H., Hu, J. (eds) Machine Learning Applications in Electronic Design Automation. Springer, Cham. https://doi.org/10.1007/978-3-031-13074-8_9

Download citation

DOI: https://doi.org/10.1007/978-3-031-13074-8_9

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-13073-1

Online ISBN: 978-3-031-13074-8

eBook Packages: Mathematics and StatisticsMathematics and Statistics (R0)