Abstract

Chapter 8 focuses on timing closure, and its perspective is particularly unique. It offers a comprehensive coverage of timing analysis and relevant optimizations in placement, routing, and netlist restructuring. Timing-driven placement (Sect. 8.3) minimizes signal delays when assigning circuit elements to locations. Timing-driven routing (Sect. 8.4) minimizes signal delays when selecting routing topologies and specific routes. Physical synthesis (Sect. 8.5) improves timing by making changes to the netlist.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Notes

- 1.

- 2.

This methodology is intended for layout of circuits directly represented by graphs rather than circuits partitioned into high-level modules. However, this methodology can also be adapted to assign budgets to entire modules instead of circuit elements.

- 3.

A multi-fanout net ei has multiple source-sink delays, so ZSA must be adjusted accordingly.

- 4.

Whereas logic synthesis maps an RTL description to a set of gates to realize the same functionality, physical synthesis transforms this gate-level netlist to a layout that can be realized (etched) on silicon. The latter includes local and global optimizations, such as timing, that take physical properties into account and which are the focus of Sect. 8.5.

- 5.

In hierarchical design flows, different designers concurrently perform top-level placement and block-level placement.

- 6.

These buffers are legalized immediately when added to the clock network.

- 7.

These include post-clock network synthesis optimizations, post-global routing optimizations, and post-detailed routing optimizations.

- 8.

For simplicity, we refer to the general foundry naming, thereby ignoring marketing labels and optical shrink specifics.

References

C. J. Alpert, M. Hrkić, J. Hu and S. T. Quay, Fast and Flexible Buffer Trees that Navigate the Physical Layout Environment, Proc. Design Autom. Conf., 2004, pp. 24-29. https://doi.org/10.1145/996566.996575

C. J. Alpert, J. Hu, S. S. Sapatnekar and C. N. Sze, “Accurate Estimation of Global Buffer Delay Within a Floorplan”, IEEE Trans. on CAD 25(6) (2006), pp. 1140-1146. https://doi.org/10.1109/TCAD.2005.855889

C. J. Alpert, S. K. Karandikar, Z. Li, G.-J. Nam, S. T. Quay, H. Ren, C. N. Sze, P. G. Villarrubia and M. C. Yildiz, “Techniques for Fast Physical Synthesis”, Proc. IEEE 95(3) (2007), pp. 573-599. https://doi.org/10.1109/JPROC.2006.890096

C. J. Alpert, D. P. Mehta and S. S. Sapatnekar, eds., Handbook of Algorithms for Physical Design Automation, Auerbach Publ., 2008, 2019. ISBN 978-0367403478.

M. Burstein and M. N. Youssef, Timing Influenced Layout Design, Proc. Design Autom. Conf., 1985, pp. 124-130. https://doi.org/10.1109/DAC.1985.1585923

T. F. Chan, J. Cong and E. Radke, A Rigorous Framework for Convergent Net Weighting Schemes in Timing-Driven Placement, Proc. Intl Conf. CAD, 2009, pp. 288-294. https://doi.org/10.1145/1687399.1687454

K.-H. Chang, I. L. Markov and V. Bertacco, “Postplacement Rewiring by Exhaustive Search for Functional Symmetries”, ACM Trans. on Design Autom. of Electronic Sys. 12(3) (2007), pp. 1-21. https://doi.org/10.1145/1255456.1255469

A. Chowdhary, K. Rajagopal, S. Venkatesan, T. Cao, V. Tiourin, Y. Parasuram and B. Halpin, How Accurately Can We Model Timing in a Placement Engine?, Proc. Design Autom. Conf., 2005, pp. 801-806. https://doi.org/10.1145/1065579.1065792

J. Cong, A. B. Kahng, G. Robins, M. Sarrafzadeh and C. K. Wong, Provably Good Algorithms for Performance-Driven Global Routing, Proc. Int. Symp. Circuits Syst., 1992, pp. 2240-2243. https://doi.org/10.1109/ISCAS.1992.230514

W. C. Elmore, “The Transient Response of Damped Linear Networks with Particular Regard to Wideband Amplifiers”, J. Applied Physics 19(1) (1948), pp. 55-63. https://doi.org/10.1063/1.1697872

H. Eisenmann and F. M. Johannes, Generic Global Placement and Floorplanning, Proc. Design Autom. Conf., 1998, pp. 269-274. https://doi.org/10.1145/277044.277119

S. Ghiasi, E. Bozorgzadeh, P.-K. Huang, R. Jafari and M. Sarrafzadeh, “A Unified Theory of Timing Budget Management”, IEEE Trans. on CAD 25(11) (2006), pp. 2364-2375. https://doi.org/10.1109/ICCAD.2004.1382657

B. Halpin, C. Y. R. Chen and N. Sehgal, Timing Driven Placement Using Physical Net Constraints, Proc. Design Autom. Conf., 2001, pp. 780-783. https://doi.org/10.1145/378239.379065

T. I. Kirkpatrick and N. R. Clark, “PERT as an Aid to Logic Design”, IBM J. Research and Development 10(2) (1966), pp. 135-141. https://doi.org/10.1147/RD.102.0135

J. Lillis, C.-K. Cheng, T.-T. Y. Lin and C.-Y. Ho, New Performance Driven Routing Techniques with Explicit Area/Delay Tradeoff and Simultaneous Wire Sizing, Proc. Design Autom. Conf., 1996, pp. 395-400. https://doi.org/10.1109/DAC.1996.545608

M. Orshansky and K. Keutzer, A General Probabilistic Framework for Worst Case Timing Analysis, Proc. Design Autom. Conf., 2002, pp. 556-561. https://doi.org/10.1109/DAC.2002.1012687

M. Orshansky, S. Nassif and D. Boning, Design for Manufacturability and Statistical Design: A Constructive Approach, Springer, 2008. https://doi.org/10.1007/978-0-387-69011-7

L. Capodieci, Evolving Physical Design Paradigms in the Transition from 20/14 to 10nm Process Technology Nodes, Proc. Intl Conf. on CAD, 2014, p. 573. https://doi.org/10.1109/ICCAD.2014.7001407

D. A. Papa, T. Luo, M. D. Moffitt, C. N. Sze, Z. Li, G.-J. Nam, C. J. Alpert and I. L. Markov, “RUMBLE: An Incremental, Timing-Driven, Physical-Synthesis Optimization Algorithm”, IEEE Trans. on CAD 27(12) (2008), pp. 2156-2168. https://doi.org/10.1109/TCAD.2008.2006155

S. M. Plaza, I. L. Markov and V. Bertacco, “Optimizing Nonmonotonic Interconnect Using Functional Simulation and Logic Restructuring”, IEEE Trans. on CAD 27(12) (2008), pp. 2107-2119. https://doi.org/10.1109/TCAD.2008.2006156

K. Rajagopal, T. Shaked, Y. Parasuram, T. Cao, A. Chowdhary and B. Halpin, Timing Driven Force Directed Placement with Physical Net Constraints, Proc. Int. Symp. Phys. Design, 2003, pp. 60-66. https://doi.org/10.1145/640000.640016

H. Ren, D. Z. Pan and D. S. Kung, “Sensitivity Guided Net Weighting for Placement Driven Synthesis”, IEEE Trans. on CAD 24(5) (2005), pp. 711-721. https://doi.org/10.1109/TCAD.2005.846367

J. A. Roy, N. Viswanathan, G.-J. Nam, C. J. Alpert and I. L. Markov, CRISP: Congestion Reduction by Iterated Spreading During Placement, Proc. Int. Conf. on CAD, 2009, pp. 357-362. https://doi.org/10.1145/1687399.1687467

M. Sarrafzadeh, M. Wang and X. Yang, Modern Placement Techniques, Springer, 2012. ISBN 978-1475737820. https://doi.org/10.1007/978-1-4757-3781-3.

R. S. Shelar, “Routing with Constraints for Post-Grid Clock Distribution in Microprocessors”, IEEE Trans. on CAD 29(2) (2010), pp. 245-249. https://doi.org/10.1109/TCAD.2009.2040012

R. S. Shelar and M. Patyra, “Impact of Local Interconnects on Timing and Power in a High Performance Microprocessor”, IEEE Trans. on CAD 32(10) (2013), pp. 1623-1627. https://doi.org/10.1109/TCAD.2013.2266404

I. Sutherland, R. F. Sproull and D. Harris, Logical Effort: Designing Fast CMOS Circuits, Morgan Kaufmann, 1999. ISBN 978-155860-557-2.

H. Tennakoon and C. Sechen, “Nonconvex Gate Delay Modeling and Delay Optimization”, IEEE Trans. on CAD 27(9) (2008), pp. 1583-1594. https://doi.org/10.1109/TCAD.2008.927758

M. Vujkovic, D. Wadkins, B. Swartz and C. Sechen, Efficient Timing Closure Without Timing Driven Placement and Routing, Proc. Design Autom. Conf., 2004, pp. 268-273. https://doi.org/10.1145/996566.996646

J. Westra and P. Groeneveld, Is Probabilistic Congestion Estimation Worthwhile?, Proc. Sys. Level Interconnect Prediction, 2005, pp. 99-106. https://doi.org/10.1145/1053355.1053377

R. Fischbach, J. Lienig, T. Meister, From 3D Circuit Technologies and Data Structures to Interconnect Prediction, Proc. Sys. Level Interconnect Prediction, 2009, pp. 77-84. https://doi.org/10.1145/1572471.1572485

Y. Xie, J. Cong and S. Sapatnekar, eds., Three-Dimensional Integrated Circuit Design: EDA, Design and Microarchitectures, Springer, 2010. https://doi.org/10.1007/978-1-4419-0784-4

J. Knechtel, J. Lienig, Physical Design Automation for 3D Chip Stacks – Challenges and Solutions, Proc. Int. Symp. on Phys. Design, 2016, pp. 3-10. https://doi.org/10.1145/2872334.2872335

J. Lienig, J. Scheible, Fundamentals of Layout Design for Electronic Circuits. Springer, ISBN 978-3-030-39283-3, 2020. https://doi.org/10.1007/978-3-030-39284-0

Author information

Authors and Affiliations

Exercises

Exercises

Exercise 1: Static Timing Analysis

Given the logic circuit below, (a) draw the timing graph, and determine the (b) AAT, (c) RAT, and (d) slack of each node. The AATs of the inputs are in angular brackets, the delays are in parentheses, and the RAT of the output is in square brackets.

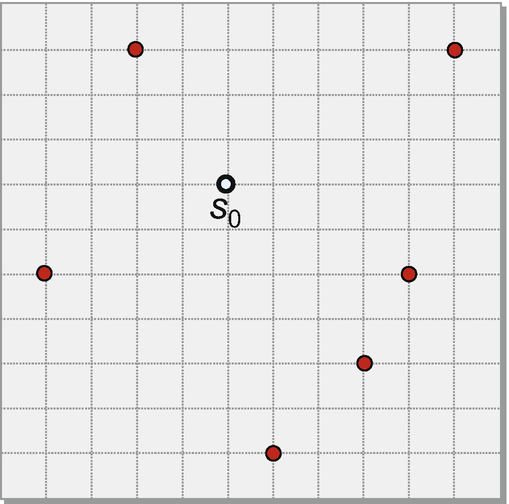

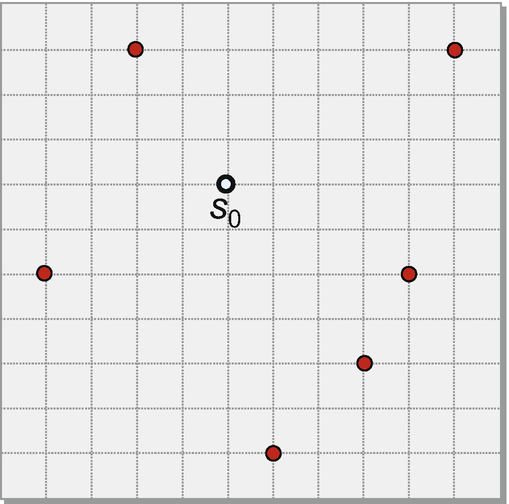

Exercise 2: Timing-Driven Routing

Given the terminal locations of a signal net, assume that all distances are Manhattan, and that no Steiner point is used when routing. Construct the spanning tree T, and calculate radius(T) and cost(T), for each of the following:

-

(a)

Prim-Dijkstra trade-off with γ = 0 (Prim’s MST algorithm)

-

(b)

Prim-Dijkstra trade-off with γ = 1 (Dijkstra’s algorithm)

-

(c)

Prim-Dijkstra trade-off with γ = 0.5

Exercise 3: Buffer Insertion for Timing Improvement

For the logic circuit and load capacitances on the following page, assume that available gate sizes and timing performances are similar to those in Fig. 8.12. Assume that gate delay always increases linearly with load capacitance. Let the input capacitance of buffer y be 0.5 fF, 1 fF, and 2 fF with sizes A, B, and C, respectively. Determine the size for buffer y that minimizes the AAT of sink c.

Exercise 4: Timing Optimization

List at least two timing optimizations covered only in this chapter (not mentioned beforehand). Describe these optimizations in your own words and discuss scenarios in which (1) they can be useful and (2) they can be harmful.

Exercise 5: Cloning vs. Buffering

List and explain scenarios where cloning results in better timing improvements than buffering, and vice versa. Explain why both methods are necessary for timing-driven physical synthesis.

Exercise 6: Physical Synthesis

In terms of timing corrections such as buffering, gate sizing, and cloning, when are their reverse transformations useful? In what situations will a given timing correction cause the design to be illegal? Explain for each timing correction.

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this chapter

Cite this chapter

Kahng, A.B., Lienig, J., Markov, I.L., Hu, J. (2022). Timing Closure. In: VLSI Physical Design: From Graph Partitioning to Timing Closure. Springer, Cham. https://doi.org/10.1007/978-3-030-96415-3_8

Download citation

DOI: https://doi.org/10.1007/978-3-030-96415-3_8

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-030-96414-6

Online ISBN: 978-3-030-96415-3

eBook Packages: EngineeringEngineering (R0)