Abstract

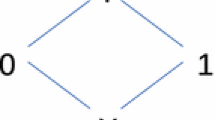

Symbolic Trajectory Evaluation (STE) is a model checking algorithm that mixes the use of lattice structures with binary decision diagrams. In addition to this algorithmic decision procedure for the logic, there is also a sound and complete set of inference rules for the logic. Together, these make STE an attractive candidate for a verification system. In this talk we will briefly introduce the underlying theory of STE. We will then discuss the challenges we faced in making STE the basic model checker in the Voss hardware verification system and how the inference rules were used to extend the capabilities of the system. The emphasis of the talk will be on the process of taking a nice theory and making it practically useful.

Chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 1998 Springer Science+Business Media Dordrecht

About this chapter

Cite this chapter

Seger, C. (1998). From Lattices to Practical Formal Hardware Verification. In: Gries, D., de Roever, WP. (eds) Programming Concepts and Methods PROCOMET ’98. IFIP — The International Federation for Information Processing. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-35358-6_2

Download citation

DOI: https://doi.org/10.1007/978-0-387-35358-6_2

Publisher Name: Springer, Boston, MA

Print ISBN: 978-1-4757-6299-0

Online ISBN: 978-0-387-35358-6

eBook Packages: Springer Book Archive