Abstract

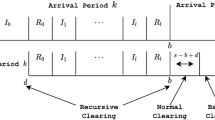

An analytical model for the performance analysis of a novel input access scheme for an ATM switch is developed and presented in this paper. The interconnection network of the ATM switch is internally nonblocking and is provided with N input queues per each input port for a switch of size N × N. That is, each input port maintains a separate queue for each output port so as to reduce the head-of-line (HOL) blocking of conventional input queuing switches. Each input is allowed to send just one cell per slot time, and each output port is allowed to accept just one cell per slot time. Under saturated conditions the switch was analyzed and a closed-form solution for the maximum throughput is derived. Using a tagged input queue approach, an analytical model for evaluating the switch performance under an i.i.d. Bernoulli traffic for different offered traffic loads is developed. The switch throughput, mean cell delay, and cell loss probability are computed from the analytical model. The accuracy of the analytical model is verified using simulation.

The original version of this chapter was revised: The copyright line was incorrect. This has been corrected. The Erratum to this chapter is available at DOI: 10.1007/978-0-387-35353-1_28

Chapter PDF

Similar content being viewed by others

References

Abramowitz, M. and Stegun, I.A. (1972) Handbook of Mathematical Functions with Formulas, Graphs, and Mathematical Tables

John Wiley and Sons. Awdeh, R.Y. and Mouftah, H.T. (1995) Survey of ATM Switch Architectures.

Computer Networks and ISDN Systems, Vol. 27, No. 12, 1567–1613.

Anderson, T.E., Owicki, S.S., Saxe, J.B. and Thacker, C.P. (1993) Highspeed Switch Scheduling for Local-area Networks. ACM Transactions on Computer Systems, Vol. 11, No. 4, 319–352.

LaMaire, R.O. and Serpanos, D.N. (1994) Two-Dimentional Round-Robin Schedulers for Packet Switches with Multiple Input Queues. IEEE/ACM Transactions on Networking, Vol. 2, No. 5, 471–82.

McKeown, N. (1994) Scheduling Algorithms for Input-Queued Cell Switches. Ph.D. thesis, University of California at Berkeley.

Mckeown, N., Varaiya, P., and Walrand, J. (1994) Scheduling Cells in an Input-Queued Switch. Electronics Letters,Vol. 29, No. 25 21742175.

Neuts, M.F. (1981) Matrix-Geometric Solutions in Stochastic Models Johns Hopkins Universi ty Press.

Pattavina, A. and Bruzzi, G. (1993) Analysis of Input and Output Queueing for Nonblocking ATM Switches. IEEE/ACM Trans. on Networking,Vol. 1, No. 3 314–328.

Youn Chan Jung and Chong Kwan Un (1994) Performance Analysis of Packet Switches with Input and Output Buffers. Computer Networks and ISDN Systems,Vol. 26, No. 12 1559–1580.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2000 IFIP International Federation for Information Processing

About this chapter

Cite this chapter

Nong, G., Muppala, J.K., Hamdi, M. (2000). Performance analysis of input queueing ATM switches with parallel iterative matching scheduling. In: Kouvatsos, D. (eds) Performance Analysis of ATM Networks. ATM 1997. IFIP — The International Federation for Information Processing, vol 29. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-35353-1_10

Download citation

DOI: https://doi.org/10.1007/978-0-387-35353-1_10

Publisher Name: Springer, Boston, MA

Print ISBN: 978-1-4757-6160-3

Online ISBN: 978-0-387-35353-1

eBook Packages: Springer Book Archive