Abstract

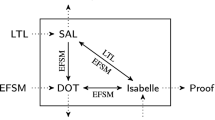

We describe a methodology for the formal verification of complex out-of-order pipelines as they may be used as execution units in out-of-order processors. The pipelines may process multiple instructions simultaneously, may have branches and cycles in the pipeline structure, may have variable latency, and may reorder instructions internally. The methodology combines model-checking for the verification of the pipeline control, and theorem proving for the verification of the pipeline functionality. In order to combine both techniques, we formally verify that the FairCTL operators defined in μ-calculus match their intended semantics expressed in a form where computation traces are explicit, since this form is better suited for theorem proving. This allows the formally safe translation of model-checked properties of the pipeline control into a theorem-proving friendly form, which is used for the verification of the overall correctness, including the functionality. As an example we prove the correctness of the pipeline of a multiplication/division floating point unit with all the features mentioned above.

The work reported here was done while the author was affiliated with Saarland University.

Chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

References

M. Aagaard, R. B. Jones, R. Kaivola, K. R. Kohatsu, and C.-J. H. Seger. Formal verification of iterative algorithms in microprocessors. In DAC-00. ACM/IEEE, 2000.

M. Aagaard and M. Leeser. Reasoning about pipelines with structural hazards. In TPCD’94, volume 901 of LNCS. Springer, 1994.

S. Berezin, A. Biere, E. Clarke, and Y. Zhu. Combining symbolic model checking with uninterpreted functions for out-of-order processor verification. In FMCAD’ 98, LNCS 1522. Springer, 1998.

C. Berg and C. Jacobi. Formal verification of the vamp floating point unit. In CHARME 2001, LNCS 2144. Springer, 2001.

R. E. Bryant, S. German, and M. N. Velev. Processor verification using efficient reductions of the logic of uninterpreted functions to propositional logic. ACM Trans. on Computational. Logic (TOCL), 2(1):1–41, Jan 2001.

J. R. Burch and D. L. Dill. Automatic verification of pipelined microprocessor control. In CAV’94, LNCS 818. Springer, 1994.

E. M. Clarke, O. Grumberg, and D. A. Peled. Model Checking. MIT Press, Cambridge, Massachusetts, 1999.

E. A. Emerson and E. M. Clarke. Characterizing correctness properties of parallel programs using fixpoints. In Automata, Languages and Programming, LNCS 85. Springer, 1980.

P.-H. Ho, A. J. Isles, and T. Kam. Formal verification of pipeline control using controlled token nets and abstract interpretation. In ICCAD-98. ACM, 1998.

R. Hosabettu, G. Gopalakrishnan, and M. Srivas. Verifying microarchitectures that support speculation and exceptions. In CAV’ 00, volume 1855 of LNCS. Springer, 2000.

C. N. Ip and D. L. Dill. Better verification through symmetry. Formal Methods in System Design, 9(1–2):41–75, 1996.

C. Jacobi. Formal Verification of a Fully IEEE Compliant Floating Point Unit. PhD thesis, Saarland University, Germany, 2002. handed in; draft available at http://www-wjp.cs.uni-sb.de/~cj/phd.ps.

D. Kroening. Formal Verification of Pipelined Microprocessors. PhD thesis, Saarland University, Computer Science Department, 2001.

K. L. McMillan. A methodology for hardware verification using compositional model checking. Science of Computer Programming, 37(1–3):279–309, 2000.

S. Owre, N. Shankar, and J. M. Rushby. PVS: A prototype verification system. In CADE 11, volume 607 of LNAI, pages 748–752. Springer, 1992.

S. Rajan, N. Shankar, and M. K. Srivas. An integration of model checking with automated proof checking. In CAV’95, volume 939. Springer, 1995.

J. Sawada and W. A. Hunt, Jr. Processor verification with precise exceptions and speculative execution. In CAV’ 98, volume 1427 of LNCS. Springer, 1998.

K. Schneider and D. W. Hoffmann. A HOL conversion for translating linear time temporal logic to-automata. In TPHOL 99, volume 1690 of LNCS. Springer, 1999.

R. M. Tomasulo. An efficient algorithm for exploiting multiple arithmetic units. In IBM Journal of Research and Development, volume 11(1), pages 25–33. IBM, 1967.

M. N. Velev and R. E. Bryant. Formal verification of superscalar microprocessors with multicycle functional units, exception, and branch prediction. In DAC’ 00. ACM/IEEE, 2000.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2002 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Jacobi, C. (2002). Formal Verification of Complex Out-of-Order Pipelines by Combining Model-Checking and Theorem-Proving. In: Brinksma, E., Larsen, K.G. (eds) Computer Aided Verification. CAV 2002. Lecture Notes in Computer Science, vol 2404. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-45657-0_23

Download citation

DOI: https://doi.org/10.1007/3-540-45657-0_23

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-43997-4

Online ISBN: 978-3-540-45657-5

eBook Packages: Springer Book Archive