Abstract

A new In0.53Ga0.47As based laterally diffused power MOSFET (LDMOS) with the tunneling junction at the drain side has been proposed. The tunneling mechanism increases the drain current which results in reduced ON state resistance and increased peak transconductance significantly as compared with In0.53Ga0.47As LDMOS. Using 2-D numerical simulations, we demonstrate that the proposed device exhibits ~24% reduction in ON state resistance and ~16% improvement in peak transconductance as compared with In0.53Ga0.47As LDMOS without affecting the breakdown voltage.

Similar content being viewed by others

1 Introduction

SILICON has been widely used material for power MOSFET devices in low to medium voltage power applications [1, 2]. However, Si has reached its highest performance level and extensive research has been carried out for establishing new materials. Out of these materials, In0.53Ga0.47As is attracting researchers for power device applications as it has a very high electron mobility as compared to that of silicon [3], which may be exploited to obtain very small ON resistance and higher transconductance [4, 5]. Lower ON resistance decreases the conduction losses and higher transconductance increases the switching speed of the device.

In this paper, we propose a novel In0.53Ga0.47As based LDMOS with tunneling junction at the drain end (TLDMOS). The TLDMOS provides lower ON resistance due to the conductivity modulation of the drift region stimulated by the band to band tunneling at the drain end. Using 2D numerical simulation, we demonstrate that In0.53Ga0.47As based TLDMOS exhibits a significantly improved performance as compared with In0.53Ga0.47As based LDMOS in terms of ON state resistance and peak transconductance without compromising with the breakdown voltage.

2 Proposed Device Structure

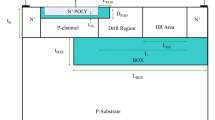

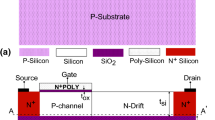

The schematic cross sectional view of In0.53Ga0.47As LDMOS and the proposed In0.53Ga0.47As TLDMOS is shown in Fig. 102.1. A 200 nm thick In0.53Ga0.47As material is grown as an epitaxial layer on the lattice matched 1.4 µm thick InP material. The doping level of p body is 2 × 1017 cm−3, the doping level of n− drift is 1 × 1016 cm−3 and doping level of n+ source/drain is 1 × 1019 cm−3. The p-channel length is 0.5 µm and drift region length is taken to be 3 µm. A 30 nm thick Al2O3 is used as a dielectric as In0.53Ga0.47As material does not have a native oxide. The Al2O3 may be deposited by atomic layer deposition to give high quality oxide/semiconductor interface [3]. In TLDMOS, a p+ pocket (NA = 1019 cm−3) of 20 nm is introduced with highly doped n+ drain to form a tunneling junction in series with conventional LDMOS as shown in Fig. 102.1b. The n+ and p+ pocket are introduced in the similar way as was done in [6]. In order to prevent the depletion of the entire lightly doped drift region, a n+ pocket (ND = 1019 cm−3) of length 20 nm is introduced with p+ pocket. In both the devices the source contact is shorted with the body contact to prevent turning ON of parasitic BJT formed by n+ source, p body and n− drift region.

3 Simulation Set up

SILVACO’s 2D device simulator (version 5.19.20) is used for the simulation of both the devices. The recombination phenomenon is taken into account by using SRH and AUGER models. The band gap narrowing model (BGN) is considered for highly doped regions. The CONMOB and FLDMOB models are taken into account for the mobility of charge carriers. The impact ionization is taken into account by using Selberherr’s model. The tunneling phenomenon at the drain side is considered by using Klaassen model which is a local tunneling model with the dense mesh spacing ~2 nm. The interface charges are taken to be 5 × 1011 cm−3 [7]. The work function of the gate is chosen to be 5 eV.

4 Results and Discussion

The band diagram of the TLDMOS at drain end for different value of VDS in ON state (VGS = 10 V) along cutline AA′ is shown in Fig. 102.2. We can observe in Fig. 102.2a that at drain voltage of VDS = 0 V, the conduction band and valence band are not aligned. But at a higher drain voltage of VDS = 2 V (as shown in Fig. 102.2b), the conduction band got aligned with the valence band at the drain end. This leads to band to band tunneling at drain which modulates the conductivity of the drift region.

Figure 102.3 shows the electron and hole concentration of LDMOS and TLDMOS at VDS = 2 V and VGS = 10 V. We can observe that in TLDMOS, the electron concentration in drift region increases to ~1017 cm−3 as compared to ~1016 cm−3 in the drift region of LDMOS. Furthermore, the hole concentration in the drift region of TLDMOS increases to ~1017 cm−3 as compared to ~1010 cm−3 in the drift region of LDMOS. The increase in the carrier concentration in the drift region increases its conductivity and reduces the drift resistance.

Figure 102.4a shows the transfer characteristics of LDMOS and TLDMOS at VDS = 2 V. We can observe that due to the tunneling at the drain end, the drain current in TLDMOS increases to ~62 µA/µm as compared with the drain current of ~42 µA/µm in LDMOS at VGS = 10 V.

Figure 102.4b shows the output characteristics of LDMOS and TLDMOS at overdrive voltage of 2 and 6 V. We can observe that there is increase in the drain current of TLDMOS as compared with the LDMOS at both the overdrive voltages. This increase in the drain current of TLDMOS improves its ON state parameters as compared with the LDMOS.

-

ON State Characteristics

The ON state resistance versus gate voltage characteristics of both LDMOS and TLDMOS is shown in Fig. 102.5a at VDS = 2 V. The mean value of ON resistance is measured from VGS = 2–8 V. The mean ON resistance of TLDMOS is 34 × 105 Ω µm as compared to 45 × 105 Ω µm of LDMOS. Thus, the ON resistance of TLDMOS is improved by 24% as compared with LDMOS.

The transconductance versus gate voltage characteristics of both the devices, i.e., TLDMOS and LDMOS is shown in the Fig. 102.5b. The peak transconductance of TLDMOS is 56.67 µS/µm as compared to the transconductance of 48.87 µS/µm of LDMOS. Thus, the transconductance of TLDMOS is improved by 16% as compared with LDMOS.

-

OFF State Characteristics

The OFF state characteristics determines the voltage which causes the breakdown of reverse biased diode formed by p+ body, n− drift and n+ drain regions. It is obtained by sweeping the drain voltage and keeping gate voltage at 0 V. As drain voltage increases, the electric field across lightly doped drift region increases. It causes avalanche multiplication resulting in the increase in current. Due to this, the electric field at the corner of the gate near the drain side increases and causes breakdown of the oxide.

The OFF state characteristics of both the devices are shown in Fig. 102.6. In TLDMOS, the drain current increases at VDS = 20 V due to the onset of band to band tunneling at drain side. Whereas, the sharp increase in current in TLDMOS takes place at VDS = 37 V as compared to the breakdown voltage of LDMOS at VDS = 36 V. Thus, there is no compromise of breakdown voltage in TLDMOS as compared to LDMOS.

5 Conclusion

Using 2D numerical simulations it is shown that by introducing tunneling junction in conventional In0.53Ga0.47As LDMOS, its ON state performance has been improved. The proposed In0.53Ga0.47As TLDMOS shows 24% reduction in ON resistance and 16% improvement in transconductance without compromising with the breakdown voltage.

References

B.J. Baliga, An overview of smart power technology. IEEE Trans. Electron Devices 38(7), 1568–1575 (1991)

T. Erlbacher, Lateral Power Transistors in Integrated Circuits (Springer, 2014)

J.A.D. Alamo, D. Antoniadis, A. Guo, D.-H. Kim, T.-W. Kim, J. Lin, W. Lu, A. Vardi, X. Zhao, InGaAs MOSFETs for CMOS: recent advances in process technology, in IEDM IEEE, pp. 13–24 (2013)

J.B. Steighner, J. Yuan, Y. Liu, Simulation and analysis of InGaAs power MOSFET performances and reliability. IEEE Trans. Electron Devices 58(1), 180–189 (2011)

M.J. Kumar, A. Bansal, Improving the breakdown voltage, ON-resistance, and gate-charge of InGaAs LDMOS power transistors. Semicond. Sci. Technol. 27(10), 105030 (2012)

N. Goyal, R.S. Saxena, A new LDMOS with tunneling junction for improved on-state performance. IEEE Electron Device Letters 34(1), 90–92 (2013)

J.B. Steighner, J. Yuan, Y. Liu, Simulation and analysis of InGaAs power MOSFET performances and reliability. IEEE Trans. Electron Devices 58(1), 180–189 (2011)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Switzerland AG

About this paper

Cite this paper

Saini, N.K., Saxena, R.S. (2019). A New In0.53Ga0.47As LDMOS with Tunneling Junction for Improved on State Performance. In: Sharma, R., Rawal, D. (eds) The Physics of Semiconductor Devices. IWPSD 2017. Springer Proceedings in Physics, vol 215. Springer, Cham. https://doi.org/10.1007/978-3-319-97604-4_102

Download citation

DOI: https://doi.org/10.1007/978-3-319-97604-4_102

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-97603-7

Online ISBN: 978-3-319-97604-4

eBook Packages: Physics and AstronomyPhysics and Astronomy (R0)