Overview

- Introduction of model based hardware testing

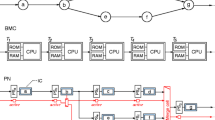

- Describes fault models for nanoscaled CMOS technology

- Fault simulation, ATPG and diagnosis algorithms for complex fault models

- Comprehensive treatment including memory and low power aspects

Part of the book series: Frontiers in Electronic Testing (FRET, volume 43)

Access this book

Tax calculation will be finalised at checkout

Other ways to access

About this book

Model based testing is the most powerful technique for testing hardware and software systems. Models in Hardware Testing describes the use of models at all the levels of hardware testing. The relevant fault models for nanoscaled CMOS technology are introduced, and their implications on fault simulation, automatic test pattern generation, fault diagnosis, memory testing and power aware testing are discussed. Models and the corresponding algorithms are considered with respect to the most recent state of the art, and they are put into a historical context by a concluding chapter on the use of physical fault models in fault tolerance.

Similar content being viewed by others

Keywords

Table of contents (8 chapters)

-

Front Matter

-

Back Matter

Editors and Affiliations

Bibliographic Information

Book Title: Models in Hardware Testing

Book Subtitle: Lecture Notes of the Forum in Honor of Christian Landrault

Editors: Hans-Joachim Wunderlich

Series Title: Frontiers in Electronic Testing

DOI: https://doi.org/10.1007/978-90-481-3282-9

Publisher: Springer Dordrecht

eBook Packages: Engineering, Engineering (R0)

Copyright Information: Springer Science+Business Media B.V. 2010

Hardcover ISBN: 978-90-481-3281-2Published: 07 December 2009

Softcover ISBN: 978-94-007-3093-9Published: 01 March 2012

eBook ISBN: 978-90-481-3282-9Published: 12 November 2009

Series ISSN: 0929-1296

Edition Number: 1

Number of Pages: XIV, 257

Topics: Computer Hardware, Logics and Meanings of Programs, Simulation and Modeling, Circuits and Systems, Performance and Reliability