Abstract

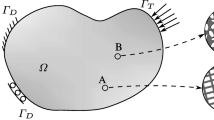

This paper presents an efficient method for globally optimizing and automating component sizing for rotary traveling wave oscillator arrays. The lumped equivalent model of transmission lines loaded by inverter pairs is evaluated and posynomial functions for oscillation frequency, power dissipation, phase noise, etc. are formulated using transmission line theory. The resulting design problem can be posed as a geometric programming problem, which can be efficiently solved with a convex optimization solver. The proposed method can compute the global optima more efficiently than the traditional iterative scheme and various design problems can be solved with the same circuit model. The globally optimal trade-off curves between competing objectives are also computed to carry out robust designs and quickly explore the design space.

Similar content being viewed by others

References

Boyd, S., Kim, S., Vandenberghez, L., Hassibi, A., 2006. A Tutorial on Geometric Programming. Available from http://www.stanford.edu/~boyd/gp_tutorial.html [Accessed on Dec. 9, 2007].

Delorme, N., Belleville, M., Chilo, J., 1996. Inductance and capacitance analytic formulas for VLSI interconnects. Electron. Lett., 32(11):996–997. [doi:10.1049/el:19960689]

Duarte, D.E., Vijaykrishnan, N., Irwin, M.J., 2002. A clock power model to evaluate impact of architectural and technology optimizations. IEEE Trans. VLSI, 10(6):844–855. [doi:10.1109/TVLSI.2002.808433]

GGPLAB, 2006. Software for Generalized Geometric Programming. Available from http://www.stanford.edu/~boyd/ggplab/ [Accessed on Dec. 9, 2007].

Hajimiri, A., Lee, H., 1998. A general theory of phase noise in electrical oscillators. IEEE J. Sol.-State Circ., 33(2):179–194. [doi:10.1109/4.658619]

Hajimiri, A., Limotyrakis, S., Lee, T.H., 1999. Jitter and phase noise in ring oscillators. IEEE J. Sol.-State Circ., 34(6):790–804. [doi:10.1109/4.766813]

Hershenson, M.D.M, 2004. CMOS Analog Circuit Design via Geometric Programming. Proc. American Control Conf., p.3266–3271.

Hershenson, M.D.M, Hajimiri, A., Mohan, S.S., Boyd, S.P., Lee, T.H., 1999. Design and Optimization of LC Oscillators. IEEE/ACM Int. Conf. on Computer-Aided Design, p.65–69. [doi:10.1109/ICCAD.1999.810623]

Hsieh, H.H., Hsu, Y.C., Lu, L.H., 2007. A 15/30-GHz dual-band multiphase voltage-controlled oscillator in 0.18-µm CMOS. IEEE Trans. Microw. Theory Tech., 55(3):474–483. [doi:10.1109/TMTT.2006.890518]

Mercey, G., 2003. A 18GHz Rotary Traveling Wave VCO in CMOS with I/Q Outputs. Proc. 29th European Solid-State Circuits Conf., p.489–492. [doi:10.1109/ESSCIRC.2003.1257179]

Mercey, G., 2004. 18GHz-36GHz Rotary Traveling Wave Voltage Controlled Oscillator in a CMOS Technology. PhD Thesis, Institute of Electrical Engineering and Information Technology, University of Bundeswehr, Germany.

Razavi, B., 2001. Design of Analog CMOS Integrated Circuits. McGraw-Hill Companies, Inc., New York, p.212–216.

Restle, P.J., McNamara, T.G., Webber, D.A., Camporese, P.J., Eng, K.F., Jenkins, K.A., Allen, D.H., Rohn, M.J., Quaranta, M.P., Boerstler, D.W., et al., 2001. A clock distribution network for microprocessors. IEEE J. Sol.-State Circ., 36(5):792–799. [doi:10.1109/4.918917]

Wood, J., Edwards, T.C., Lipa, S., 2001. Rotary traveling-wave oscillator arrays: a new clock technology. IEEE J. Sol.-State Circ., 36(11):1654–1665. [doi:10.1109/4.962285]

Yu, Z.T., Liu, X., 2005. Power Analysis of Rotary Clock. Proc. IEEE Computer Society Annual Symp. on VLSI, p.150–155. [doi:10.1109/ISVLSI.2005.58]

Yu, Z.T., Liu, X., 2007. Low-power rotary clock array design. IEEE Trans. VLSI, 15(1):5–12. [doi:10.1109/TVLSI.2006.887804]

Zhuo, C., Zhang, H.F., Samanta, R., Hu, J., Chen, K.S., 2007. Modeling, Optimization and Control of Rotary Traveling-wave Oscillator. IEEE/ACM Int. Conf. on Computeraided Design, p.476–480. [doi:10.1109/ICCAD.2007.4397310]

Author information

Authors and Affiliations

Corresponding author

Additional information

Project (No. 20060335065) supported by the Specialized Research Fund for the Doctoral Program of Higher Education of Ministry of Education, China

Rights and permissions

About this article

Cite this article

Chen, Lj., Zhang, Hf., Zhou, Jf. et al. Efficient design of rotary traveling wave oscillator array via geometric programming. J. Zhejiang Univ. Sci. A 10, 1815–1823 (2009). https://doi.org/10.1631/jzus.A0820774

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1631/jzus.A0820774

Key words

- Rotary traveling wave oscillator array (RTWOA)

- Clock distribution

- Transmission line resonator

- Global optimization

- Geometric programming (GP)