Abstract

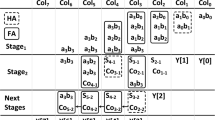

In this paper, we propose an effective VLSI architecture of sub-pixel interpolation for motion compensation in the AVS HDTV decoder. To utilize the similar arithmetical operations of 15 luma sub-pixel positions, three types of interpolation filters are proposed. A simplified multiplier is presented due to the limited range of input in the chroma interpolation process. To improve the processing throughput, a parallel and pipelined computing architecture is adopted. The simulation results show that the proposed hardware implementation can satisfy the real-time constraint for the AVS HDTV (1 920×1 088) 30 fps decoder by operating at 108 MHz with 38.18k logic gates. Meanwhile, it costs only 216 cycles to accomplish one macroblock, which means the B frame sub-pixel interpolation can be realized by using only one set of the proposed architecture under real-time constraints.

Similar content being viewed by others

References

AVS (Audio Video Coding Standard Workgroup of China), 2003. Video Coding Standard FCD1.0.

Chen, T.C., Huang, Y.W., Chen, L.G., 2004. Fully Utilized and Reusable Architecture for Fractional Motion Estimation of H.264/AVC. Proc. IEEE ICASSP, 5:9–12.

Deng, L., Gao, W., Hu, M.Z., Ji, Z.Z., 2004. An Efficient VLSI Implementation for MC Interpolation of AVS Standard. Advances in Multimedia Information Processing, p.200–206.

Horowitz, M., Joch, A., Kossentini, F., Hallapuro, A., 2003. H.264/AVC baseline profile decoder complexity analysis. IEEE Trans. on Circuits Syst. Video Technol., 13(7):704–716. [doi:10.1109/TCSVT.2003.814967]

Li, Y., Qu, Y.M., He, Y., 2007. Memory Cache Based Motion Compensation Architecture for HDTV H.264/AVC Decoder. IEEE Int. Symp. on Circuits and Systems, p.2906–2909. [doi:10.1109/ISCAS.2007.377857]

Ling, N., Wang, N.T., 2003. A real-time video decoder for digital HDTV. J. VLSI Signal Processing, 33(3):295–306. [doi:10.1023/A:1022179914445]

Mizosoe, H., Yoshida, D., Nakamura, T., 2007. A single chip H.264/AVC HDTV encoder/decoder/transcoder system LSI. IEEE Trans. on Consum. Electron., 53(2):630–635. [doi:10.1109/TCE.2007.381739]

Song, Y., Liu, Z.Y., Goto, S., Ikenaga, T., 2005. A VLSI Architecture for Motion Compensation Interpolation in H.264/AVC. 6th Int. Conf. on ASIC, 1:279–282.

Tsai, C.Y., Chen, T.C., Chen, T.W., Chen, L.G., 2005. Bandwidth Optimized Motion Compensation Hardware Design for H.264/AVC HDTV Decoder. 48th Midwest Symp. on Circuits and Systems, 2:1199–1202. [doi:10.1109/ MWSCAS.2005.1594322]

Wang, R.G., Huang, C., Li, J.T., Shen, Y.F., 2004. Sub-pixel Motion Compensation Interpolation Filter in AVS. IEEE Int. Conf. on Multimedia and Expo, 1:93–96.

Wang, S.Z., Lin, T.A., Liu, T.M., Lee, C.Y., 2005. A New Motion Compensation Design for H.264/AVC Decoder. Proc. IEEE Int. Symp. on Circuits and Systems, 5:4558–4561. [doi:10.1109/ISCAS.2005.1465646]

Zheng, J.H., Deng, L., Zhang, P., Xie, D., 2006. An efficient VLSI architecture for motion compensation of AVS HDTV decoder. J. Comput. Sci. Technol., 21(3):370–377. [doi:10.1007/s11390-006-0370-8]

Author information

Authors and Affiliations

Corresponding author

Additional information

Project (No. 20051321B01) supported by the Science and Technology Development Project of Hangzhou, China

Rights and permissions

About this article

Cite this article

Li, Wy., Yu, L. Highly parallel implementation of sub-pixel interpolation for AVS HDTV decoder. J. Zhejiang Univ. Sci. A 9, 1638–1643 (2008). https://doi.org/10.1631/jzus.A0820112

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1631/jzus.A0820112