Abstract

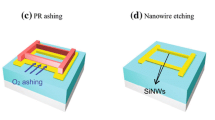

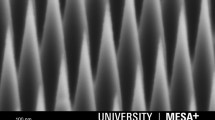

Arrays of vertically aligned silicon wires of 250 nm–4 μm in diameter were fabricated in a top–down process using photolithography and deep reactive ion etching at cryogenic temperatures. Using the 3-omega method, thermal conductance of vertical silicon nanowires, i.e., nanopillars, was measured immediately on-chip without the need of breaking off single wires and mounting them into a special testing device. The Seebeck coefficient was measured with 2-mm2 arrays of pillars of 260 nm in diameter, which were pressure-joined with bulk chips for testing. Testing was performed in the temperature range between 50 and 470 °C at applied temperature gradients of up to 190 °C. We found a reduction of the thermal conductivity to less than 30% of the bulk silicon, confirming that arrayed vertical nanowires fabricated in an economical top–down process can strongly promote silicon as a thermoelectric material.

Similar content being viewed by others

REFERENCES

P. Yang, R. Yan, and M. Fardy: Semiconductor nanowire: What’s next? Nano Lett. 10, 1529 (2010).

A.I. Boukai, Y. Bunimovich, J. Tahir-Kheli, J.-K. Yu, W.A. Goddard III, and J.R. Heath: Silicon nanowires as efficient thermoelectric materials. Nature 451, 168(2008).

A.I. Hochbaum, R. Chen, R.D. Delgado, W. Liang, E.C. Garnett, M. Najarian, A. Majumdar, and P. Yang: Enhanced thermoelectric performance of rough silicon nanowires. Nature 451, 163(2008).

P. Martin, Z. Aksamija, E. Pop, and U. Ravaioli: Impact of phonon-surface roughness scattering on thermal conductivity of thin Si nanowires. Phys. Rev. Lett. 102, 125503 (2009).

C.T. Hsu, D.J. Yao, K.J. Ye, and B. Yu: Renewable energy of waste heat recovery system for automobiles. J. Renewable Sustainable Energy 2, 013105 (2010).

N. Espinosa, M. Lazard, L. Aixala, and H. Scherrer: Modeling a thermoelectric generator applied to diesel automotive heat recovery. J. Electron. Mater. 39, 1446 (2010).

S.Y. Park, S.J. Di Giacomo, R. Anisha, P.R. Berger, P.E. Thompson, and I. Adesida: Fabrication of nanowires with high aspect ratios utilized by dry etching with SF6:C4F8 and self-limiting thermal oxidation on Si substrate. J. Vac. Sci. Technol. B 28, 763(2010).

D. Paul: Generate Renewable Energy Efficiently using Nanofabricated Silicon (GREEN Silicon). European project EC FP7 ICT FET, http://www.greensilicon.eu/GREENSilicon/index.html.

Ü. Sökmen, A. Stranz, S. Fündling, S. Merzsch, R. Neumann, H.-H. Wehmann, E. Peiner, and A. Waag: Shallow and deep dry etching of silicon using ICP cryogenic reactive ion etching process. Microsyst. Technol. 16, 863 (2010).

A. Stranz, Ü. Sökmen, E. Peiner, and A. Waag: Sapphire on silicon assembly using a nanostructured compliant interface. (Techn. Dig. 22nd Intern. Conf. Eurosensors XXII, Dresden, Germany, September 7–10, 2008), p. 1246.

L. Shi, D. Li, C. Yu, W. Jang, D. Kim, Z. Yao, P. Kim, and A. Majumdar: Measuring thermal and thermoelectric properties of one-dimensional nanostructures using a microfabricated device. J. Heat Transfer 125, 881 (2003).

O. Bourgeois, T. Fournier, and J. Chaussy: Measurement of the thermal conductance of silicon nanowires at low temperature. J. Appl. Phys. 101, 016104 (2007).

X.J. Hu, A. Antonio Padillay, J Xuz, T.S Fisher, K.E. Goodson: 3-omega measurements of vertically oriented carbon nanotubes on silicon. J. Heat Transfer 128, 1109 (2006).

E. Puyoo, S. Grauby, J.-M. Rampnoux, E. Rouvière, and S. Dilhaire: Thermal exchange radius measurement: Application to nanowire thermal imaging. Rev. Sci. Instrum. 81, 073701 (2010).

S. Lefèvre, S. Volz, and P.-O. Chapuis: Nanoscale heat transfer at contact betweena hot tip and a substrate. Int. J. Heat Mass Transfer 49, 251 (2006).

G.D. Cahill: Thermal conductivity measurement from 30 to 750 K: The 3ω method. Rev. Sci. Instrum. 61, 802 (1990); Erratum. Rev. Sci. Instrum. 73, 3701 (2002).

Y. Sungtaek Ju: Phonon heat transport in silicon nanostructures. Appl. Phys. Lett. 87, 153106 (2005).

T.H. Geballe and T.W. Hull: Seebeck effect in silicon. Phys. Rev. 98, 940 (1955).

N. Neophytou, M. Wagner, H. Kosina, and S. Selberherr: Analysis of thermoelectric properties of scaled silicon nanowires using an atomistic tight-binding model. J. Electron. Mater. 39, 1902 (2010).

G.D. Cahill, W.K. Ford, K.E. Goodson, G.D. Mahan, A. Majumdar, H.J. Maris, R. Merlin, and S.R. Phillpot: Nanoscale thermal transport. J. Appl. Phys. 93, 793 (2003).

W.M. Pruessner, W.S. Rabinovich, T.H. Stievater, D. Park, and J.W. Baldwin: Cryogenic etch process development for profile control of high aspect-ratio submicron silicon trenches. J. Vac. Sci. Technol. B 25, 21 (2007).

ACKNOWLEDGMENTS

We thank M. Turczyński for his valuable technical assistance during the 3-omega measurements with silicon pillars. This work is supported by the German Research Foundation (DFG) under PE 885/2-1 “Silicon-based thermoelectric nanosystems” in the framework of the priority program, SPP 1386.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Stranz, A., Waag, A. & Peiner, E. Thermal characterization of vertical silicon nanowires. Journal of Materials Research 26, 1958–1962 (2011). https://doi.org/10.1557/jmr.2011.60

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1557/jmr.2011.60