Abstract

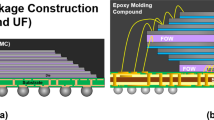

This work attempts to determine an appropriate passivation structure in the real integrated circuit (IC) pattern to improve stress-related reliability problems after the plastic packaging. Several different types of amorphous passivation materials were first tested to learn how effectively they protect underlying Al interconnection lines during thermal displacement-induced fatigue at temperature ranges from −65 °C to 150 °C. It was also studied how effectively the occurrence of cracking in a passivation layer can be suppressed by the improvement of its topological feature or increase in its thickness. According to the experimental results, an increase in passivation thickness up to 21,000 Å (7000 Å for oxide and 14,000 Å for SiN, respectively) was found to be a highly effective way to suppress stress-induced passivation damage on the inside of the chip in plastic IC packages. However, at the edges of the chip, smoothing of the passivation layer by a sloping metal sidewall was more important for the improvement of thermal cycling performance than thickening of the passivation layer.

Similar content being viewed by others

References

W.A. P. Claassen, H. A. J. Th. v. d. Pol, and A. H. Goemans, J. Electrochem. Soc.: Solid-State Sci. Technol. 133, 1458 (1986).

P. A. Flinn, in Thin Films: Stresses and Mechanical Properties II, edited by M. F. Doerner, W. C. Oliver, G. M. Pharr, and F. R. Brotzen (Mater. Res. Soc. Symp. Proc. 188, Pittsburgh, PA, 1990), p. 3.

A. I. Sauter and W. D. Nix, in Thin Films: Stresses and Mechanical Properties II, edited by M.F. Doerner, W.C. Oliver, G. M. Pharr, and F. R. Brotzen (Mater. Res. Soc. Symp. Proc. 188, Pittsburgh, PA, 1990), p. 15.

S. Okikawa et al., The International Society for Testing and Failure Analysis Meeting, Los Angeles, CA, Oct. (1983).

A. Nishimura, S. Kawai, and G. Murakami, IEEE Trans. on CHMT 12, 639 (1989).

E. Suhir, Proc. 37th Electronics Components Conference, IEEE/(EIA) (1987), p. 508

S. W. Groothius and M. Murtuza, Proc. 23rd Annual Int. Reliability Symposium, IEEE (1985), p. 184.

D. Edwards, K. G. Heinen, S. K. Martines, and J. E. Martines, IEEE Trans. Components, Hybrids, and Manufacturing Technology, CHMT-12 (4) (1987).

J. Klema, R. Pyle, and E. Domangue, 22nd Annual Proceedings of Reliability Physics, IEEE Cat. 84 (CH1990-1), 1 (1984).

T. Abraham, Proceedings 4th Intl. IEEE VMIC Conf., Santa Clara, CA (1987), p. 115.

S. M. Lee, J.H. Lee, S. Y. Oh, and H. K. Chung, Proceedings 45th IEEE/ECTC, Las Vegas, NV (1995), p. 455.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Lee, SM. Appropriate passivation structure in dynamic random access memory devices to improve stress-related reliability performance after plastic packaging. Journal of Materials Research 13, 1967–1973 (1998). https://doi.org/10.1557/JMR.1998.0276

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1557/JMR.1998.0276