Abstract

Redox-based resistive switches are an emerging class of non-volatile memory and logic devices. Especially, ultimately scaled transistor-less passive crossbar arrays using a selector/resistive-switch (1S1R) configuration are one of the most promising architectures. Due to the scalability and the inherent logic and memory capabilities of these devices, they are good candidates for logic-in-memory approaches. But due to the memory architecture, true parallelism can only be achieved by either working on several arrays at the same time or at multiple lines in an array at the same time. In this work, a Sklansky tree adder is presented, which exploits the parallelism of a single crossbar array. The functionality is proven by means of memristive simulations using a physics-based TaOx model. The circuit and device requirements for this approach are discussed.

Similar content being viewed by others

References

M.A. Zidan, J.P. Strachan, W.D. Lu, Nat. Electron. 1, 22 (2018)

J.J. Yang, D.B. Strukov, D.R. Stewart, Nat. Nanotechnol. 8, 13 (2013)

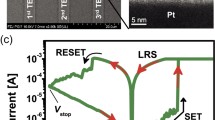

W. Kim, S. Menzel, D.J. Wouters, R. Waser, V. Rana, IEEE Electron Device Lett. 37, 564 (2016)

S. Poblador, M. Gonzalez, F. Campabadal, Microelectron. Eng. 187, 148 (2018)

A. Prakash, J. Park, J. Song, J. Woo, E. Cha, H. Hwang, IEEE Electron Device Lett. 36, 32 (2015)

A. Flocke, T.G. Noll, in Proceedings of the 33rd European Solid-State Circuits Conference (2007), p. 328

E. Linn, R. Rosezin, C. Kügeler, R. Waser, Nat. Mater. 9, 403 (2010)

G. Burr, R. Shenoy, K. Virwani, P. Narayanan, A. Padilla, B. Kurdi, H. Hwang, J. Vac. Sci. Technol. B 32, 040802 (2014)

E. Linn, R. Rosezin, S. Tappertzhofen, U. Böttger, R. Waser, Nanotechnology 23, 305205 (2012)

J. Borghetti, G.S. Snider, P.J. Kuekes, J.J. Yang, D.R. Stewart, R.S. Williams, Nature 464, 873 (2010)

S. Kvatinsky, D. Belousov, S. Liman, G. Satat, N. Wald, E.G. Friedman, A. Kolodny, U.C. Weiser, IEEE Trans. Circuits Syst. Express Briefs 61, 895 (2014)

T. You, Y. Shuai, W. Luo, N. Du, D. Bürger, I. Skorupa, R. Hübner, S. Henker, C. Mayr, R. Schüffny, T. Mikolajick, O.G. Schmidt, H. Schmidt, Adv. Funct. Mater. 24, 3357 (2014)

A. Siemon, T. Breuer, N. Aslam, S. Ferch, W. Kim, J. van den Hurk, V. Rana, S. Hoffmann-Eifert, R. Waser, S. Menzel, E. Linn, Adv. Funct. Mater. 25, 6414 (2015)

E. Lehtonen, M. Laiho, in 2009 IEEE/ACM International Symposium on Nanoscale Architectures, San Francisco, CA, USA, July 30–31 2009 (2009), p. 33

S. Kvatinsky, E.G. Friedman, A. Kolodny, U.C. Weiser, IEEE Trans. Very Large Scale Integr. VLSI Syst. 22, 2054 (2014)

A. Siemon, S. Menzel, R. Waser, E. Linn, IEEE J. Emerging. Sel. Top. Circuits Syst. 5, 64 (2015)

N. Talati, S. Gupta, P. Mane, S. Kvatinsky, IEEE Trans. Nanotechnol. 15, 635 (2016)

M. Teimoory, A. Amirsoleimani, J. Shamsi, A. Ahmadi, S. Alirezaee, M. Ahmadi, in 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), Marseille, France, December 7–10 2014 (2014)

M. Le Gallo, A. Sebastian, R. Mathis, M. Manica, H. Giefers, T. Tuma, C. Bekas, A. Curioni, E. Eleftheriou, Nat. Electron. 1, 246 (2018)

T. Breuer, A. Siemon, E. Linn, S. Menzel, R. Waser, V. Rana, Adv. Electron. Mater. 1, 1500138 (2015)

J. Sklansky, IRE Trans. Electron. Comput. (USA) EC-9, 226 (1960)

D. Harris, in Conference Record of the Thirty-Seventh Asilomar Conference On Signals, Systems & Computers (2003), Vols. 1 and 2, p. 2213

A. Siemon, S. Menzel, A. Marchewka, Y. Nishi, R. Waser, E. Linn, in 2014 IEEE International Symposium on Circuits and Systems (ISCAS) (2014), p. 1420

A. Siemon, S. Menzel, A. Chattopadhyay, R. Waser, E. Linn, in 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015 (2015), p. 13

E. Linn, A. Siemon, R. Waser, S. Menzel, IEEE Trans. Circuits Syst. Regul. Pap. (TCAS-I) 61, 2402 (2014)

S. Menzel, A. Siemon, A. Ascoli, R. Tetzlaff, in Proceedings of 2018 IEEE International Symposium on Circuits and Systems (ISCAS), 27–30 May 2018, Florence, Italy (2018)

S. Kim, W. Lee, H. Hwang, in 2012 13th International Workshop On Cellular Nanoscale Networks and Their Applications (CNNA) (IEEE, 2012), pp. 1–2

D. Bhattacharjee, A. Siemon, E. Linn, S. Menzel, A. Chattopadhyay, ACM JETC 14, 30 (2018)

E. Lehtonen, J.H. Poikonen, M. Laiho, Electron. Lett. 46, 239 (2010)

K. Kim, S. Shin, S.M. Kang, IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 30, 1800 (2011)

J. Reuben, R. Ben-Hur, N. Wald, N. Talati, A.H. Ali, P.-E. Gaillardon, S. Kvatinsky, in 2017 27th International Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS), Thessaloniki, Greece, 25–27 September 2017 (2017)

P.-E. Gaillardon, L. Amaru, A. Siemon, E. Linn, R. Waser, A. Chattopadhyay, G. De Micheli, in 2016 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 14–18 March 2016 (2016), p. 1

X. Hu, M.J. Schultis, M. Kramer, A. Bagla, A. Shetty, J.S. Friedman, IEEE Trans. Circuits Syst. Regul. Pap. (TCAS-I) 66, 263 (2018)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Siemon, A., Menzel, S., Bhattacharjee, D. et al. Sklansky tree adder realization in 1S1R resistive switching memory architecture. Eur. Phys. J. Spec. Top. 228, 2269–2285 (2019). https://doi.org/10.1140/epjst/e2019-900042-x

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1140/epjst/e2019-900042-x