Abstract

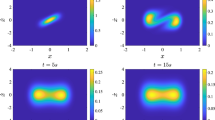

A novel approach to determining time parameters of digital library IC elements with the use of built-in digital measuring modules arranged on the test chip is offered. It is shown that using the phase error accumulation methodology in ring oscillators with the investigated elements makes it possible to measure the averaged rising and falling delays of signals with picosecond accuracy. Use of digital elements will allow us to provide a technology-independent solution when one manufacturing method used at a plant changes to another one without modifying the circuits of the measurement module and the measuring technique.

Similar content being viewed by others

References

Ruffoni, M. and Bogliolo, A., Direct measures of path delays on commercial FPGA chips (Proc. of 6th IEEE Workshop on Signal Propagation on Interconnects), Pisa, 2002, pp. 157–159.

Maggioni, S., Veggetti, A., Bogliolo, A., and Croce, L., Random sampling for on-chip characterization of standard cell propagation delay (Proc. of the Fourth International Symposium on Quality Electronic Design), 2003, pp. 41–45.

Churayev, S.O. and Paltashev, T.T., Speed improvement in random sampling for on-chip cell characterization, Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS-2011), IEEE Catalog Number: CFP11DDE-CDR, Cottbus, Germany, 2011, pp. 305–308.

Matkarimov, B.T., Paltashev, T.T., and Churayev S.O., In-circuit measurements of time delays of standard library cells, Papers of National Academy of Sciences of the Republic of Kazakhstan, 2010, no 2. pp. 7–10.

Churayev S.O., Matkarimov V.T., and Paltashev T.T., On-chip measurements of standard-cell propagation delay, IEEE East-West Design & Test Symposium (EWDTS’09), Moscow, 2009, pp. 93–95.

Chang, S.K., In, H.I., Churayev, S., and Paltashev, T., Phase error accumulation methodology for on-chip cell characterization, World Academy of Science, Engineering and Technology, An International Journal of Science, Engineering and Technology, no. 28. pp. 132–136.

Author information

Authors and Affiliations

Corresponding author

Additional information

Original Russian Text © S.O. Churayev, 2013, published in Izvestiya Vysshikh Uchebnykh Zavedenii. Elektronika, 2013, No. 1, pp. 34–40.

Rights and permissions

About this article

Cite this article

Churayev, S.O. Use of the effect of phase error accumulation in ring oscillators to estimate time parameters of digital elements of integrated circuits. Russ Microelectron 42, 403–407 (2013). https://doi.org/10.1134/S1063739713070044

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S1063739713070044