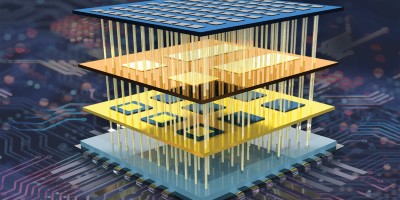

Wafer-to-wafer hybrid bonding is an attractive 3D integration technology for stacking multiple heterogeneous chips with high 3D interconnect density. We highlight recent design and technology innovations that enable hybrid Cu, SiCN-to-Cu and SiCN bonding with interconnect pitches down to an unprecedented 400 nm.

References

Wuu, J. et al. In 2022 IEEE International Solid-State Circuits Conference (ISSCC) 428–429 (IEEE, 2022).

Chew, S. A. et al. In 2023 IEEE International Electron Devices Meeting (IEDM) 13.6 (IEEE, 2023).

Acknowledgements

The authors thank the 3D system integration department at imec for their contributions and M. Van Bavel for editing this article.

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Rights and permissions

About this article

Cite this article

Chew, S.A., De Vos, J. & Beyne, E. Wafer-to-wafer hybrid bonding at 400-nm interconnect pitch. Nat Rev Electr Eng 1, 71–72 (2024). https://doi.org/10.1038/s44287-024-00019-8

Published:

Issue Date:

DOI: https://doi.org/10.1038/s44287-024-00019-8

- Springer Nature Limited