Abstract

Oxide semiconductors have gained significant attention in electronic device industry due to their high potential for emerging thin-film transistor (TFT) applications. However, electrical contact properties such as specific contact resistivity (ρC) and width-normalized contact resistance (RCW) are significantly inferior in oxide TFTs compared to conventional silicon metal oxide semiconductor field-effect transistors. In this study, a multi-stack interlayer (IL) consisting of titanium nitride (TiN) and indium-gallium-tin-oxide (IGTO) is inserted between source/drain electrodes and amorphous indium-gallium-zinc-oxide (IGZO). The TiN is introduced to increase conductivity of the underlying layer, while IGTO acts as an n+-layer. Our findings reveal IGTO thickness (tIGTO)-dependent electrical contact properties of IGZO TFT, where ρC and RCW decrease as tIGTO increases to 8 nm. However, at tIGTO > 8 nm, they increase mainly due to IGTO crystallization-induced contact interface aggravation. Consequently, the IGZO TFTs with a TiN/IGTO (3/8 nm) IL reveal the lowest ρC and RCW of 9.0 × 10−6 Ω·cm2 and 0.7 Ω·cm, significantly lower than 8.0 × 10−4 Ω·cm2 and 6.9 Ω·cm in the TFTs without the IL, respectively. This improved electrical contact properties increases field-effect mobility from 39.9 to 45.0 cm2/Vs. This study demonstrates the effectiveness of this multi-stack IL approach in oxide TFTs.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Introduction

In 2004, amorphous indium-gallium-zinc-oxide (a-IGZO) was discovered by the group of Prof. Hosono, offering numerous outstanding characteristics such as reasonable field-effect mobility (μFE) > 10 cm2/Vs, extremely low off-current < 10−24 A/μm, steep subthreshold swing (SS) of ~ 0.1 V/dec, and outstanding uniformity even when fabricated at low temperature1,2,3,4,5. Because of these merits, oxide semiconductor (OS) family has been studied intensively and has become a standard channel material of thin-film transistors (TFTs) in high-end active matrix organic light emitting diode (AMOLED) display backplanes. Recently, the OS has gained more attention as a channel candidate for next-generation semiconductor device applications such as 2T0C dynamic random access memory (DRAM)6,7,8,9, because it has potential to overcome the scaling and leakage problems of DRAM technologies due to their ultralow off-current originating from the wide bandgap (EG) nature. Furthermore, their back-end-of-line (BEOL)-compatible low-temperature processibility enables movement of the DRAM peripheral circuitry under the memory array, achieving 3D DRAM technology.

Solid state devices have been scaled down to improve power, performance, area, and cost (PPAC) in the semiconductor industry2. O/S TFTs also must follow this conventional PPAC rule to meet the abovementioned requirements. For this reason, increasing numbers of studies on scaled oxide TFTs have been reported2. Here, it is important to note that the impact of contact resistance in nanoscale semiconductor devices increases considerably with miniaturization. However, the contact resistance of OS TFTs is generally four orders of magnitude higher than that of the current silicon (Si) metal oxide semiconductor field-effect transistors (MOSFETs)10,11,12. This high contact resistance of OS TFTs can be a critical obstacle for miniaturized device applications13. Thus, there is need to improve the electrical contact properties between OS channels and source/drain (S/D) electrodes.

To improve the contact resistance at the channel/electrode interface, both Schottky barrier height and width must be reduced to facilitate carrier injection through the barrier formed at the interface14,15,16. The height is controlled depending on a work function of contact electrode, which can reduce the contact resistance17. The interface-state defects at the channel/electrode interface should be minimized to increase the height control18. The width determined by carrier density (nc) of the channel material can be narrowed by several approaches19,20,21,22,23,24,25,26,27,28,29,30,31,32,33. Increasing nc is the simplest method to reduce barrier width, which was originally devised for the Si MOSFETs, and can be realized through ion implantation and/or plasma treatments using elements such as boron, fluorine, argon, or hydrogen19,20,21,29,30. However, these methods can damage the channel layer below the S/D electrodes, which increases the interface defects and offsets the merits of increasing nc. In addition to these doping techniques, other approaches such as controlling cation composition, metal-induced oxygen scavenging and highly conductive interlayer (IL) insertion have been employed22,23,24,25,26,27,34,35. These methods have an advantage in that they can reduce the barrier width without incurring damage.

In this study, a multi-stack IL using titanium nitride (TiN) and indium-gallium-tin-oxide (IGTO) is inserted between IGZO channel and indium tin oxide (ITO) S/D electrodes. Specific contact resistivity (ρC) of IGZO TFTs with a 3-nm-thick TiN IL is reduced to 5.6 × 10−5 Ω·cm2, which is almost 20-fold lower than that of IGZO TFTs without the IL. More importantly, the electrical contact properties have IGTO thickness (tIGTO)-dependent behavior, decreasing with tIGTO up to 8 nm. It is degraded in the IGZO TFTs with tIGTO greater than 8 nm. Consequently, the device with a TiN/IGTO (3/8 nm) IL has the lowest ρC and width-normalized contact resistance (RCW) of 9.0 × 10−6 Ω·cm2 and 0.7 Ω·cm, which also leads to the largest increase in μFE from 39.9 to 45.0 cm2/Vs compared to the device without the IL. This noticeable improvement in the electrical contact properties could be attributed to enhanced electron injection by reduced Schottky barrier height (SBH) and width through the TiN/IGTO IL insertion, which will be discussed in depth.

Methods

Device fabrication

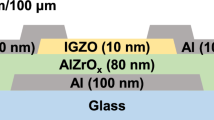

Transmission line method (TLM) patterns and bottom gate IGZO TFTs were fabricated with top-contact configuration (Fig. 1a,b). 15-nm-thick IGZO thin-films were deposited through plasma-enhanced atomic layer deposition (PEALD) using dimethylbutylamino(trimethylindium) (DATI), trimethylgallium (TMG), diethylzinc (DEZ), and O2 plasma as In, Ga, Zn and oxygen sources, respectively, at 150 °C. Also, 100-nm-thick silicon oxide (SiO2) and heavily doped p+-Si substrates were used as gate dielectric and electrode, respectively. The deposited channel layers were patterned by standard photolithography and wet etching. The TiN and IGTO IL were deposited through direct current (DC) magnetron sputtering at room temperature, followed by in-situ deposition of highly conducting indium tin oxide (ITO) thin-films for S/D electrodes. Then, the deposited S/D structure with the multi-stack IL was patterned using the lift-off method. Finally, the devices were annealed at 500 °C under ambient air for 1 h. The fabricated TLM pattern devices have a channel width (W) of 60 μm and lengths (L) of 20, 30, 40, and 50 μm. The TFTs has W/L of 60/30 μm.

Materials and device characterization

The film thickness was determined through spectroscopic ellipsometry (Elli-SE, Ellipso Technology), and nc was obtained through Hall effect measurements (HMS-5000, Ecopia) with a van der Pauw configuration. Surface morphologies of IGTO/IGZO thin-film stacks were characterized using atomic force microscopy (XE-100, Park System Co.). The crystalline structure of the IGTO thin-film was confirmed through grazing incidence X-ray diffraction (Model X’Pert PRO MRD, Malvern Panalytical) and high-resolution transmission electron microscopy (NEOARM, JEOL). Chemical states were determined through X-ray photoelectron spectroscopy (K-Alpha+, Thermo Fisher Scientific Co.) after in-situ surface (~ 3 nm) etching using an accelerated (1 kV) Ar+ ion to avoid confusion by possible contamination and/or oxidation during air exposure.

Electrical characteristics of the fabricated TFTs were measured through a Keithley 2636 source meter at room temperature under dark conditions. The μFE was calculated using the equation \( {\mu_{FE}} = \frac{{L{g_m}}}{{W{C_{OX}}{V_{DS}}}}\)31, where COX, VDS, and gm are the capacitance per unit area, drain-to-source voltage, and transconductance, respectively. In this study, VDS is 0.1 V. Threshold voltage (VTH) was extracted using the constant current method, which was defined as the gate-to-source voltage (VGS) inducing a drain current (ID) of L/W × 10 nA31. Subthreshold swing (SS) was obtained using the equation \( SS = \frac{{d{V_{GS}}}}{{d\log {I_D}}}\) at the subthreshold region of transfer characteristics31.

Results and discussion

To verify the effects of TiN and IGTO IL on electrical contact properties in the IGZO TFT, TLM was conducted. Figure 2 shows total resistance (RT) versus L graphs as a function of gate voltage (VGS) in the IGZO TLM devices with different multi-stack ILs. ρC was calculated using the following equations:14

where Rch, RC, and ∆L are the channel resistance, the contact resistance, and the change in channel length, respectively. The values of 2RC and 2∆L can be obtained at the intersection of the RT and L curves (Fig. 2)31. More importantly, the RCW can be expressed as36

where RSH, LC, and LT are the sheet resistance of the channel, the physical contact length (30 μm in this study), and the current transfer length, respectively. This equation can be rewritten as

As such, ρC can be obtained using Eq. (3). It is also important to note that the RCW, an intuitive figure of merit to demonstrate the electrical contact properties, is simultaneously observed along with the ρC throughout this study. The control device without the IL has the largest ρC (RCW) of 8.0 × 10−4 Ω·cm2 (6.9 Ω·cm). Insertion of a 3-nm-thick TiN IL reduces this to 5.6 × 10−5 Ω·cm2 (1.8 Ω·cm), respectively, which indicates that the TiN IL improves the electrical contact properties. This improvement could be attributed to increase in conductivity of the underlying layer through the oxygen scavenging effect of the TiN. Combination of IGTO thin-film with the TiN IL further improves the electrical contact. Of particular interest is tIGTO-dependent behavior, where ρC (RCW) values of 1.4 × 10−5 (0.9), 9.0 × 10−6 (0.7), and 3.0 × 10−5 Ω·cm2 (1.3 Ω·cm) were obtained in the devices using a TiN/IGTO multi-stack IL with tIGTO of 5, 8, and 12 nm, respectively. The device with the TiN/IGTO IL (3/8 nm) has the lowest ρC of 9.0 × 10−6 Ω·cm2, which is almost two orders of magnitude lower than that of the control device (Fig. S1). The RCW also has the same tIGTO dependence which has the smallest value of 0.7 Ω·cm. It is noteworthy that the both of the ρC and RCW are reduced to 1.1 × 10−5 Ω·cm2 and 1.0 Ω·cm in the device featuring an 8-nm-thick IGTO IL (Fig. S2). This outcome suggest that the IGTO IL alone can enhance the electrical contact properties to a certain degree, even without the presence of TiN. However, it simultaneously indicates that the TiN/IGTO multi-stack IL holds greater influence. Additionally, it is worth noting that the device annealed at 400 °C with the TiN/IGTO IL (3/8 nm) demonstrates electrical contact properties comparable to those of the device with the same IL stack annealed at 500 °C (Fig. S3). These findings collectively imply that insertion of a multi-stack IL is not only an effective but also thermally stable method for enhancing the electrical contact properties of IGZO TFT.

Before comprehending the effect of tIGTO on the electrical contact properties, it is quite important to discuss the implications of the intersection in RT versus L graphs. In oxide TFTs, the ∆L generally originates from oxygen vacancy (VO)’s diffusion, which occurs more noticeably in the OS containing high VO concentration. Here, IGZO TFTs with an IL can have higher VO concentration at the contact region than those without an IL due to a synergetic effect of TiN and IGTO layers where the former induces oxygen scavenging effect from the underlying oxide layer and the latter has high VO concentration. It leads to the higher nc, which reduces the Schottky barrier width and improves the electron injection from the source electrode. More importantly, this reduced barrier width makes the electron injection independent on VGS. For this reason, the IGZO TFTs with an IL can have a VGS-independent intersection, i.e., VGS-independent RC, in the RT versus L graphs. Meanwhile, there could not be an intersection, as shown in the RT versus L graph of IGZO TFTs without an IL. In this case, the RC as well as LT becomes dependent on the VGS. It could be because the nc under the S/D electrode is affected by the VGS due to the relatively low VO concentration at the contact region.

To understand the effect of multi-stack IL, the ultraviolet photoelectron spectroscopy (UPS) depth profile and UV/visible spectroscopy was conducted for two cases: (1) the ITO/IGZO thin-film stack; (2) ITO/TiN/IGTO/IGZO (3-/8-nm-thick TiN/IGTO IL) thin-film stack. Work functions and differences between the Fermi-level and the valence band edge (EF–EV) were obtained by the UPS (Fig. S4). EG was extracted through the UV/visible spectroscopy. It was confirmed that both of the IGTO and IGZO possess approximately 3.6 eV of EG. Utilizing the values obtained from these analyses, the energy band diagrams were estimated (Fig. 3). The detailed procedure to depict the band diagrams can be seen in the previous study37. Consequently, the SBH decreases from approximately 0.4 to 0.2 eV by inserting the 3-/8-nm-thick TiN/IGTO IL. These values may deviate slightly. However, it is obvious that the SBH for electron injection is drastically reduced by this contact scheme. This reduction can lead to the improvement in specific contact resistivity by enhancing the electron injection as confirmed in the TLM analyses.

Then, atomic force microscopy (AFM) analysis was conducted. Figure 4 shows tIGTO-dependent surface roughness (Rrms) of the IGTO thin-films deposited on the 15-nm-thick IGZO/SiO2/Si substrates. The Rrms increases to 0.8 nm in the 12-nm-thick IGTO thin-film, and this roughest surface could partially contribute to degradation of the electrical contact properties. The data obtained from the 0-nm-thick IGTO thin-film indicates information of the underlying 15-nm-thick IGZO thin-film. In addition to AFM analysis, Hall effect measurement was performed on the IGTO thin-films to investigate the origin of the tIGTO-dependent the electrical contact. The nc of the IGTO thin-film steadily increases from 7.9 × 1017 to 6.9 × 1019/cm3 with tIGTO (Fig. 5a). Moreover, its bulk resistivity (ρIGTO) simultaneously decreases from 1.1 Ω·cm to 3.7 × 10−3 Ω·cm, a trend originating from percolation conduction2. This result shows that the IGTO IL can act as an n+-layer in IGZO devices but cannot elucidate the tIGTO-dependent the electrical contact. Even, the fact that the 12-nm-thick IGTO thin-film has the lowest ρIGTO conflicts with the trend that the ρC and RCW are the lowest in the tIGTO of 8 nm.

Grazing-incidence X-ray diffraction (GIXRD) was conducted to investigate the crystalline structure of the IGTO thin-film (Fig. 5b). Surprisingly, the 12-nm-thick IGTO thin-film possesses a random polycrystalline In2O3 cubic bixbyite configuration, differing from the other tIGTO conditions. Electron transport can be enhanced by decreased defect scattering after crystallization due to structural ordering and defect confinement, which can contribute to the decrease in bulk ρIGTO observed in the Hall measurement. More importantly, this crystallographic change has a large impact on a metal/semiconductor (MS) interface, a critical factor in the electrical contact properties, and can result in a trend difference between the electrical contact and ρIGTO. However, it is possible that the IGTO thin-films with tIGTO < 12 nm were crystallized but too thin to determine their crystalline structure using GIXRD.

For this reason, cross-sectional high-resolution transmission electron microscopy (HRTEM) was performed on the ITO/TiN/IGTO/IGZO stacks to clearly examine the tIGTO-dependent crystallographic change (Fig. 6). It is noteworthy that electron dispersive spectroscopy (EDS) depth profile was conducted to distinguish the IGTO and IGZO layers (Fig. S5). There is no noticeable nano-/microscale crystal in the 8-nm-thick IGTO thin-film (Fig. 6a and Fig. S6). The fast Fourier transform (FFT) result also shows a diffused hollow ring pattern (Fig. S7). These results indicate that the corresponding IGTO thin-film has an amorphous structure. Meanwhile, the 12-nm-thick IGTO thin-film is crystallized (Fig. S8), and many crystal grains significantly infiltrate from the ITO into the IGTO film (Fig. 6b and Fig. S8). It is worth mentioning that the ITO thin-film has the same In2O3 cubic bixbyite crystalline configuration. Consequently, the MS interface is considerably deteriorated in the thin-film stack with tIGTO of 12 nm. These degradations are not observed in the stack with tIGTO of 8 nm (Fig. S6). This deteriorated interface could be attributed to the worse thermal stability of the polycrystalline structure with grain boundaries than the amorphous structure that make it susceptible to thermal stress during annealing. Thus, the polycrystalline 12-nm-thick IGTO thin-film could be more prone to deformation and cracking by thermal stress compared to the amorphous 8-nm-thick IGTO thin-film, as observed in the HRTEM analyses. Here, it is important to note that the interfacial property can significantly influence electrical contact properties. This is because a rough interface can introduce numerous scattering and localized trapping centers, thereby impeding electron injection at the MS contact region. Furthermore, such roughness can induce variations in the Schottky barrier height, resulting in fluctuations in the contact properties. Consequently, this TEM result implies that the electrical contact can be greatly degraded in a device using the multi-stack IL with tIGTO of 12 nm due to crystallization-induced disruptive interface even if it has the lowest bulk ρIGTO. This underscores the critical importance of the interfacial quality between the S/D electrodes and the channel layer.

Figure 7 shows electrical characteristics of IGZO TFTs with different IL structures. The IGZO TFTs without the IL exhibit device performances with μFE of 39.9 ± 1.6 cm2/Vs, current modulation ratio (ION/OFF) > 108, SS of 0.1 ± 0.03 V/dec, and VTH of − 0.5 ± 0.4 V. The μFE is improved to 42.7 ± 1.4 cm2/Vs through insertion of a 3-nm-thick TiN IL, and it further increases using the TiN/IGTO multi-stack IL. Importantly, the tIGTO-dependent behavior is clearly observed, with the IGZO TFTs with tIGTO of 8 nm exhibiting the highest μFE of 45.0 ± 1.6 cm2/Vs. Meanwhile, the devices with tIGTO of 5 and 12 nm showed μFE values of 44.8 ± 1.3 and 42.4 ± 1.8 cm2/Vs, respectively. Figure S9 shows VGS-dependent μFE curves in the IGZO TFTs with different IL conditions. Such improvement by IL insertion is also seen in output characteristics (Fig. 7f–j). All device performances of the IGZO TFTs with different IL stacks are summarized in Table 1. Considering the significant impact of electrical contact on the electrical characteristics of the TFT, it is straightforward to understand the trend where the highest device performances are revealed in the IGZO TFTs with tIGTO of 8 nm. This enhancement can be further pronounced in scaled oxide TFTs where the device performance is dictated by the electrical contact properties. Figure 8 and Table S1 are benchmarking graph and table, respectively. It is important to emphasize that the ρC (RCW) of 9.0 × 10−6 Ω·cm2 (0.7 Ω·cm) achieved in this study surpasses the state-of-the-art results reported in the literature for all types of multicomponent metal oxide transistors, demonstrating the superiority of this study.

(a–e) Transfer characteristics of IGZO TFTs with different IL stacks: (a) Without IL; (b) TiN IL; (c) TiN/IGTO IL (tIGTO = 5 nm); (d) TiN/IGTO IL (tIGTO = 8 nm); (e) TiN/IGTO IL (tIGTO = 12 nm). (f–j) Output characteristics: (f) Without IL; (g) TiN IL; (h) TiN/IGTO IL (tIGTO = 5 nm); (i) TiN/IGTO IL (tIGTO = 8 nm); (j) TiN/IGTO IL (tIGTO = 12 nm).

Conclusion

This study demonstrates a significant improvement in electrical contact properties of IGZO TFTs through insertion of a TiN/IGTO IL. The electrical contact properties are dependent on tIGTO, which is attributed to crystallographic change from the amorphous structure to the random polycrystalline structure of IGTO. Despite a decrease in bulk ρIGTO with increasing tIGTO, crystallization at tIGTO of 12 nm aggravates the electrical contact due to side effects such as grain boundary infiltration and degraded MS interfaces. Therefore, the use of an amorphous 8-nm-thick IGTO thin-film is more effective in improving the electrical contact properties. As a result, ρC (RCW) decreases from 8.0 × 10−4 (6.9) to 9.0 × 10−6 Ω·cm2 (0.7 Ω·cm) and μFE increases from 39.9 to 45.0 cm2/Vs, compared to the IGZO devices without the IL. This study not only highlights the effectiveness of the multi-stack IL approach in enhancing electrical contact properties, but also demonstrates that the effect can be maximized using a highly conductive amorphous IL. Importantly, this contact scheme can be applied to various types of oxide TFTs, not just IGZO TFTs.

Data availability

The datasets used and/or analysed during the current study available from the corresponding author on reasonable request. Correspondence and requests for materials should be addressed to J.K.J. or T. K. (email: jkjeong1@hanyang.ac.kr; tkim13@kist.re.kr).

References

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492. https://doi.org/10.1038/nature03090 (2004).

Kim, T. et al. Progress, challenges, and opportunities in oxide semiconductor devices: A key building block for application from display backplanes to 3D Integrated semiconductor chips. Adv. Mater. 35, 2204663. https://doi.org/10.1002/adma.202204663 (2023).

Chiang, H. Q., Wager, J. F., Hoffman, R. L., Jeong, J. & Keszler, D. A. High mobility transparent thin-film transistors with amorphous zinc tin oxide channel layer. Appl. Phys. Lett. 86, 013503. https://doi.org/10.1063/1.1843286 (2005).

Cho, M. H. et al. Impact of cation compositions on the performance of thin-film transistors with amorphous indium gallium zinc oxide grown through atomic layer deposition. J. Inf. Disp. 20, 73–80. https://doi.org/10.1080/15980316.2018.1540365 (2019).

Fortunato, E., Barquinha, P. & Martins, R. Oxide semiconductor thin-film transistors: A review of recent advances. Adv. Mater. 24, 2945–2986. https://doi.org/10.1002/adma.201103228 (2012).

Belmonte, A., Oh, H., Subhechha, S., Rassoul, N., Hody, H., Dekkers, H., Delhougne, R., Ricotti, L., Banerjee, K., Chasin, A., Setten, M. J. V., Puliyalil, H., Pak, M., Teugels, L., Tsvetanova, D., Vandersmissen, K., Kunde, S., Heijlen, J., Geypen, D. B. J., Goux, L. & Kar, G. S. Tailoring IGZO-TFT Architecture for Capacitorless DRAM, Demonstrating > 103s Retention, >1011 Cycles Endurance and Lg Scalability Down to 14 nm. IEEE International Electron Devices Meeting (IEDM) 10.6.1–10.6.4. https://doi.org/10.1109/IEDM19574.2021.9720596 (2021).

Belmonte, A., Oh, H., Rassoul, N., Donadio, G. L., Mitard, J., Dekkers, H., Delhougne, R., Subhechha, S., Chasin, M. J., Klijucar, L., Mao, M., Puliyalil, H., Park, M., Teugels, L., Tsventanova, D., Banerjee, K., Souriau, L., Tokei, Z. & Kar, G. S. Capacitor-less, long-retention (> 400s) DRAM cell paving the way towards low-power and high-density monolithic 3D DRAM. IEEE International Electron Devices Meeting (IEDM) 28–2. https://doi.org/10.1109/IEDM13553.2020.9371900 (2020).

Duan, X. et al. Novel vertical channel-all-around (CAA) In-Ga-Zn-O FET for 2T0C-DRAM with high density beyond 4F 2 by monolithic stacking. IEEE Trans. Electron Devices 69, 2196–2202. https://doi.org/10.1109/TED.2022.3154693 (2022).

Huang, K., Duan, X., Feng, J., Sun, Y., Lu, C., Chen, C., Jiao, G., Lin, X., Shao, J., Yin, S., Sheng, J., Wang, Z., Zhang, W., Chuai, X., Niu, J., Wang, W., Wu, Y., Jing, W., Wang, Z., Xu, J., Yang, G., Geng, D., Li, L. & Liu, M. Vertical Channel-All-Around (CAA) IGZO FET under 50 nm CD with High Read Current of 32.8 μA/μm (Vth + 1 V), Well-performed Thermal Stability up to 120 ℃ for Low Latency, High-density 2T0C 3D DRAM Application. IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 296–297. https://doi.org/10.1109/VLSITechnologyandCir46769.2022.9830271 (2022).

Park, E., Kim, S. H. & Yu, H. Y. Schottky barrier engineering with a metal nitride–double interlayer–semiconductor contact structure to achieve high thermal stability and ultralow contact resistivity. Appl. Surf. Sci. 531, 147329. https://doi.org/10.1016/j.apsusc.2020.147329 (2020).

Kupka, R. K. & Anderson, W. A. Minimal ohmic contact resistance limits to n-type semiconductors. J. Appl. Phys. 69, 3623–3632. https://doi.org/10.1063/1.348509 (1991).

Park, J. H., Seok, H. J., Jung, S. H., Cho, H. K. & Kim, H. K. Rapid thermal annealing effect of transparent ITO source and drain electrode for transparent thin film transistors. Ceram. Int. 47, 3149–3158. https://doi.org/10.1016/j.ceramint.2020.09.152 (2021).

Cho, E. N., Kang, J. H. & Yun, I. Contact resistance dependent scaling-down behavior of amorphous InGaZnO thin-film transistors. Curr. Appl. Phys. 11, 1015–1019. https://doi.org/10.1016/j.cap.2011.01.017 (2011).

Schroder, D. K. Semiconductor Material and Device Characterization 128–135 (Wiley, 2015).

Yu, A. Y. C. Electron tunneling and contact resistance of metal-silicon contact barriers. Solid State Electron. 13, 239–247. https://doi.org/10.1016/0038-1101(70)90056-0 (1970).

Liao, M. H. & Lien, C. The comprehensive study and the reduction of contact resistivity on the n-InGaAs MIS contact system with different inserted insulators. AIP Adv. 5, 057117. https://doi.org/10.1063/1.4921023 (2015).

Streetman, B. G. & Banerjee, S. Solid State Electronic Devices Vol. 7, 251–253 (Prentice Hall, 2000).

Kim, J.-K., Kim, S.-H., Kim, T. & Yu, H.-Y. Universal metal-interlayer-semiconductor contact modeling considering interface-state effect on contact resistivity degradation. IEEE Trans. Electron Devices 65, 4982–4987. https://doi.org/10.1109/TED.2018.2868833 (2018).

Kang, S. H. et al. Performance improvement of self-aligned coplanar amorphous indium–gallium–zinc oxide thin-film transistors by boron implantation. ACS Appl. Electron. Mater. 4, 2372–2379. https://doi.org/10.1021/acsaelm.2c00196 (2022).

Um, J. G. & Jang, J. Heavily doped n-type IGZO by F plasma treatment and its thermal stability up to 600° C. Appl. Phys. Lett. 112, 162104. https://doi.org/10.1063/1.5007191 (2018).

Park, H. et al. Enhancing the contact between IGZO and metal by hydrogen plasma treatment for a high-speed varactor (> 30 GHz). ACS Appl. Electron. Mater. 4, 1769–1775. https://doi.org/10.1021/acsaelm.2c00028 (2022).

Yang, S.-H. et al. Low resistance ohmic contacts to amorphous IGZO thin films by hydrogen plasma treatment. Surf. Coat. Technol. 206, 5067–5071. https://doi.org/10.1016/j.surfcoat.2012.06.017 (2012).

Liu, M. et al. Carrier density-tunable work function buffer at the channel/metallization interface for amorphous oxide thin-film transistors. ACS Appl. Electron. Mater. 3, 2703–2711. https://doi.org/10.1021/acsaelm.1c00284 (2021).

Hung, C.-H. et al. Improving source/drain contact resistance of amorphous indium–gallium–zinc-oxide thin-film transistors using an n+-ZnO buffer layer. Jpn. J. Appl. Phys. 55, 06GG05. https://doi.org/10.7567/JJAP.55.06GG05 (2016).

Kim, H., Kim, K. K., Lee, S. N., Ryou, J. H. & Dupuis, R. D. Low resistance Ti/Au contacts to amorphous gallium indium zinc oxides. Appl. Phys. Lett. 98, 112107. https://doi.org/10.1063/1.3567796 (2011).

Yun, P. S. & Koike, J. Metal reaction doping and ohmic contact with Cu–Mn electrode on amorphous In-Ga-Zn-O semiconductor. J. Electrochem. Soc. 158, H1034. https://doi.org/10.1149/1.3621723 (2011).

Choi, K. H. & Kim, H. K. Correlation between Ti source/drain contact and performance of InGaZnO-based thin film transistors. Appl. Phys. Lett. 102, 052103. https://doi.org/10.1063/1.4790357 (2013).

Okuno, N., Sato, Y., Jimbo, Y., Honda, H., Kurata, M., Wakuda, M., Kunitake, H., Kobayashi, M. & Yamazaki, S. Source/drain engineering by tantalum nitride (TaNx) electrode for boosting OSFET performance. IEEE International Electron Devices Meeting (IEDM) 37–45. https://doi.org/10.1109/IEDM19574.2021.9720629 (2021).

Huang, X. D., Song, J. Q. & Lai, P. T. Improved performance of scaled-down a-InGaZnO thin-film transistor by Ar plasma treatment. IEEE Electron. Device Lett. 37, 1574–1577. https://doi.org/10.1109/LED.2016.2615879 (2016).

Park, J. S., Jeong, J. K., Mo, Y. G., Kim, H. D. & Kim, S. I. Improvements in the device characteristics of amorphous indium gallium zinc oxide thin-film transistors by Ar plasma treatment. Appl. Phys. Lett. 90, 262106. https://doi.org/10.1063/1.2753107 (2007).

Duan, X. et al. A direct n+-formation process by magnetron sputtering an inter-layer dielectric for self-aligned coplanar indium gallium zinc oxide thin-film transistors. Micromachines 13, 652. https://doi.org/10.3390/mi13050652 (2022).

Moon, S. H., Kwon, Y. H., Seong, N. J., Choi, K. J. & Yoon, S. M. Performance enhancement of self-aligned coplanar TFTs with ALD-IGZO channels via effective doping from interlayer dielectric. IEEE Electron. Device Lett. 44, 1128–1131. https://doi.org/10.1109/LED.2023.3274811 (2023).

Kim, D. G., Ryu, S. H., Jeong, H. J. & Park, J. S. Facile and stable n+ doping process via simultaneous ultraviolet and thermal energy for coplanar ALD-IGZO thin-film transistors. ACS Appl. Electron. Mater. 3, 3530–3537. https://doi.org/10.1021/acsaelm.1c00463 (2021).

Noh, S. H. et al. Improvement in short-channel effects of the thin-film transistors using atomic-layer deposited In–Ga–Sn–O channels with various channel compositions. IEEE Trans. Electron Devices 69, 5542–5548. https://doi.org/10.1109/TED.2022.3198032 (2022).

Lee, D. H. et al. Analysis on contact resistance and effective channel length of thin film transistors using composition-modified In–Ga–Zn-O active channels prepared with atomic layer deposition and various electrode materials. ACS Appl. Electron. Mater. 4, 6215–6228. https://doi.org/10.1021/acsaelm.2c01342 (2022).

Chen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217. https://doi.org/10.1038/s41586-021-03472-9 (2021).

Choi, M. H. et al. High-performance indium-based oxide transistors with multiple channels through nanolaminate structure fabricated by plasma-enhanced atomic layer deposition. ACS Appl. Mater. Interfaces 15, 19137–19151. https://doi.org/10.1021/acsami.3c00038 (2023).

Acknowledgements

This work was supported by the National Research Foundation (NRF) Grant funded by the Korean government (NRF-2022M3H4A6A01035636 and RS-2023-00260527), and the Samsung Electronics Co., Ltd. (IO230726-06845-01 and IO201210-08034-01).

Author information

Authors and Affiliations

Contributions

J.H.J., S.W.S. and J.K.J. designed this work. J.H.J., T.K. and J.K.J. wrote the main text. S.W.S., J.H.J. D.K. and T.K. fabricated and characterized the devices. All authors discussed the results and commented on the manuscript. J.H.J. and S.W.S. equally contributed to this work. The projects were supervised by J.K.J. All authors reviewed the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Jeong, J.H., Seo, S.W., Kim, D. et al. Specific contact resistivity reduction in amorphous IGZO thin-film transistors through a TiN/IGTO heterogeneous interlayer. Sci Rep 14, 10953 (2024). https://doi.org/10.1038/s41598-024-61837-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-024-61837-2

- Springer Nature Limited