Abstract

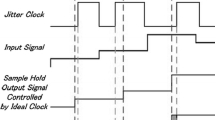

This paper presents a theoretical overview and analysis of clock jitter in a switched capacitor (SC) Sigma-Delta (ΣΔ) Analog-to-Digital Converter (ADC). We start by defining three different types of jitter effects and proceed to analyze their impact, both mathematically and by simulations. The main jitter assumption throughout this analysis is that it is stochastic white Gaussian noise. Using this assumption, the ΣΔ performance is characterized in terms of Signal-to-Jitter-Noise-Ratio (SJNR) for each jitter effect. Non-uniform sampling effects have, to some extent, been characterized in litterature (S.R. Norsworthy, R. Schreier and G.C. Temes, Delta-Sigma Data Converters—Theory, Design and Simulation, IEEE Press, New Jersey, 1997). However, varying phase-length effects are also a main focus in this work since they can have a significant impact on the total ADC performance depending on settling accuracy and characteristic. Furthermore, because SC circuits usually operate on a two-phase clock, jitter may give rise to a secondary effect, phase overlap, which does not appear when dealing with a single-phase clock. This effect severely degrades the resolution of a ΣΔ and therefore a thorough understanding of the interaction of jitter on the two phases is necessary.

Similar content being viewed by others

References

S.R. Norsworthy, R. Schreier, and G.C. Temes, Delta-Sigma Data Converters—Theory, Design and Simulation. IEEE Press, New Jersey, 1997.

H. Tao, L. Toth, and J.M. Khoury, “Analysis of timing jitter in bandpass sigma-delta modulators.” IEEE Transactions on Circuits and Systems II—Analog and Digital Signal Processing, vol. 46, pp. 991–1001, 1999.

H. Kobayashi, M. Morimura, K. Kobayashi, and Y. Onaya, “Aperture jitter effects in wideband ADC systems,” in Proceedings of the IEEE International Conference on Electronics, Circuits and Systems, 1999, vol. 3, pp. 1705–1708.

B. Jonsson, S. Signell, H. Stenstrm, and N. Tan, “Distortion in sampling,” in Proceedings of the IEEE International Symposium on Circuits and Systems, 1997, pp. 445–448.

T. Karema, T. Ritoniemi, and H. Tenhunen, “Fourth order sigma-delta modulator circuit for digital audio and ISDN applications”, in Proceedings of the IEE European Conference on Circuit Theory and Design, 1989, pp. 223–227.

A. Gothenberg and H. Tenhunen, “Nonlinear quantization in low oversampling ratio sigma-delta noise shapers for RF applications.” International Journal of Analog Integrated Circuits and Signal Processing, vol. 30, pp. 193–206, 2002.

P. Zhu and H. Tenhunen, “Design and analysis of a CMOS switched-current sigma-delta modulator using multi level simulations.” International Journal of Analog Integrated Circuits and Signal Processing, vol. 15, pp. 153–168, 1997, Kluwer Academic Publishers, Boston, U.S.A.

A. Gothenberg and H. Tenhunen, “Analysis of substrate noise coupling effects on sigma delta noise shapers,” in Proceedings of the IEEJ International Analog VLSI Workshop, 2000, pp. 43–46.

K. Uchimura, T. Hayashi, T. Kimura, and A. Iwata, “Oversampling A-to-D and D-to-A converters with multistage noise shaping modulators.” IEEE Transactions on Acoustics, Speech, and Signal Processing, vol. AASP-36, pp. 1899–1905, 1988.

Y. Dong, “Noise and clock jitter analysis of sigma-delta modulators and periodically switched linear networks.” Ph.D. thesis, University of Waterloo, Waterloo, Ontario, Canada, 1999.

A. Gothenberg and H. Tenhunen, “Performance analysis of low oversampling ratios sigma-delta noise shapers for RF-applications,” in Proceedings of the IEEE International Symposium on Circuits and Systems,vol. 1, pp. 401–404, 1998.

A. Strak, A. Gothenberg, and H. Tenhunen, “Analysis of clock jitter effects in wideband sigma-delta modulators for RF-applications,” in IEEE Intl. Conference on Electronics, Circuits and Systems (ICECS), pp. 339–342, 2002.

T. Karema, T. Ritoniemi, and H. Tenhunen, “An oversampled sigma-delta A/D converter circuit using two-stage fourth order modulator,” in Proceedings of the IEEE International Symposium on Circuits and Systems, 1990, pp. 3279–3282.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Strak, A., Gothenberg, A. & Tenhunen, H. Analysis of Clock Jitter Effects in Wideband Sigma-Delta Modulators for RF-Applications. Analog Integrated Circuits and Signal Processing 41, 223–236 (2004). https://doi.org/10.1023/B:ALOG.0000041638.12447.7d

Issue Date:

DOI: https://doi.org/10.1023/B:ALOG.0000041638.12447.7d