Abstract

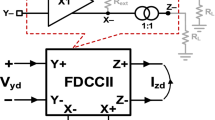

A novel circuit of the low-voltage application-specific amplifier is proposed and analyzed. A wide-band current amplifying cell is developed as a central part of the amplifier structure. The amplifier is designed for a built-in-current-sensor, on-chip circuitry used in high-frequency power supply current monitoring and test applications. It could be implemented with analog, digital, or mixed-signal cores in an integrated system-on-chip environment. The current amplifier has been fabricated in 0.13 and 0.18 μm CMOS technology processes with 1.2 and 1.8 V power supply, respectively. The impacts of technology scaling on amplifier's performances have been investigated as well. With sensitivity better than 500 nA, the 0.13 μm design achieves the gain-bandwidth product of 6.8 GHz, low frequency current gain of 48 dB, high linearity for the input current range of (−15 μA, 15 μA), and power consumption of 5.2 mW.

Similar content being viewed by others

References

Kuo-Hsing Cheng and Huei-Chi Wang, “Design of current mode operational amplifier with differential input and differential output,” in Proc. Int. Symposium on Circuits and Systems, Hong Kong, 1997, vol. 1, pp. 153–156.

B. Wilson, “Trends in current conveyor and current-mode amplifier design.” Int. J. of Electronics, vol. 73, no 3, pp. 573–383, 1992.

C. Thibeault, “On the comparison of IDDQ and IDDQ testing,” in Proc. 17th IEEE VLSI Test Symposium, San Diego, California, April 26–30, 1999, pp. 538–542.

T.J. Powell, J. Pair, M. St. John, and D. Counce, “IDDQ for testing reliability,” in Proc. 18th IEEE VLSI Test Symposium, Montreal, Canada April 30–May 4, pp. 439–443, 2000.

W. Maly and A. Patyra, “Built-in current testing.” IEEE Journal of Solid State Circuits, vol. 27, no. 3, pp. 425–428, 1992.

I.M. Bell, D.A. Camplin, G.E. Taylor, and B.R. Bannister, “Supply current testing of mixed analogue and digital ICs.” Electronics Letters, vol. 27, no. 17, pp. 1581–1586, 1991.

K. Arabi and B. Kaminska, “Design and realization of an accurate built-in current sensor for on-line power dissipation measurement and IDDQ testing,” in Proc. IEEE International Test Conference, Washington, DC, USA, Nov. 3–5, 1997, pp. 578–586.

V. Stopjakova, H. Manhaeve, and M. Sidiropulos, “On-chip transient current monitor for testing of low-voltage CMOS IC,” in Proc. Design, Automation and Test in Europe Conference, Munich, Germany, March 1999, pp. 538–542.

H. Kim, D.M.H. Walker, and D. Colby, “A Practical built-in current sensor for IDDQ testing,” in Proc. IEEE International Test Conference, 30 October–1 November, 2001, Baltimore, MD, USA, pp. 405–414, 2001.

J.-B. Kim, J.-S. Hong, and J. Kim, “Design of a built-in current sensor for IDDQ testing.” IEEE Journal of Solid-state Circuits, vol. 33, no. 8, pp. 1266–1272, 1998.

Siskos et al., “A simple built-in current sensor for current monitoring in mixed-signal circuits.” IEEE Transactions on Instrumentation and Measurement, pp. 1301–1304, 1997.

D.M.H. Walker, “Requirements for practical IDDQ testing of deep submicron circuits,” in Dig. IEEE International Workshop on Defect Based Testing (DBT), Montreal, Quebec, April 2000, pp. 15–20.

S. Dragic and M. Margala, “Application specific low-voltage current amplifier for system-on-chip IDDQ test,” in Proc. 9th IEEE International Conference on Electronics, Circuits, and Systems, Dubrovnik, Croatia, Sept. 15–18, 2002, pp. 397–400.

I.M. Filanovsky, A. Allam, and S.T. Lim, “Temperature dependence of output voltage generated by interaction of threshold voltage and mobility of an NMOS transistor.” Analog Integrated Circuits and Signal Processing, Kluwer Academic Publishers, vol. 27, no. 3, pp. 229–238, 2001.

C. Toumazou, F.J. Lidgey, and D.G. Haigh, Analogue IC design: The current-mode approach. Peter Peregrinus Ltd, London, UK, 1990.

Th. Laopoulos, S. Siscos, M. Bafleur, and Ph. Givelin, “CMOS current conveyor.” Electronics Letters, vol. 28, no. 24, pp. 2261–2262, 1992.

W. Surakampontorn, V. Riewruja, K. Kumwachara, and K. Dejhan, “Accurate CMOS-based current conveyors.” IEEE Transactions on Instrumentation and Measurement, vol. 40, no. 4, pp. 699–702, 1991.

D.A. Johns and K. Martin, Analog Integrated Circuit Design, Wiley, New York, 1997.

D.P. Foty, MOSFET Modeling with SPICE, Prentice Hall, Upper Saddle River, NJ, 1997.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Dragic, M.S., Filanovsky, I.M. & Margala, M. A Novel On-Chip Amplifier for Fast I DD Current Monitoring. Analog Integrated Circuits and Signal Processing 41, 185–198 (2004). https://doi.org/10.1023/B:ALOG.0000041635.23947.a8

Issue Date:

DOI: https://doi.org/10.1023/B:ALOG.0000041635.23947.a8