Abstract

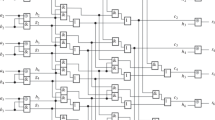

This paper shows how a parallel prefix adder computing S = A + B may be slightly modified to yield a new adder structure, called a “flagged prefix adder”, capable of returning therelated computation pairs A + B and A + B + 1, or, if the bits of B are inverted, A − B and B − A. This adder is of use in digital communications applications and video compression, as well as arithmetic processor designs. The new adder uses 25% less transistors than the conditional-sum adder, which has been used previously in such situations.

Similar content being viewed by others

References

S.C. Knowles, “Arithmetic Processor Design for the T9000 Transputer,” in Proc. SPIE,. vol. 1566, ASPAAI-2, San Diego, July 1991, pp. 230-243.

J. Sklansky, “Conditional-Sum Addition Logic,” IRE Transactions on Electronic Computers, vol. 9, 1960, pp. 226-231.

O.J. Bedrij, “Carry-Select Adder,” IRE Transactions on Electronic Computers, vol. 11, 1962, pp. 340-346.

M.R. Santoro, G. Bewick, and M.A. Horowitz, “Rounding Algorithms for IEEE Multipliers,” in Proc. 9th IEEE Symp. Computer Arithmetic, Santa Monica, Sept. 1989, pp. 176-183.

R.K. Yu and G.B. Zyner, “167 MHz Floating-Point Multiplier,” in Proc. 12th IEEE Symp. Computer Arithmetic, Bath, July 1995, pp. 149-154.

A. Omondi, Computer Arithmetic Systems, Englewood Cliffs, NJ: Prentice-Hall, 1994.

R.P. Brent, “On the Addition of Binary Numbers,” IEEE Transactions on Computers, vol. 19, 1970, pp. 758-760.

S.C. Knowles, “A Family of Adders,” in Proc. 14th IEEE Symp. Computer Arithmetic, Adelaide, April 1999, pp. 30-34.

A. Farooqui, V.G. Oklobdzija, and F. Chehrazi, “Multiplexer Based Adder for Media Signal Processing,” in Proc. IEEE Int. Symp. on VLSI Technology, Systems, and Applications, Taipei, June 1999, pp. 100-103.

A. Tyagi, “A Reduced-Area Scheme for Carry-Select Adders,” IEEE Transactions on Computers, vol. 42, 1993, pp. 1163-1170.

M.J. Flynn et al., “The SNAP Project: Towards Sub-Nanosecond Arithmetic,” in Proc. 12th IEEE Symp. Computer Arithmetic, Bath, July 1995, pp. 75-82.

N. Burgess and S.C. Knowles, “Efficient Implementation of Rounding Units,” in Proc. 33rd Asilomar Conference on Signals, Systems and Computers, Asilomar, CA, Oct. 1999.

A Beaumont-Smith et al., “Reduced Latency IEEE Floating-Point Adder Architectures,” in Proc. 14th IEEE Symp. Computer Arithmetic, Adelaide, April 1999, pp. 35-42.

R.E. Ladner and M.J. Fischer, “Parallel Prefix Computation,” J. ACM, vol. 27, 1980, pp. 831-838.

N. Burgess, “The Flagged Prefix Adder for Dual Additions,” in Proc. SPIE, vol. 3461, ASPAAI-8, San Diego, July 1998, pp. 567-575.

S.C. Knowles, “Simultaneous Arithmetic,” British Patent Application, no. 9813328.3, June 1998.

J.M. Rabaey, Digital Integrated Circuits: A Design Perspective, Upper Saddle River, NJ: Prentice Hall, 1996.

R. Zimmermann, “Efficient VLSI Implementation of Modulo 2n ± 1 Addition and Multiplication,” in Proc. 14th IEEE Symp. Computer Arithmetic, Adelaide, April 1999, pp. 158-167.

P.M. Kogge and H.S. Stone, “A Parallel Algorithm for the Efficient Solution of a General Class of Recurrence Relations,” IEEE Transactions on Computers, vol. 22, 1973, pp. 786-793.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Burgess, N. The Flagged Prefix Adder and its Applications in Integer Arithmetic. The Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology 31, 263–271 (2002). https://doi.org/10.1023/A:1015421507166

Published:

Issue Date:

DOI: https://doi.org/10.1023/A:1015421507166