Abstract

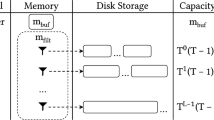

We present the design, implementation, and evaluation of single assignment data structures and of a software controlled cache in an existing multi-threaded architecture platform – the Efficient Architecture for Running Threads (EARTH). The I-Structure Software-Controlled Cache (ISSC) exploits temporal and spatial locality of EARTH split-phased memory transactions for single-assignment memory references. Our experimental evaluation indicates that the caching mechanism for single-assignment storage makes the EARTH memory system more robust to variations in the latency of memory operations. As a consequence the system can be ported to a wider range of machine platforms and deliver speedup for both regular and irregular application.

Similar content being viewed by others

References

J.N. Amaral, Z. Ruiz, S. Ryan, A. Marques, C. Morrone and G.R. Gao, Portable Threaded-C - Release 1.1, Technical Note 05, Computer Architecture and Parallel System Laboratory, University of Delaware (September 1998).

Arvind, R.S. Nikhil and K.K. Pingali, I-Structures: Data structures for parallel computing, ACM TOPLAS 11(4) (October 1989).

D.H. Bailey, J.T. Barton, T.A. Lasinski and H.D. Simon, The NAS parallel benchmarks, Technical Report NASA Technical Memorandum 103863, NASA Ames Research Center (July 1993).

D. Culler, R. Karp, D. Patterson, A. Sahay, K. Schauser, E. Santos, R. Subramonian and T. von Eicken, LogP: Towards a realistic model of parallel computation, in: Proc. 4th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming (May 1993).

D.E. Culler, S.C. Goldstein, K.E. Schauser and T. von Eicken, Empirical study of a dataflow language on the CM-5, in: Advanced Topics in Dataflow Computing and Multithreading, eds. G.R. Gao, L. Bic and J.-L. Gaudiot (IEEE Press, 1994) pp. 187–210.

J.B. Dennis and G.R. Gao, On memory models and cache management for shared-memory multiprocessors, ACAPS Technical Memo 90, School of Computer Science, McGill University (December 1994).

G.R. Gao, An efficient hybrid dataflow architecture model, Journal of Parallelism 19(4) (December 1993).

G.R. Gao, H.H.-J. Hum and Y.-B. Wong, Parallel function invocation in a dynamic argument-fetching dataflow architecture, in: Proc. of PARBASE-90: Int. Conf. on Databases, Parallel Architectures, and their Applications, Miami Beach, Florida (March 1990) pp. 112–116.

W.K. Giloi, U. Bruning and W. Schroder-Preikschat, MANNA: Prototype of a distributed memory architecture with maximized sustained performance, in: Proc. Euromicro PDP96 Workshop (1996).

H.H.-J. Hum, The Super-Actor Machine: a Hybrid Dataflow/von Neumann Architecture, Ph.D. thesis, McGill University, Montreal (May 1992).

H.H.-J. Hum, O. Maquelin, K.B. Theobald, X. Tian, X. Tang, G. Gao, P. Cupryk, N. Elmasri, L.J. Hendren, A. Jimenez, S. Krishnan, A. Marquez, S. Merali, S.S. Nemawarkar, P. Panangaden, X. Xue and Y. Zhu, A design study of the EARTH multiprocessor, in: PACT 95 (June 1995).

V. Karamcheti and A. Chien, Software overhead in messaging layers: Where does the time go? in: Proc. 6th ACM Int. Conf. on Architectural Support for Programming Languages and Systems (ASPLOS VI) (5- 7 October 1994).

K.M. Kavi, A.R. Hurson, P. Patadia, E. Abraham and P. Shanmugam, Design of cache memories for multi-threaded dataflow architecture, in: ISCA 95 (1995) pp. 253–264.

K. Keeton, T. Anderson and D. Patterson, LogP quantified: The case for low-overhead local area networks, in: Hot Interconnects III: A Symposium on High Performance Interconnects (August 1995).

W.Y. Lin, J.N. Amaral, J.-L. Gaudiot and G. Gao, Caching singleassignment structures to build a robust fine-grain multi-threading system, in: International Parallel and Distributed Processing Symposium (IPDPS2000) (May 2000) pp. 589–601.

W.Y. Lin and J.-L. Gaudiot, I-Structure software caches - a split-phase transaction runtime cache system, in: PACT 96 (October 1996).

W.Y. Lin and J.-L. Gaudiot, Exploiting global data locality in nonblocking multithreaded architectures, in: Proc. 3rd Int. Symposium on Parallel Architectures, Algorithms and Networks (December 1997).

W.Y. Lin and J.-L. Gaudiot, The design of an I-structure software cache system, in: MTEAC 98 (February 1998).

W.Y. Lin, J. Nelson, J.-L. Gaudiot and G. Gao, Performance analysis of the I-structure software cache on multi-threading systems, in: 19th IEEE International Performance, Computing and Communications Conference (IPCCC2000) (February 2000) pp. 83–89.

S. Rodrigues, T. Anderson and D. Culler, High-performance local area communication with fast sockets, in: USENIX 1997 Annual Technical Conference (January 1997).

K.B. Theobald, EARTH - an Efficient Architecture for Running THreads, Ph.D. thesis, School of Computer Science, McGill University, Montreal, Québec (1999).

T. von Eicken, D.E. Culler, S.C. Goldstein and K.E. Schauser, Active messages: a mechanism for integrated communication and computation, in: ISCA 92 (19- 21 May 1992) pp. 256–266.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Amaral, J.N., Lin, WY., Gaudiot, JL. et al. Exploiting Locality in Single Assignment Data Structures Updated Through Split-Phase Transactions. Cluster Computing 4, 281–293 (2001). https://doi.org/10.1023/A:1011808526481

Issue Date:

DOI: https://doi.org/10.1023/A:1011808526481