Abstract

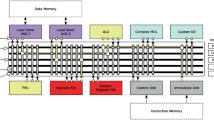

High-performance, reliable, and robust products with a short development schedule are general design aims. FACE was developed to achieve these goals, including the organization of a design flow, a frequency-driven information analyzer, compiler techniques (code generator and instruction optimization), and a hierarchical object design library. This paper explores the design space of a retargetable compiler and a reconfigurable hardware, which combine both software and hardware reprogrammability. The environment, FACE, we have developed allows us to quickly move the functions between software and hardware in a state of flux. Finally, it generates the application specific integrated processor (ASIP) and a compiler for the new ASIP architecture. The case study is considered which demonstrates the efficiency in ASIP design of FACE.

Similar content being viewed by others

References

J. Sato et al. PEAS-I: A hardware/software codesign system for ASIP development. IEICE Trans. Fundamentals of Electronics, Communications and Computer Sciences E77-A(3): 483-491, Mar. 1994.

R. M. Stallman. Using and porting GNU CC. Free Software Foundation, Version 2.7, 1996.

I. J. Huang et al. Synthesis of application specific instruction sets. IEEE Trans. Computer-Aided Design 14(6): 663-675, June 1995.

W. Stephen. VHDL Analysis and Modeling of Digital Systems. McGRAW-HILL, 1993.

T. M. Conte et al. Challenges to combining general-purpose and multimedia processors. IEEE Computer 33-37, Dec. 1997.

F. Lai, S. L. Hwang, and T. S. Chen. ARDEN — ARchitecture Development ENvironment. IEEE TENCON'93, Oct. 1993.

T. S. Chen, F. Lai et al. Peephole optimizer in retargetable compilers. IEICE Trans. Information and Systems E79-D(9): 1248-1256, Sept. 1996.

F. Lai and Y. K. Chao. The complementary relationship of interprocedure register allocation and inlining. International Conference on Computer Languages, Toulouse, France, pp. 253-264, May 1994.

D. Morris et al. Object Oriented Computer Systems Engineering. Springer-Verlag, 1996.

S. Kumar et al., A framework for hardware/software codesign. University of Virginia, Technical Report No. 920525.0, 1992.

P. Darche et al. ActNet: the actor model applied to mobile robitic environments. Object-Based Parallel and Distributed Computation, selected papers of OBPDC'95, LNCS N. DG 1107, Springer-Verlag, 273-289, 1996.

S. Kumar et al. Object-oriented techniques in hardware design. IEEE Computer 64-70, June 1994.

N. N. Binh et al. A hardware/software partitioning algorithm for pipelined instruction set processor. Proc. of Euro-DAC'95 176-181, 1995.

D. A. Patterson and J. L. Hennessy. Computer Architecture: A Quantitative Approach, Morgan Kaufmann Publishers, 1996.

D. Hearn and M. P. Baker. Computer Graphics. Prentice-Hall, 1986.

R. Sedgewick. Algorithms in C. Addison-Wesley, 1990.

D. Bistry et al. The Complete Guide to MMX Technology. McGraw-Hill, 1997.

S. D. Conte and Carl de Boor. Elementary Numerical Analysis: An Algorithmic Approach. McGraw-Hill, 1980.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Jeng, IH., Lai, F. & Tseng, YD. FACE: Fine-tuned Architecture Codesign Environment for ASIP Development. Design Automation for Embedded Systems 4, 329–351 (1999). https://doi.org/10.1023/A:1008973722314

Issue Date:

DOI: https://doi.org/10.1023/A:1008973722314