Abstract

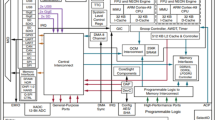

A single chip system for real–time MPEG–2 decoding can be created by integrating a general purpose dual–issue RISC processor, with a small dedicated hardware for the variable length decoding (VLD) and block loading processes; a 32KB instruction RAM; and a 32KB data RAM. The VLD hardware performs Huffman decoding on the input data. The block loader performs the half–sample prediction for motion compensation and acts as a direct memory access (DMA) controller for the RISC processor by transferring data between an external 2MB DRAM and the internall 32 KB data RAM. The dual-issue RISC processor, running at 250MHz, is enhanced with a set of key sub-word and multimedia instructions for a sustained peak performance of 1000 MOPS. With this setup for MPEG-2 decoding applications, bi-directionally predicted non-intra video blocks are decoded in less than 800 cycles, leading to a single-chip, real-time MPEG-2 decoding system.

Similar content being viewed by others

References

T. Demura, T. Oto, K. Kitagaki, and S. Ishiwata et al, “A single-chip MPEG2 video decoder LSI,” in ISSCC, 1994, pp.72–73.

M. Toyokura, M. Saishi, S. Kurohmaru, and K. Yamauchi et al, “A video DSP with a macroblock-level-pipeline and a SIMD type vector-pipeline architecture for MPEG2 CODEC,” in ISSCC, 1994, pp. 74–75.

M. Matsui, H. Hara, K. Seta, and Y. Uetani et al, “200MHz video compression macrocells using low-swing differential logic, in ISSCC, 1994, pp. 76–77.

S. Uramoto, Y. Inoue, and A. Takabatake et al, “A 100 MHz 2-D discrete cosine transform core processor,” Journal of Solid-State Circuits, vol. 27, April 1992, pp. 492–499.

U.Totzek, F. Matthiesen, S.Wohlleben, and T.G. Noll, “CMOS VLSI implementation of the 2D-DCT with linear processor arrays,” in ICASSP, April 1990, pp. 937–940.

K. Nadehara, M. Hayashida, and I. Kuroda, “A low-power, 32-bit RISC processor with signal processing capability and its multiply-adder,” in VLSI Signal Processing, VIII, October 1995, pages 51–60.

A. Charnas, A. Dalal, P. deDood, and P. Ferolito et al, “A 64b microprocessor with multimedia support,” in ISSCC, 1995, pp. 178–179.

C.-G. Zhou, L. Kohn, D. Rice, I. Kabir, A. Jabbi, and X.-P. Hu, “MPEG video decoding with the UltraSPARC visual instruction set,” in Compcon, Spring 1995, pp. 470–475.

R.B. Lee, “Accelerating multimedia with enhanced microprocessors,” IEEE Micro, April 1995, pp. 22–32.

R.B. Lee, “Realtime MPEG video via software decompression on a PA-RISC processor,” in Compcon, Spring 1995, pp. 186–192.

B. Case, “First trimedia chip boards PCI bus – VLIW multimedia engine aimed at PCs, set-top boxes,” Microprocessor Report, vol. 9, 1995, pp. 22–25.

D. Epstein, “Chromatic raises the multimedia bar,” Microprocessor Report, vol. 9, 1995, pp. 23–27.

T. Takayanagi, K. Nogami, F. Hatori, and N. Hatanaka et al, “350MHz time-multiplexed 8-port SRAM and word-size variable multiplier for multimedia DSP,” in ISSCC, 1996, pp. 150–151.

E. Holmann, T. Yoshida, A. Yamada, and Y. Shimazu, ”A VLIW processor for multimedia applications,” in HOT Chips 8 Symposium, 1996, pp. 193–202.

T. Yoshida, Y. Shimazu, A. Yamada, and E. Holmann et al, “A 2V 250MHz multimedia processor,” in ISSCC, 1997, pp. 266–267.

International Organisation for Standardisation, Generic Coding of Moving Pictures and Associated Audio Information: Video, 1994. Recommendation ITU-T H.262. ISO/IEC 13818-2.

N. Ahmed, T. Natarajan, and K. R. Kao, “Discrete cosine transform,” Trans. on Computers, vol. 23, 1974, pp. 90–93.

I. Kuroda, “Processor architecture driven algorithm optimization for fast 2D-DCT,” in VLSI Signal Processing, VIII, 1995, pp. 481–490.

E. Feig and S. Winograd, “Fast algorithms for the discrete cosine transform,” Trans. on Acoustics, Speech, and Signal Processing, vol. 40, 1992, pp. 2174–2193.

M.Al. Haque, A two-dimensional fast cosine transform,” Trans. on Acoustics, Speech, and Signal Processing, vol. 33, 1985, pp. 1532–1539.

J. Makhoul, A fast cosine transform in one and two dimensions,” Trans. on Acoustics, Speech, and Signal Processing, vol. 28, 1980, pp. 27–34.

W.-H. Chen, C.H. Smith, and S. C. Fralick, “A fast computational algorithm for the discrete cosine transform,” Trans. on Comm., vol. 25, 1977, pp. 1004–1009.

C. Loeffler, A. Ligtenberg, and G. Moschytz, “Practical fast 1-D DCT algorithm with 11 multiplications,” in ICASSP, 989, pp. 988–991.

B.G. Lee, “A new algorithm to compute the discrete cosine transform,” Trans. on Acoustics, Speech, and Signal Processing, vol. 32, 1984, pp. 1243–1245.

K. R. Rao and P. Yip, Discrete Cosine Transform: Algorithms, Advantages, Applications, San Diego, CA: Academic Press, 1990.

IEEE CAS Standards Committee for submission to the IEEE Standards Board, Standard Specification for the Implementations of 8x8 Inverse Discrete Cosine Transform, 1990.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Holmann, E., Yoshida, T., Yamada, A. et al. Single Chip Dual–Issue RISC Processor for Real–Time MPEG–2 Software Decoding. The Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology 18, 155–165 (1998). https://doi.org/10.1023/A:1008079712533

Published:

Issue Date:

DOI: https://doi.org/10.1023/A:1008079712533