Abstract

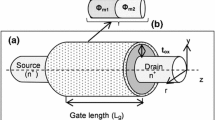

In this research paper, we present a comprehensive simulation study focused on a specific type of MOSFET called the triple material gate all around (GAA) MOSFET. The study incorporates an inner gate engineering approach, utilizing a high-K dielectric insulator to facilitate the downsizing of the device. Our investigation primarily compares the performance of the triple material gate GAA MOSFET with a similar MOSFET design incorporating triple material inner gate engineering. We evaluate a range of parameters, including drain current (ID), threshold voltage (Vth), transconductance (gm), higher-order transconductance (gm2, gm3, gm4), transconductance generation factor (TGF), second-order voltage coefficient (VIP2), and third-order voltage coefficient (VIP3). The findings of our study highlight the linearity analysis of the proposed device, particularly in the context of lower technology nodes. Based on our results, we posit that the triple material gate GAA MOSFET with inner gate engineering holds substantial promise as a potential candidate for future semiconductor applications. technologies.

Similar content being viewed by others

References

C.P. Auth, J.D. Plummer, Scaling theory for cylindrical, fully depleted, surrounding gate MOSFETs. IEEE Electron. Device Lett. 18, 74 (1997)

T.K. Chiang, A scaling theory for fully depleted, surrounding-gate MOSFET’s: including effective conducting path effect. Microelectron. Eng. 77, 2175 (2005)

N.A. Kumari, V.B. Sreenivasulu, P. Prithvi, Impact of scaling on Nanosheet FET and CMOS Circuit Applications. ECS J. Solid State Sci. Technol. 12, 033001 (2023)

A. Kranti, S. Haldar, R.S. Gupta, Analytical model for threshold voltage and I-V characteristics of fully depleted short channel cylindrical/surrounding gate MOSFET. Microelectron. Eng. 56, 241 (2001)

K. Bhol, B. Jena, U. Nanda, Silicon Nanowire GAA-MOSFET: a workhorse in nanotechnology for future semiconductor devices. Silicon. 14, 3163 (2022)

F. Liu, J. He, L. Zhang, J. Zhang, J. Hu, C. Ma, M. Chan, A charge-based model for long-Channel Cylindrical Surrounding-gate MOSFETs from Intrinsic Channel to heavily doped body. IEEE Trans. Electron. Devices. 55, 2187 (2008)

K. Bhol, B. Jena, U. Nanda, Journey of Mosfet from planar to gate all around: a review. Recent Pat. Nanotechnol. 16, 326 (2022)

S. Samia, D. Bouaza, High dielectric permittivity impact on SOI double gate MOSFET. Microelectron. Eng. 112, 213 (2013)

R. Gautam, M. Saxena, R.S. Gupta, M. Gupta, Effect of localised charges on nanoscale cylindrical surrounding gate MOSFET: Analog performance and linearity analysis. Microelectron. Reliab. 52, 989 (2012)

K.P. Pradhan, S.K. Mohapatra, P.K. Sahu, D.K. Behera, Impact of high-k gate dielectric on analog and RF performance of nanoscale DG-MOSFET. Microelectron. J. 45, 144 (2014)

B. Jena, S. Dash, G.P. Mishra, Improved switching speed of a CMOS inverter using work-function modulation engineering. IEEE Trans. electron. Devices. 65, 2422 (2018)

C.N. Venkatesh, G.P. Mishra, B. Jena, Design of Core Gate Silicon Nanotube RADFET with Improved Sensitivity. ECS J. Solid-State Sci. Technol. 11, 081002 (2022)

B. Jena, S. Dash, G.P. Mishra, Inner-Gate-Engineered GAA MOSFET to enhance the Electrostatic Integrity NANO: brief reports and reviews, 14 (2019),1950128

W. Long, H. Ou, J.M. Kuo, K.K. Chin, Dual material gate (DMG) Field Effect Transistor. IEEE Tran Electron. Devices. 46, 865 (1999)

A. Pal, Analytical study of dual material surrounding Gate MOSFET to suppress short-channel effects(SCEs). Eng. Sci. Technol. 17, 205 (2014)

Sentaurus Device User Guide, Synopsys, Inc., Mountain View, USA, 2022

A. Singh, C.K. Pandey, S. Chaudhury, and C.K.Sarkar, 2019. Effect of strain in silicon nanotube FET devices for low power applications. The European Physical Journal Applied Physics, vol. 85(2019), 10101

V. Pott, K.E. Moselund, D. Bouvet, L. De Michielis, A.M. Ionescu, Fabrication and characterization of gate-all-around silicon nanowires on bulk silicon. IEEE Trans. Nanotechnol. 7, 733 (2008)

S. Barraud,, B.P.V. Lapras, R. Coquand, C. Vizioz, J.M. Hartmann, Top-down fabrication and electrical characterization of Si and SiGe nanowires for advanced CMOS technologies. Semicond. Sci. Technol. 34, 074001 (2019)

Funding

No funding is available for this work.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Ethical Approval

Not Applicable.

Conflict of Interest

There is no conflict of interest for this work.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Jena, B., Bhol, K. & Nanda, U. Exploration of Linearity Analysis in Nanotube GAA MOSFET Through Simulation-Based Study Utilizing Multi-Material Gate Technique. Trans. Electr. Electron. Mater. (2024). https://doi.org/10.1007/s42341-024-00528-1

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42341-024-00528-1